在先进工艺上,台积电今年底量产3nm工艺,2025年则是量产2nm工艺,这一代会开始使用GAA晶体管,放弃现在的FinFET晶体管技术。

再往后呢?2nm之后是1.4nm工艺,Intel、台积电及三星这三大芯片厂商也在冲刺,其中三星首个宣布2027年量产1.4nm工艺,台积电没说时间点,预计也是在2027年左右。

1.4nm之后就是1nm工艺了,这个节点曾经被认为是摩尔定律的物理极限,是无法实现的,但是现在芯片厂商也已经在攻关中。

台积电已经启动了先导计划,传闻中的1nm晶圆厂将落户新竹科技园下属的桃园龙潭园区,这意味着台积电已经开始为1nm做规划了,毕竟工厂需要提前一两年建设。

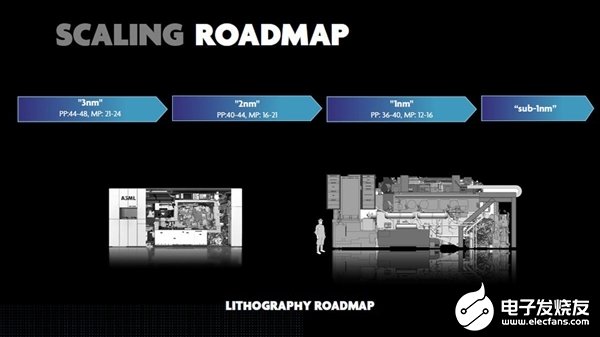

不过真正量产1nm还需要很长时间,其中关键的设备就是下一代EUV光刻机,要升级下一代的高NA(数值孔径)标准,从现在的0.33 NA提升到0.55 NA,更高的NA意味着更分辨率更高,是3nm之后的工艺必备的条件。

按照ASML的计划,下一代EUV光刻机的试验型号最快明年就开始出货,2025年后达到正式量产能力,售价将达到4亿美元以上。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电

+关注

关注

43文章

5284浏览量

164815 -

光刻机

+关注

关注

31文章

1121浏览量

46392 -

1nm

+关注

关注

0文章

15浏览量

3860

发布评论请先 登录

相关推荐

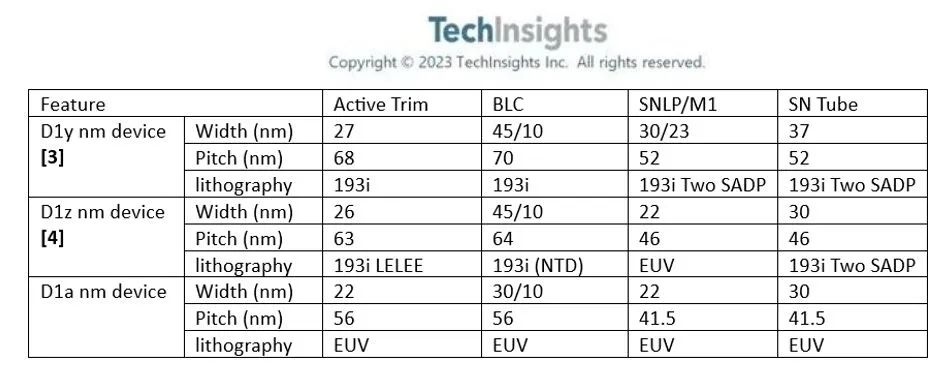

绕开EUV光刻,下一代纳米压印光刻技术从存储领域开始突围

电子发烧友网报道(文/李宁远)提及芯片制造技术,首先想到的自然是光刻机和光刻技术。众所周知在芯片行业,光刻是芯片制造过程中最重要、最繁琐、最具挑战也最昂贵的一项工艺步骤。在

英特尔突破技术壁垒:首台商用High NA EUV光刻机成功组装

英特尔的研发团队正致力于对这台先进的ASML TWINSCAN EXE:5000 High NA EUV光刻机进行细致的校准工作,以确保其能够顺利融入未来的生产线。

光刻机的发展历程及工艺流程

光刻机经历了5代产品发展,每次改进和创新都显著提升了光刻机所能实现的最小工艺节点。按照使用光源依次从g-line、i-line发展到KrF、ArF和EUV;按照工作原理依次从接触接近式

发表于 03-21 11:31

•727次阅读

ASML 首台新款 EUV 光刻机 Twinscan NXE:3800E 完成安装

EUV 光刻机持续更新升级,未来目标在 2025 年推出 NXE:4000F 机型。 上两代 NXE 系列机型 3400C 和 3600D 分别适合 7~5、5~3 纳米节点生产,德媒 ComputerBase 因此预测 38

光刻机结构及IC制造工艺工作原理

光刻机是微电子制造的关键设备,广泛应用于集成电路、平面显示器、LED、MEMS等领域。在集成电路制造中,光刻机被用于制造芯片上的电路图案。

发表于 01-29 09:37

•652次阅读

能耗成了EUV***的最大掣肘

制造的各道工序,不少晶圆厂在新建之际时,都要对该地区的电力输送进行大改。 极度耗电的EUV 光刻机 由于制造EUV光源的能源转换效率并不算高,所以哪怕7nm节点下,

日本的EUV***引进之路

水平。 美光的1γ节点 在今年五月,美光宣布将在日本引入EUV光刻机,用于开发下一代DRAM,基于最先进的1γ节点。此消息一出,美光也就成为第一个为日本引入EUV

EUV光刻DDR5内存狂飙 单条1TB不是梦

随着制程工艺的进步,DRAM内存芯片也面临着CPU/GPU一样的微缩难题,解决办法就是上EUV光刻机,但是设备实在太贵,现在还要榨干DUV工艺最后一滴,DDR5内存有望实现单条1TB。

什么是EUV***?

需要明确什么是EUV光刻机。它是一种采用极紫外线光源进行曝光的设备。与传统的ArF光刻机相比,EUV光刻机可以将曝光分辨率提高到7纳米以下的

发表于 05-22 12:48

•4079次阅读

台积电已启动1nm工艺先导计划 升级下一代EUV光刻机是关键

台积电已启动1nm工艺先导计划 升级下一代EUV光刻机是关键

评论