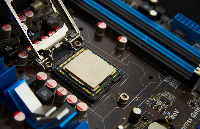

目前手机处理器的工艺制程是7nm,台积电也即将量产5nm芯片,未来还有2nm甚至1nm芯片的出现。台积电的研发负责人曾在谈论半导体工艺极限的问题时,认为到2050年,晶体管可达0.1nm的氢原子尺度。

当然工艺的提升因芯片、光刻机技术等方面因素受到影响。那么芯片最小能做到多少?三星电子预计在2022-2023年将量产3nm的硅基芯片,那么在3nm硅芯片之后就需要在新材料上得到捅破才能做更小的芯片了。

芯片制造最重要的设备就是光刻机,但光刻机采用的频率是有物理极限的,光的频率也不可能被要求做到无限高。另一个则是制造芯片的原材料硅,芯片内部的晶体管做的再小,也不可能比硅原子还小。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

462文章

53534浏览量

459106 -

光刻机

+关注

关注

31文章

1196浏览量

48733 -

2nm

+关注

关注

1文章

215浏览量

5096

发布评论请先 登录

相关推荐

热点推荐

纳米世界的舞者:压电陶瓷如何实现精密定位与扫描?

陶瓷定位技术,则以其天生的纳米基因,成为了探索微观世界不可或缺的“舞者”。 一、挑战极限:为何需要纳米级运动? · 光学显微镜的对焦与像差校正 :需要移动透镜组实现纳米步进的精确对焦。

CYBT-343026-01 芯片的电源电压范围是多少?

我想知道 CYBT-343026-01 芯片的电源电压范围是多少。

它在数据表中提到了2.3V-3.6V,但也提到电源电压取决于 “模块中包含的SPI串行闪存的最小和最大工作电压”。

我找不到所含的 SPI 串行闪存的详细信息。

你能帮忙解决这个问题吗?

发表于 07-03 08:12

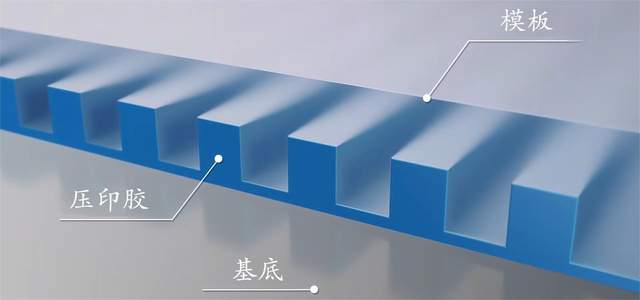

压电纳米定位系统如何重塑纳米压印精度边界

在半导体芯片制造、光学元件加工以及生物医疗器件研发等领域,微纳结构的加工精度正朝着原子级精度不断迈进。传统光刻技术由于受到波长衍射极限的制约,当加工尺度进入10nm以下时,不仅面临着成本急剧上升

扫描电镜:打开微观世界的“超维相机”,科学家如何用它破解纳米谜题?

传统显微镜受限于可见光波长,放大极限止步于200纳米。而扫描电镜利用高能电子束作为"探针",通过电磁透镜操控电子轨迹,突破衍射极限,分辨率可达1纳米以下。

全球芯片产业进入2纳米竞争阶段:台积电率先实现量产!

随着科技的不断进步,全球芯片产业正在进入一个全新的竞争阶段,2纳米制程技术的研发和量产成为了各大芯片制造商的主要目标。近期,台积电、三星、英特尔以及日本的Rapidus等公司纷纷加快了在2纳米

6G新时代:碳纳米管射频器件开创未来

随着集成电路的不断缩小,传统硅基材料逐渐接近性能极限。碳纳米管,作为一种低维材料,凭借其独特的结构和优异的性能,在射频领域展现出巨大的应用潜力。 碳纳米管的种类和优势: 半导体性碳纳米

Rapidus携手博通推进2纳米芯片量产

近日,据日媒报道,日本半导体新兴企业Rapidus正与全球知名芯片制造商博通(Broadcom)展开合作,共同致力于2纳米尖端芯片的量产。Rapidus计划在今年6月向博通提供试产芯片

芯片极限能力、封装成品及系统级测试

本文介绍了芯片极限能力、封装成品及系统级测试。 本文将介绍芯片极限能力、封装成品及系统级测试,分述如下: 极限能力测试 封装成品测试(Fin

7纳米工艺面临的各种挑战与解决方案

本文介绍了7纳米工艺面临的各种挑战与解决方案。 一、什么是7纳米工艺? 在谈论7纳米工艺之前,我们先了解一下“纳米”是什么意思。纳米(nm)

ADS1115这块芯片的设计精度是多少?

想问下,ADS1115这块芯片的设计精度是多少?

具体在手册的哪一页?

还有ADS1115的I2C的时序图,有没有大神能为我解释下?

另外就是,如果用ADS1115做一个电压表,那么有哪些环节会对这个电压表的精度产生影响呢?

谢谢各位。

发表于 12-17 07:02

芯片的极限是多少纳米

芯片的极限是多少纳米

评论