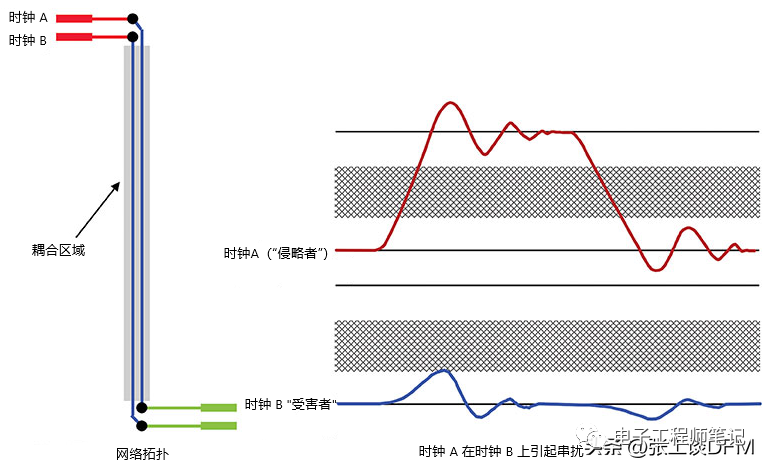

在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。

2022-08-22 10:45:08 4444

4444

在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。

2022-08-29 09:38:57 2560

2560

因此了解串扰问 题产生的机理并掌握解决串扰的设计方法,对于工程师来说是相当重要的,如果处理不好可能会严重影响整个电路的效果。

2022-09-28 09:41:25 2687

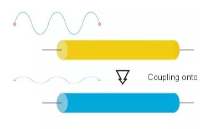

2687 先来说一下什么是串扰,串扰就是PCB上两条走线,在互不接触的情况下,一方干扰另一方,或者相互干扰。主要表现是波形有异常杂波,影响信号完整性(Signal integrity, SI)等等。一般情况下可以分为容性串扰和感性串扰两种。

2022-11-10 17:00:44 2650

2650

必须确保测量精度不受PCB或测试装置的杂散电容和电感影响。您可以通过使用低电容探头、在PCB上使用短连接线,并且避免在信号走线下大面积铺地来尽可能规避这些问题。

2023-04-17 09:16:05 739

739 01 . 什么是串扰? 串扰 是 PCB 的走线之间产生的不需要的噪声 (电磁耦合)。 串扰是 PCB 可能遇到的最隐蔽和最难解决的问题之一。最难搞的是,串扰一般都会发生在项目的最后阶段,而且

2023-05-23 09:25:59 8732

8732

先来说一下什么是串扰,串扰就是PCB上两条走线,在互不接触的情况下,一方干扰另一方,或者相互干扰。

2023-09-11 14:18:42 2335

2335

不同频率的模拟部分共地时,只有一个频率的返回信号可以非常接近于以不同频率运行的电路传播,从而引起串扰。最后,为了降低感应信号的强度,应该在尽可能短的距离内布线模拟信号线。虽然将分线放置在地平面中以便

2019-05-15 09:13:05

设计1、PCB中的电磁干扰2、PCB的一般设计原则3、旁路与去耦4、PCB中的抗串扰设计5、PCB接地 回复下载PPT课件!

2015-08-19 22:03:16

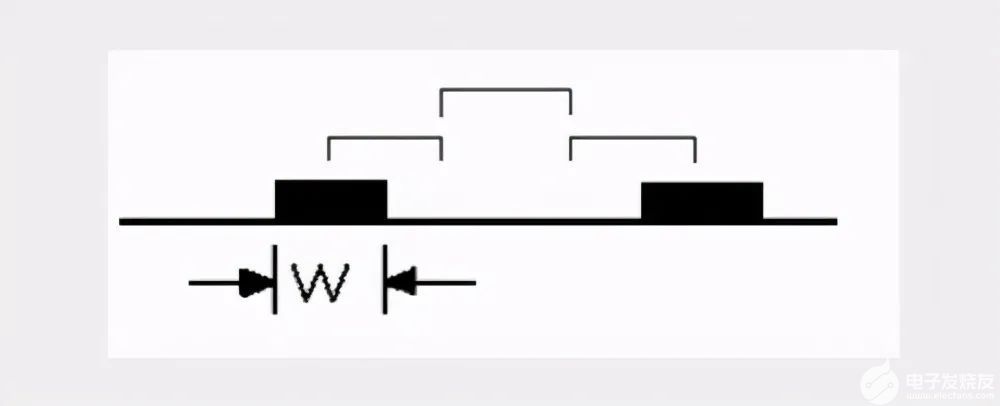

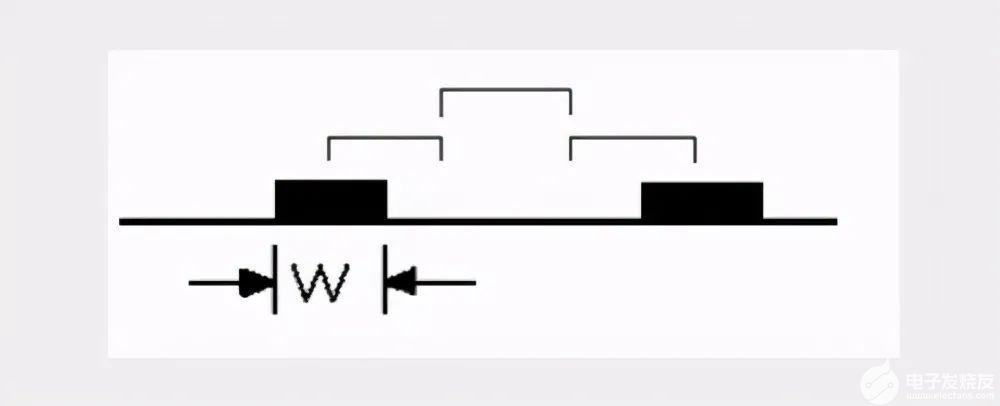

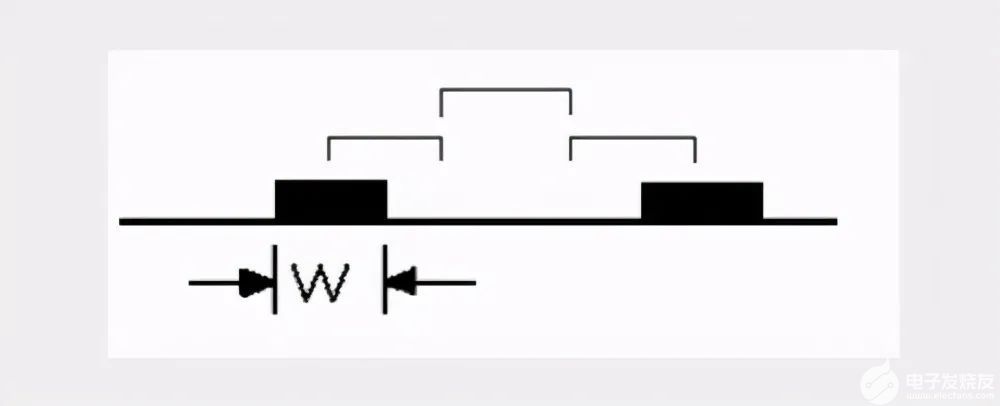

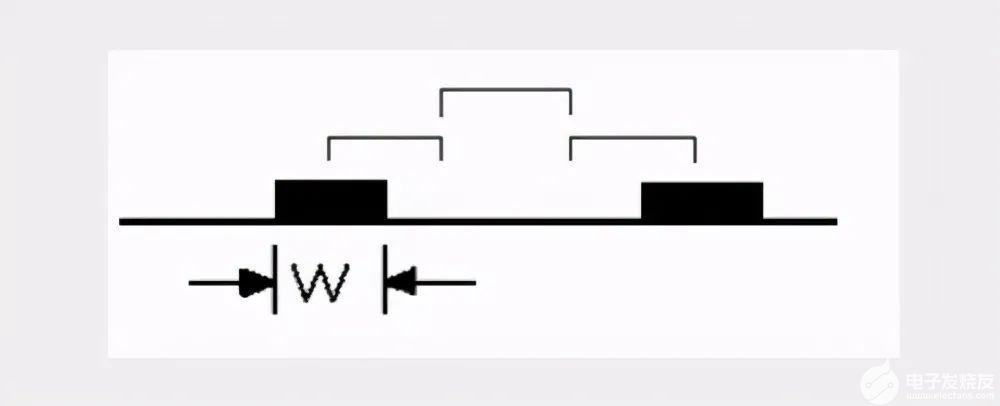

?对串扰有一个量化的概念将会让我们的设计更加有把握。1.3W规则在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如(图1

2014-10-21 09:53:31

同组信号的串扰叠加在上升/下降沿上,影响较小。不同组信号的串扰可能造成信号的振铃等,影响较大。6.时钟信号对串扰较为敏感,高速串行信号的时钟通常合并在信号中一起发送,串扰引起的抖动对接收的信号

2014-10-21 09:52:58

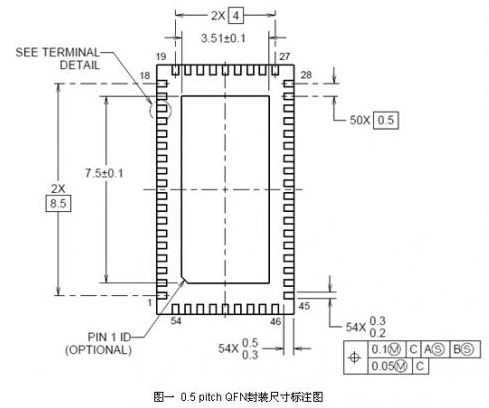

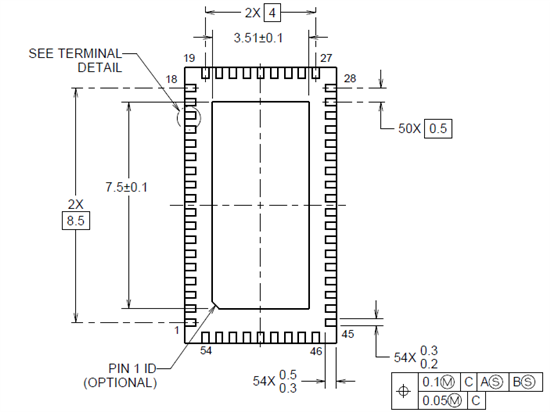

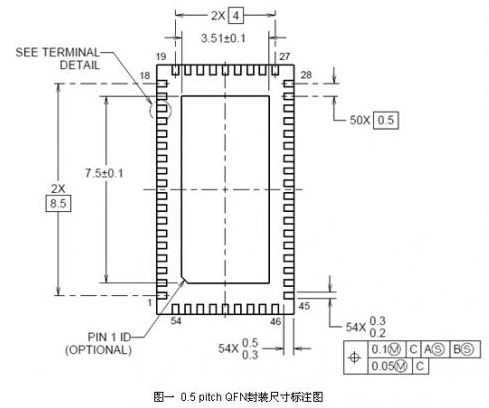

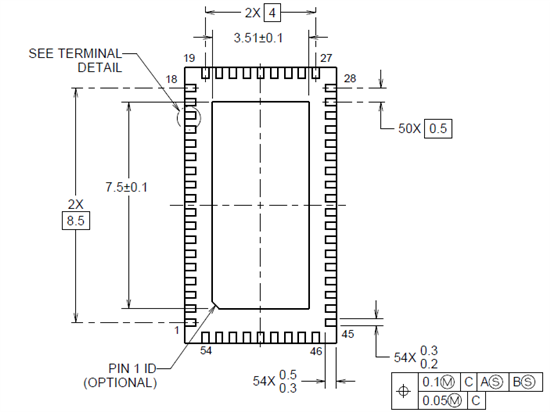

间隙的高度以便分离。此外,由于芯片焊盘直接与PCB连接,使得QFN封装具有极好的散热性。由于QFN封装的有效和致密的设计,还会降低电子寄生效应。表1所列是典型的可靠性数据。表1 可靠性 为了达到峰值性能

2010-07-20 20:08:10

一、下载STM32元件库1、下载完成2、找到原理图二、建立最小系统元件库1、新建元件工程并改名2、新建PCB元件库和SCH元件库二、芯片PCB的封装1、打开PCB元件,选择工具打开如下界面2

2021-11-25 09:05:08

芯片封装测试流程详解ppt•按封装外型可分为:SOT 、QFN 、SOIC、TSSOP、QFP、BGA、CSP等;• 决定封装形式的两个关键因素:Ø封装效率。芯片面积/封装面积,尽量接近1:1

2012-01-13 11:46:32

在接插件和封装处。1.使用介电常熟小的材料可减少串扰。2.互连线尽可能地短。轨道塌陷当芯片的输出反转或者内核门反转时,会在电源和地之间的阻抗上产生一个压降。这个压降就意味着供给芯片的电压变小了。高性能处理器

2017-11-27 09:02:56

为什么低噪声放大器的第一级要尽可能的放大?

2023-11-21 08:01:12

方法之一。负载点转换器是一种电源DC-DC转换器,放置在尽可能靠近负载的位置,以接近电源。因POL转换器受益的应用包括高性能CPU、SoC和FPGA——它们对功率级的要求都越来越高。例如,在汽车应用中

2021-12-01 09:38:22

为什么在MCU中要尽可能少用全局变量

2023-10-11 07:07:12

为什么在MCU中要尽可能少用浮点数运算

2023-10-09 08:06:12

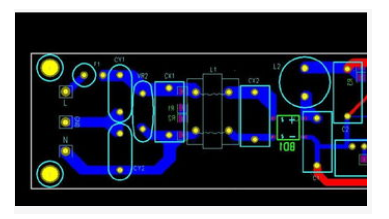

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出

2019-07-30 08:03:48

相互作用时就会产生。在数字电路系统中,串扰现象相当普遍,串扰可以发生在芯片内核、芯片的封装、PCB板上、接插件上、以及连接线缆上,只要有临近的铜互连链路,就存在信号间的电磁场相互作用,从而产生串扰现象

2016-10-10 18:00:41

、尽量避免两层信号层直接相邻,以减少串扰。4、主电源尽可能与其对应地相邻,构成平面电容,降低电源平面阻抗。5、兼顾层压结构对称,利于制版生产时的翘曲控制。以上为层叠设计的常规原则,在实际开展层叠设计时

2017-03-22 14:34:08

哪里可以买到尽可能高频率的无线能量发射接收模块。哪里可以买到尽可能高频率的无线能量发射接收模块。哪里可以买到尽可能高频率的无线能量发射接收模块。哪里可以买到尽可能高频率的无线能量发射接收模块。哪里

2015-12-05 22:48:41

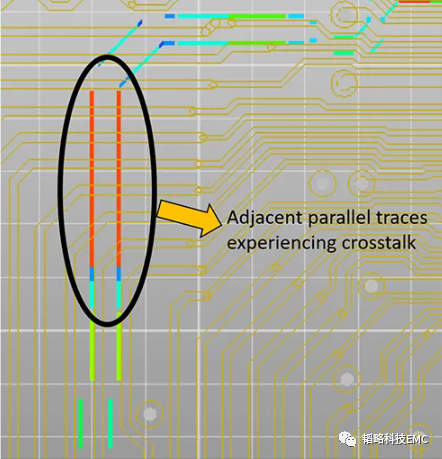

的影响一般都是负面的。为减少串扰,最基本的就是让干扰源网络与***扰网络之间的耦合越小越好。在高密度复杂PCB设计中完全避免串扰是不可能的,但在系统设计中设计者应该在考虑不影响系统其它性能的情况下,选择适当

2018-09-11 15:07:52

问题:如何确保尽可能高效地测试开关稳压器?

2019-03-01 08:50:13

方法可以在制定PCB布线规则和叠层时综合考虑,在PCB设计初期避免由小间距QFN封装带来的串扰风险。TI公司的产品DS125BR820、DS80PCI810等芯片都采用了体积小并且利于散热的QFN封装

2018-09-11 11:50:13

随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于

2021-03-01 11:45:56

我需要让 ST25R3916 读取尽可能节能。我正在搜索文档,但我只看到这个稳压器 (0x2C)。是否有任何选项可以更改 NFC 的场功率以使读取尽可能节能?NFC 标签将始终位于固定范围内的固定位置。重要提示:我们不是在谈论检测卡——因为电容检测已经足够好了,但只是在读取卡时

2023-02-02 07:43:34

、电路板的设计、串扰的模式(反向还是前向)以及干扰线和***扰线两边的端接情况。下文提供的信息可帮助读者加深对串扰的认识和研究,从而减小串扰对设计的影响。 研究串扰的方法 为了尽可能减小PCB设计中的串

2018-11-27 10:00:09

,但是连接后电压不会下降到1.9V以下。JRK直接从电位器工作。我想在PSoC和控制器之间放置一个运放来缓冲这个,但是我想尽可能少的损失,尽可能地保持输出的精确性。我需要一个DIL包,这样我就可以剥离

2019-10-08 12:43:05

在PCB电路设计中有很多知识技巧,之前我们讲过高速PCB如何布局,以及电路板设计最常用的软件等问题,本文我们讲一下关于怎么解决PCB设计中消除串扰的问题,快跟随小编一起赶紧学习下。 串扰是指在一根

2020-11-02 09:19:31

为什么低噪声放大器的第一级要尽可能的放大?

2018-08-24 07:15:03

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出

2022-11-21 06:14:06

可能出现在电路板、连接器、芯片封装以及线缆上。本文将剖析在高速PCB板设计中信号串扰的产生原因,以及抑制和改善的方法。

串扰的产生

串扰是指信号在传输通道

2018-08-28 11:58:32

Z方向的并行距离远大于水平方向的间距时,就要考虑高速信号差分过孔之间的串扰问题。顺便提一下,高速PCB设计的时候应该尽可能最小化过孔stub的长度,以减少对信号的影响。如下图所1示,靠近Bottom层

2018-09-04 14:48:28

方向的间距时,就要考虑高速信号差分过孔之间的串扰问题。顺便提一下,高速PCB设计的时候应该尽可能最小化过孔stub的长度,以减少对信号的影响。如下图所1示,靠近Bottom层走线这样Stub会比较短。或者

2020-08-04 10:16:49

高速PCB设计中的串扰分析与控制:物理分析与验证对于确保复杂、高速PCB板级和系统级设计的成功起到越来越关键的作用。本文将介绍在信号完整性分析中抑制和改善信号串扰的

2009-06-14 10:02:38 0

0 高速PCB 串扰分析及其最小化乔 洪(西南交通大学 电气工程学院 四川 成都 610031)摘要:技术进步带来设计的挑战,在高速、高密度PCB 设计中,串扰问题日益突出。本文就串

2009-12-14 10:55:22 0

0 用于PCB 品质验证的时域串扰测量法作者:Tuomo Heikkil关键词:TDS8000B,串扰,采样示波器,PCB,通信信号分析仪摘要:本文讨论了串扰的组成,并展示了如何利用泰克的TDS8000

2010-02-07 16:40:00 37

37 基于AD8108的宽频带低串扰视频切换矩阵的设计

摘要:介绍了一种宽频带低串扰视频切换矩阵的设计.该矩阵采用美国ADI公司的AD8108作为宽频带视频切矩阵的信号切

2006-03-24 13:30:07 1090

1090

高速PCB串扰分析及其最小化

1.引言 随着电子产品功能的日益复杂和性能的提高,印刷电路

2009-03-20 13:55:35 888

888

分析了在超深亚微米阶段,串扰对高性能芯片设计的影响,介绍了消除串扰影响的方法。 关键词:串扰,布线,关键路径,

2009-05-05 20:59:16 1434

1434

QFN焊点的检测与返修

(1)焊点的检测

由于QFN的焊点是在封装体的下方,并且厚度较薄,X-ray对QFN焊点少锡和开路无法检测,只能依靠外部的焊点情况尽可能地

2010-03-04 15:08:19 2887

2887 对高速PCB中的微带线在多种不同情况下进行了有损传输的串扰仿真和分析, 通过有、无端接时改变线间距、线长和线宽等参数的仿真波形中近端串扰和远端串扰波形的直观变化和对比,

2011-11-21 16:53:02 0

0 串扰是不同传输线之间的能量耦合。当不同结构的电磁场相互作用时,就会发生串扰。在数字设计中,串扰现象是非常普遍的。串扰可能出现在芯片、PCB板、连接器、芯片封装和连接器

2012-05-28 09:09:38 2951

2951 PCB印制线间串扰的MATLAB分析理论分析给实际布线做参考依据

2015-12-08 10:05:46 0

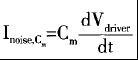

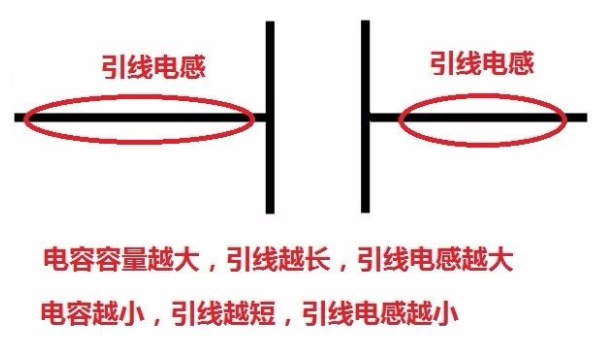

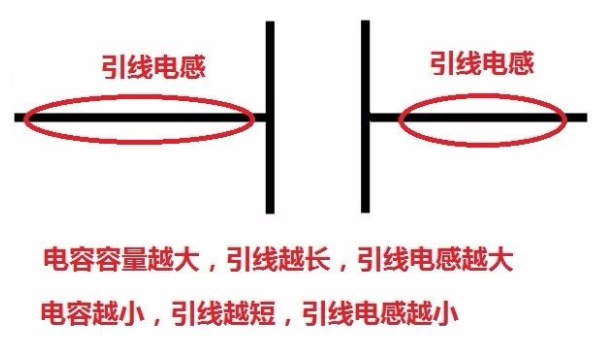

0 我们先来说说电容,都说大电容低频特性好,小电容高频特性好,那么根据容抗的大小与电容C及频率F成反比来说的话,是不是大电容不仅低频特性好,高频特性更好呢,因为频率越高,容量越大,容抗就越低,高频就是

2018-08-28 09:31:02 13488

13488

信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰在高速PCB设计中的影响显著增加。串扰问题是客观存在,但超过一定的界限可能引起电路的误触发,导致系统无法正常工作。设计者必须了解串扰产生的机理,并且在设计中应用恰当的方法,使串扰产生的负面影响最小化。

2019-05-29 14:09:48 1271

1271

检视器,您可以准确地找到耦合度最高的网络区域所在的位置。此外,将网络导出到 LineSim,以编辑耦合部分并消除串扰问题。然后,确定需要对 Layout 做出的更改。

请注意:在您放映视频时,如没有显示中文字幕,请单击 “CC” 按钮并点选 “Mandarin(Simplified)” 选项。

2019-05-16 06:30:00 4186

4186

PCB布局上的串扰可能是灾难性的。如果不纠正,串扰可能会导致您的成品板完全无法工作,或者可能会受到间歇性问题的困扰。让我们来看看串扰是什么以及如何减少PCB设计中的串扰。

2019-07-25 11:23:58 3989

3989 在实际PCB设计中,3W规则并不能完全满足避免串扰的要求。

2019-08-19 15:10:14 8071

8071 在PCB设计中,QFN封装的器件通常使用微带线从TOP或者BOTTOM层扇出。对于小间距的QFN封装,需要在扇出区域注意微带线之间的距离以及并行走线的长度。

2019-10-04 17:09:00 1710

1710

PCB串扰问题可以很容易地定位和固定使用HyperLynx®垫专业或垫+标准。从PCB布局出口你的设计之后,在批处理模式运行模拟和/或交互模式来识别潜在的串扰问题。沃克BoardSim耦合地区使您能

2019-10-16 07:10:00 3787

3787 随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB 走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于

2020-10-19 10:42:00 0

0 高速PCB设计中,信号之间由于电磁场的相互耦合而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可能引发电路误动作从而导致系统无法正常工作,解决PCB串扰问题可以从以下几个方面考虑。

2020-07-19 09:52:05 2820

2820 PCB设计师之所以关心串扰这一现象,是因为串扰可能造成以下性能方面的问题:噪音电平升高;有害尖峰突波;数据边沿抖动;意外的讯号反射。

2020-09-09 13:44:30 2223

2223 在UPS 的实际应用中,温度对电池的自然老化过程有很大影响。详细的实验数据表明温度每上升 5℃,电池寿命就下降 10%,所以 UPS 蓄电池的设计应让电池保持尽可能的温度。

2020-08-09 15:22:00 1705

1705 是什么,以及如何在高速设计中分析,模拟和消除串扰。 什么是串扰? 串扰是由走线之间有害的电磁耦合引起的干扰。具有移动电荷的导体将始终产生一些电磁场。增大信号速度会增加其在相邻信号上引起耦合的可能性。让我们仔细看看电磁

2020-09-16 22:59:02 3130

3130 当电路板上出现串扰时,电路板可能无法正常工作,并且在那里也可能会丢失重要信息。为了避免这种情况, PCB 设计人员的最大利益在于找到消除其设计中潜在串扰的方法。让我们谈谈串扰和一些不同的设计技术

2020-09-19 15:47:46 3330

3330 您可能会发现布局和布线会因攻击者的踪迹而产生强烈的串扰。 那么,在设计中哪里可以找到串扰,以及在PCB中识别出不良走线的最简单方法是什么?您可以使用全波场求解器,但是可以在PCB设计软件中使用更简单的分析功能来识别和抑

2021-01-13 13:25:55 3420

3420 文章——串扰溯源。 提到串扰,防不胜防,令人烦恼。不考虑串扰,仿真波形似乎一切正常,考虑了串扰,信号质量可能就让人不忍直视了,于是就出现了开头那惊悚的一幕。下面就来说说串扰是怎么产生的。 所谓串扰,是指有害信号从一

2021-03-29 10:26:08 4155

4155 我无法找到解释为什么人们想要沿着铜迹线(或PCB上的任何地方)放置尽可能多的通孔(~50),这些通孔传输高频RF(100 MHz至GHz)信号。 在我的情况下,我的电路板两侧有两个地平面(倾倒)。我

2021-02-23 11:44:39 5745

5745 适用于DA4580蓝牙芯片的QFN40芯片尺寸及推荐PCB封装资料免费下载

2021-02-02 08:00:00 0

0 电子发烧友网为你提供PCB小间距QFN封装引入串扰的抑制方法资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-31 08:52:17 11

11 电子发烧友网为你提供到底什么是串扰?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:51:47 14

14 本指南旨在说明如何尽可能地加强Linux的安全性和隐私性,并且不限于任何特定的指南。 免责声明:如果您不确定自己在做什么,请不要尝试在本文中使用任何内容。 本指南仅关注安全性和隐私性,而不关注性能

2021-04-25 14:58:24 3044

3044 电子发烧友网为你提供PCB设计的串扰问题解决资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-28 08:42:04 8

8 机械振动测试讲解PPT课件下载

2021-07-07 09:57:15 0

0 单片机基础知识讲解PPT课件下载

2021-07-29 09:43:11 230

230 IC封装工艺讲解PPT课件下载

2021-08-05 17:17:06 165

165 PCB封装设计步骤PPT课件下载

2021-09-02 16:09:44 0

0 pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路

2021-11-10 09:42:22 3436

3436

串扰的危害:

降低板内信号完整性

时钟或者信号延迟

产生过冲电压和突变电流

造成芯片逻辑功能紊乱

2022-07-07 10:35:01 1289

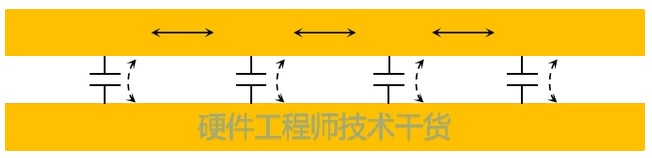

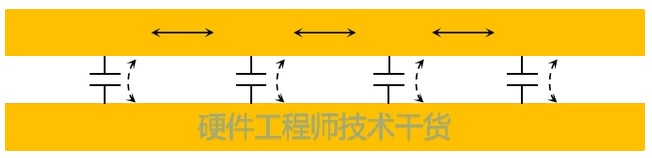

1289 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

2022-08-15 09:32:06 11704

11704 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。串扰也可以理解为感应噪声。

2022-09-14 09:49:55 3781

3781

小间距QFN封装PCB设计串扰抑制分析

2022-11-04 09:51:54 2

2 在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

2022-11-07 11:20:35 2558

2558 在测量运算放大器输入电容时,应关注哪些方面? 必须确保测量精度不受PCB或测试装置的杂散电容和电感影响。您可以通过使用低电容探头、在PCB上使用短连接线,并且避免在信号走线下大面积铺地来尽可能规避

2023-04-11 03:45:02 1382

1382

串扰是 PCB 的走线之间产生的不需要的噪声 (电磁耦合)。

2023-05-22 09:54:24 5605

5605

串扰是 PCB 的走线之间产生的不需要的噪声(电磁耦合)。

2023-07-20 09:57:08 3937

3937

空间中耦合的电磁场可以提取为无数耦合电容和耦合电感的集合,其中由耦合电容产生的串扰信号在受害网络上可以分成前向串扰和反向串扰Sc,这个两个信号极性相同;由耦合电感产生的串扰信号也分成前向串扰和反向串扰SL,这两个信号极性相反。

2023-08-21 14:26:46 700

700 pcb上的高速信号需要仿真串扰吗 在数字电子产品中,高速信号被广泛应用于芯片内部和芯片间的数据传输。这些信号通常具有高带宽,并且需要在特定的时间内准确地传输数据。然而,在高速信号传输的过程中,会出

2023-09-05 15:42:31 1458

1458 这种影响信号完整性的问题叫做串扰,在电路计中普遍存在,有可能出现在芯片、PCB板、连接器、芯片封装和连接器电缆等器件上。如果串扰超过一定的限度就会引起电路的误触发,导致系统无法正常工作。

2023-10-07 09:46:19 1446

1446 电子发烧友网站提供《如何在STM32F10xxx上得到最佳的ADC精度.pdf》资料免费下载

2023-10-07 14:46:02 21

21 一站式PCBA智造厂家今天为大家讲讲pcb设计布线解决信号串扰的方法有哪些?PCB设计布线解决信号串扰的方法。信号之间由于电磁场的相互而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可能

2023-10-19 09:51:44 2514

2514 如何在不受电线等的影响下尽可能准确地测量如mΩ数量级的电阻值呢? 引言: 电阻测量是电路分析和电子工程中非常重要的技术。然而,在测量低阻值时,电线、接触电阻、温度等因素可能对结果产生较大的影响。因此

2023-11-17 14:48:59 1209

1209 如何减少PCB板内的串扰

2023-11-24 17:13:43 1382

1382

串扰是芯片后端设计中非常普遍的现象,它会造成逻辑信号的预期之外的变化。消除串扰的影响是后端的一个重要课题。

2023-12-06 15:38:19 2340

2340 空间中耦合的电磁场可以提取为无数耦合电容和耦合电感的集合,其中由耦合电容产生的串扰信号在受害网络上可以分成前向串扰和反向串扰Sc,这个两个信号极性相同;由耦合电感产生的串扰信号也分成前向串扰和反向串扰SL,这两个信号极性相反。

2023-12-28 16:14:19 718

718

1.高精度切割:QFN封装要求芯片的尺寸和形状误差要尽可能小,因此对国产双轴半自动划片机的切割精度提出了高要求。高精度的切割能够提高封装的良品率和稳定性。2.快速和稳定:QFN封装生产需要快速、稳定

2024-01-15 17:11:08 1069

1069

在PCB设计过程中,串扰(Crosstalk)是一个需要重点关注的问题,因为它会导致信号质量下降,甚至可能导致数据丢失。本文将详细介绍PCB中的串扰机制。 耦合 耦合是指两条信号线之间的磁场和电场

2024-01-17 14:33:20 1137

1137

一些方法尽量降低串扰的影响。那么减少串扰的方法有哪些呢? 检查靠近 I/O 网络的关键网络 检查与I/O线相关的关键网络的布线非常重要,因为这些线容易产生噪声,这些噪声可能会通过它们离开或进入电路板并与PCB连接,从而耦合到电路板内部或外部的世界,以及其他系统

2024-01-17 15:02:12 3261

3261

PCB产生串扰的原因及解决方法 PCB(印刷电路板)是电子产品中非常重要的组成部分,它连接着各种电子元件,并提供电气连接和机械支撑。在 PCB 设计和制造过程中,串扰是一个常见的问题,它可能

2024-01-18 11:21:55 3085

3085 在PCB设计中,如何避免串扰? 在PCB设计中,避免串扰是至关重要的,因为串扰可能导致信号失真、噪声干扰及功能故障等问题。 一、了解串扰及其原因 在开始讨论避免串扰的方法之前,我们首先需要

2024-02-02 15:40:30 2902

2902 电子发烧友网站提供《HotRod™ QFN封装PCB附件.pdf》资料免费下载

2024-08-26 14:47:40 0

0

电子发烧友App

电子发烧友App

硬声App

硬声App

4444

4444

2560

2560

2650

2650

739

739 8732

8732

0

0 0

0 37

37 1090

1090

2887

2887 0

0 2951

2951 13488

13488

1271

1271

4186

4186

3989

3989 1710

1710

3787

3787 0

0 2820

2820 2223

2223 1705

1705 3130

3130 3330

3330 3420

3420 4155

4155 5745

5745 11

11 14

14 3044

3044 8

8 3436

3436

11704

11704 3781

3781

2558

2558 1382

1382

700

700 1458

1458 1446

1446 2514

2514 1209

1209 718

718

1069

1069

1137

1137

3261

3261

3085

3085 2902

2902

评论