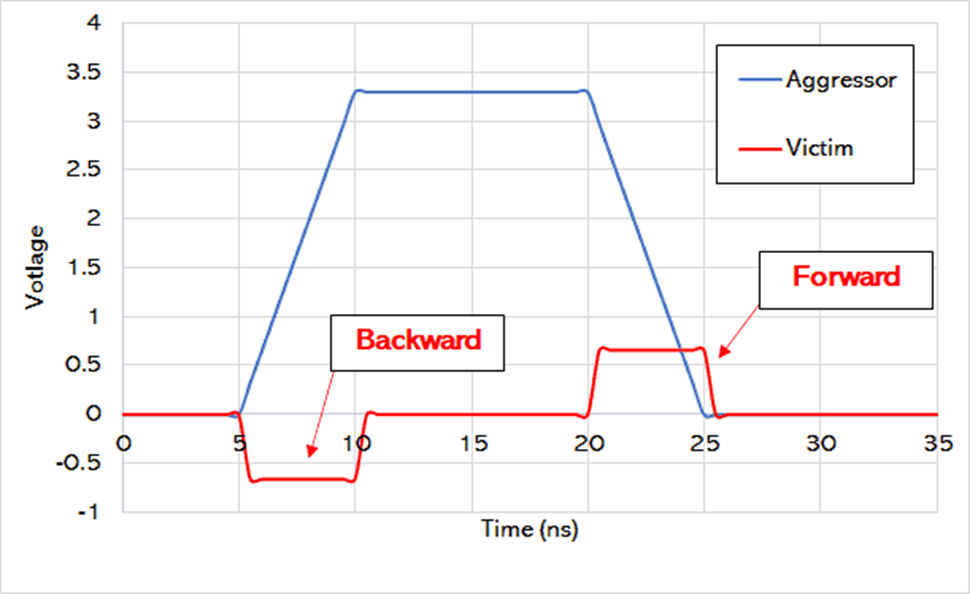

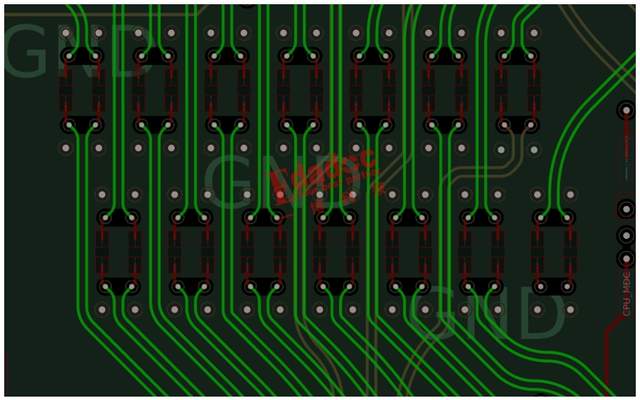

使用 HyperLynx® 可以轻松地查找并修复 PCB 串扰问题。从 PCB Layout 导出设计后,以批量模式和/或交互模式运行仿真,从而确定潜在的串扰问题。利用 BoardSim 的耦合区检视器,您可以准确地找到耦合度最高的网络区域所在的位置。此外,将网络导出到 LineSim,以编辑耦合部分并消除串扰问题。然后,确定需要对 Layout 做出的更改。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4417文章

23967浏览量

426191 -

网络

+关注

关注

14文章

8336浏览量

95569

发布评论请先 登录

相关推荐

热点推荐

PCB别人包地你包地,但别人的隔离度比你好10dB不止

为什么在这个节点把看起来没意义的阻抗结果show出来了。那包地的串扰是多少呢?如下面这个3D模型。

那个,等等哈,总好像感觉这个包地的设计有什么不确定的设计因素。在原来不包地的基础上进行包地,有没发现

发表于 04-13 11:21

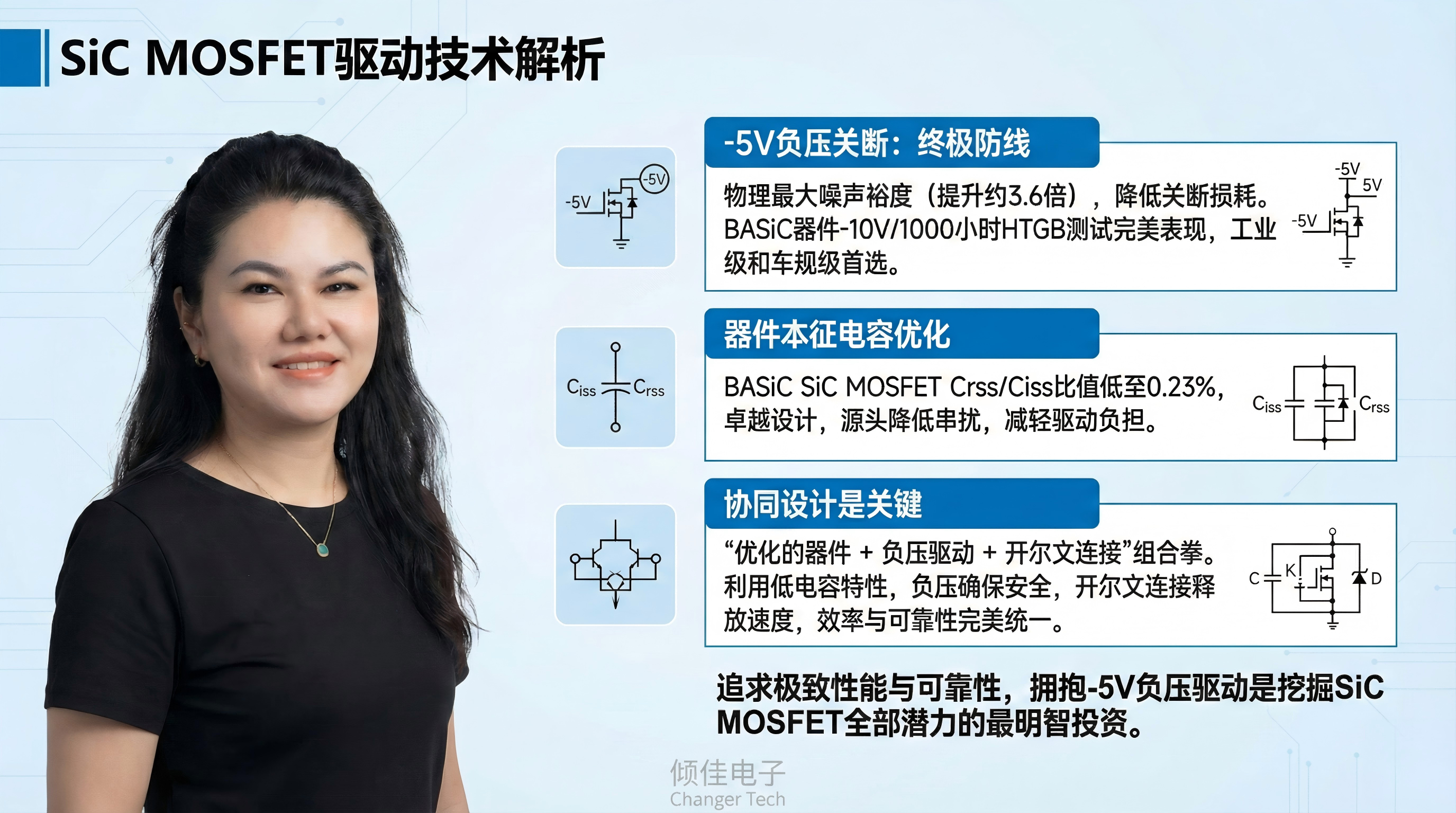

碳化硅MOSFET串扰抑制策略深度解析:负压关断与寄生电容分压的根本性优势

倾佳电子剖析SiC MOSFET串扰问题的物理机制,并对各类抑制措施进行详尽的比较分析。报告的核心论点在于:通过优化器件本征参数实现的寄生电容分压优化,以及采用-5V负压关断驱动,构成了解决串

西门子PCB仿真分析工具HyperLynx 2510版本的新增功能

HyperLynx 2510 新版在原理图分析、AMS、DRC、信号和电源完整性、高阶解算器和企业数据管理方面带来了一系列丰富的增强功能。这些更新提升了可用性、准确性和集成度,助力加快电子系统设计验证与优化。我们一起来了解其中的亮点。

EXCUSE ME,表层的AC耦合电容和PCB内层的高速线会有串扰?

和走线就是没串扰啊!但是串扰是没了,只不过让电容链路的信号质量承担了所有。

我们知道,电容结构本身的焊盘比较宽,那么阻抗如果参考L2层那么近的话,阻抗肯定是低的,就像上面这个模型一样

发表于 12-10 10:00

隔离地过孔要放哪里,才能最有效减少高速信号过孔串扰?

的方案。无论是高速过孔本身的优化,还是过孔间串扰的优化,其实都是很难通过经验甚至常规理论去解决,目前看起来,仿真绝对是更好的选择了哈!

问题:根据你们的经验,提出几种有效的改善高速信号过孔串扰

发表于 11-14 14:05

SiC MOSFET并联均流及串扰抑制驱动电路的研究

SiC MOSFET在并联应用中的安全性和稳定性提出了挑战当SiC MOSFET应用在桥式电路时高速开关动作引发的串扰问题严重影响了系统的可靠性.为了使SiC MOSFET在电路系统中稳定运行本文主要针对并联均流和串

发表于 08-18 15:36

•1次下载

高速AC耦合电容挨得很近,PCB串扰会不会很大……

觉得恐惧了?

恐惧?恐惧啥呢,那当然是大家都会担心对与对之间的串扰啊,在满足物质生活之后(能塞到PCB板之后),肯定要慢慢开始注重精神生活了!鉴于有不少的粉丝,包括公司设计部的同事都来问过Chris

发表于 07-22 16:56

harmony-utils之StrUtil,字符串工具类

harmony-utils之StrUtil,字符串工具类 harmony-utils 简介与说明 [harmony-utils] 一款功能丰富且极易上手的HarmonyOS工具库,借助众多实用

NEXT(Near-End Crosstalk,近端串扰)

一、什么是NEXT(近端串扰)? NEXT(Near-End Crosstalk,近端串扰)是指在线缆传输信号时,靠近发射端处,相邻线对之间因电磁干扰所产生的

OLI-P——分布式偏振串扰测量利器

在保偏光纤系统中,偏振串扰是导致性能劣化的核心因素之一。传统偏振检测手段仅能获得链路整体消光比,而分布式偏振串扰测量通过连续、高精度地捕捉整条光纤链路的偏振耦合分布,成为保障系统可靠性

使用HyperLynx工具确定和解决PCB串扰问题

使用HyperLynx工具确定和解决PCB串扰问题

评论