可编程逻辑

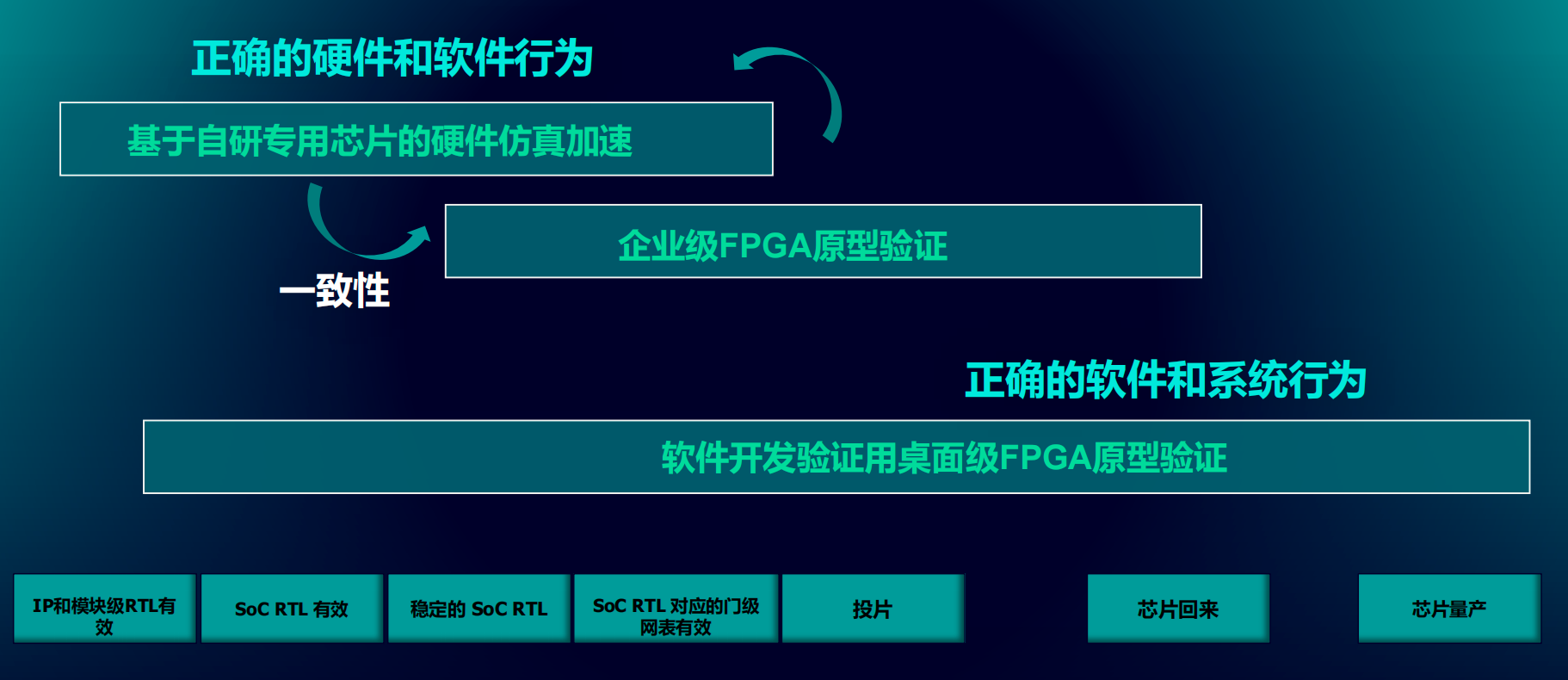

提供权威的PLD及可编程逻辑器件设计应用、Altera公司、Xilinx公司资讯和解决方案,包括HDL语言与源代码、FPGA开发板、EDA工具、FPGA、FPGA软件等领域。基于自研芯片+顶级AMD FPGA,西门子EDA发布“快而全”的Veloce CS

电子发烧友网报道(文/吴子鹏)在大型芯片设计过程中,验证被认为是整体流程中最复杂、最耗时的环节之一。有数据显示,目前功能验证约占整个芯片开发过程投入的60%-70%,是芯片项目能否...

2024-04-26 862

基于FPGA开发板的GPS模拟器数据采集验证

必须将GPS模拟器的数据通过FPGA开发板进行短时间的采集,至少能用于matlab算法上的捕获验证,这个采集时间至少要几ms。...

2024-04-25 129

国产FPGA应用专题--易灵思Efinity软件使用心得

做为FPGA的集成开发环境,不同的厂家其实大同小异。很多国产厂家,如安路,高云,会在软件上贴近Xilinx和Intel,以节省客户的软件使用成本。而国产厂商的易灵思的集成开发环境Efinity似乎并...

2024-04-23 353

易灵思RAM使用--Update4

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径 在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。 (1)如果文件放在工程目...

2024-04-23 352

基于FPGA的网络摄像头图像封装处理

上位机才能够在接收数据后正确显示图像。所以每帧图像的开始需要多传输8字节数据,一般规定每次传输一行数据,由于OV7725一行有640个像素,每个像素16位,而以太网每个时钟传输8位数据,...

2024-04-19 191

基于FPGA的内存128M flash芯片控制器设计方案

这款flash芯片的的存储是一个扇区4KB,一个扇区可以存256个字,一个字是8位,一个块是64KB,一共有256个块组成一个存储flash内存。...

2024-04-19 278

gtkwave界面每次都更新太麻烦?来个小技巧-v1

迄今为止,大家都在吐槽gtkwave debug每次弹窗都会覆盖上一次弹窗设置好的排序和参数。下面我们分享一个可以暂时规避该问题的方法,聊以慰藉久被摧残的心~~。 (1)添加debug ,无论手动或者自...

2024-04-15 564

易灵思Jtag_bridge_loader生成-v2

Efinity版本:2023.1及以前版本。 易灵思器通过jtag bridge烧写flash时需要自己生成一个jtage birdge文件。jtage bridge 工程的目的是为了打通JTAG与flash的连接。 (1)打开IPM (2)选择Memory Controllers --> J...

2024-04-15 534

AMD自适应计算加速平台之GTYP收发器误码率测试IBERT实验(6)

实验VIvado工程为“ibert_test”,目录中还有一个“ibert_ex”,是生成的测试工程。...

2024-04-12 1053

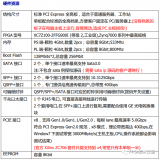

XC7K410T-FFG900外设之DDR3硬件设计方案分享

在数据速率带宽约束方面,DDR3运行速度受限于其与K7-410T FPGA互联的I/O Bank 管脚以及FPGA器件的速度等级。...

2024-04-12 932

Xilinx FPGA的约束设置基础

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。...

2024-04-26 25

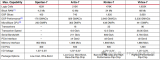

中国FPGA市场竞争格局分析

AMD(Xilinx)FPGA相关产品矩阵主要包括:四大 FPGA产品系列(VIRTEX、KINTEX、ARTIX、SPARTAN),以及集成度更高的两大自适应 SoC(Adaptive SoC)系列(ZYNQ、VERSAL)。...

2024-04-26 46

基于Verilog HDL的FPGA图像滤波处理仿真实现

注意这里的A是double类型的,直接进行imshow会全白,要转化到0-1:A=A./255,或者把double类型转化为整形。...

2024-04-26 28

基于FPGA的光纤通信加密系统

FPGA 设计加密算法具有安全性高,加密速度快,开发周期短,开发成本较低, 可重配,可靠性高以及移植性好等优点。 系统链路部分采用 Aurora 协议,该协议是一款轻量级的光纤链路协议,具有...

2024-04-26 36

Zynq-7000为何不是FPGA?

Zynq-7000可扩展处理平台是采用赛灵思新一代FPGA(Artix-7与Kintex-7FPGA)所采用的同一28nm可编程技术的最新产品系列。...

2024-04-26 31

基于FPGA的内部LVDS接收器设计

LVDS是一种低压低功耗的高速串行差分数据传输标准,在高速数据互联和数据通信领域得到广泛的应用,主流的FPGA器件都集成了高速的LVDS收发器。...

2024-04-26 39

FPGA的时钟电路结构原理

FPGA 中包含一些全局时钟资源。以AMD公司近年的主流FPGA为例,这些时钟资源由CMT(时钟管理器)产生,包括DCM、PLL和MMCM等。...

2024-04-25 43

AMD FPGA中MicroBlaze的固化流程详解

AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,上电后FPGA会以Master SPI方式尝试从FLASH加载配置文件,其与工程是否含有...

2024-04-25 42

基于FPGA设计的BRAM内部结构

再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。...

2024-04-25 38

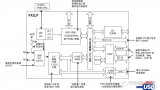

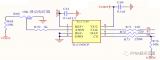

基于FPGA技术的USB2.0接口设计实践

本次设计我们选择一款开发设备,一块廉价的开发板,其中的USB芯片是Cypress的FX2LP系列中的CY7C68013A代,详细的介绍大家可以去Cypress的官网查询。下面简述一下设计思路。...

2024-04-25 38

FPGA技术的五大优势

各行各业纷纷采用FPGA芯片是源于FPGA融合了ASIC和基于处理器的系统的最大优势。 FPGA能够提供硬件定时的速度和稳定性,且无需类似自定制ASIC设计的巨额前期费用的大规模投入。...

2024-04-23 53

基于FPGA VHDL的ASK调制与解调

ASK即“幅移键控”又称为“振幅键控”,也有称为“开关键控”(通断键控)的,所以又记作OOK信号。ASK是一种相对简单的调制方式。...

2024-04-22 77

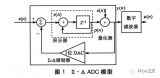

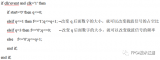

基于FPGA的数字电压表(AD)设计

TLC549是一个8位的串行模数转换器,A/D转换时间最大为17us,最大转换速率为4MHz。下图为TLC549的访问时序,从图中可以看出,TLC549的使用只需对外接输入输出时钟(I/O CLK)和芯片选择(/CS)、输...

2024-04-22 64

Xilinx 7系列FPGA功能特性介绍

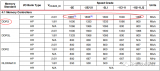

Xilinx7系列FPGA由四个FPGA系列组成,可满足一系列系统需求,从低成本、小尺寸、成本敏感的大容量应用到最苛刻的高性能应用的超高端连接带宽、逻辑容量和信号处理能力。...

2024-04-22 81

Xilinx FPGA BGA设计:NSMD和SMD焊盘的区别

Xilinx建议使用非阻焊定义的(NSMD)铜材BGA焊盘,以实现最佳板设计。NSMD焊盘是不被任何焊料掩模覆盖的焊盘,而阻焊定义的(SMD)焊盘中有少量阻焊层盖住焊盘平台。...

2024-04-19 98

FPGA通过AXI总线读写DDR3实现方式

AXI总线由一些核心组成,包括AXI主处理器接口(AXI4)、AXI处理器到协处理器接口(AXI4-Lite)、AXI主外设接口(AXI4)、AXI外设到主处理器接口(AXI4-Lite)等。...

2024-04-18 99

基于FPGA的多通道高速信号采集与处理平台设计方案

以核心处理板为核心,由信号源产生的待处理模拟信号通过同轴线缆连接到核心处理板的信号接口,同时,连接同步时钟等其他相关信号到核心处理板。...

2024-04-17 73

利用ISE与Matlab创建并仿真FPGA设计中的ROM IP核

一般都是先创建MIF文件,将图像中的像素信息用一个ROM储存起来,然后调用ROM里面的地址进行处理,相当于制作了一个ROM查找表。...

2024-04-16 70

CAM在FPGA上的最优化实现方案

我们都知道RAM是根据地址查找对应的数据,而对于CAM,则恰好相反,是已知数据查找其对应的地址。像在网络报文处理里,根据报文的五元组的一些信息去查询其所属的规则地址,随后通过该地...

2024-04-15 121

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |