本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此 HLS IP,并使用嵌入式 Vitis 应用控制此 HLS IP。

2025-06-13 09:50:11 1447

1447

Vivado IP 流程(Vitis Unified),在这篇 AMD Vitis HLS 系列 3 中,我们将介绍如何使用 Unified IDE 创建 HLS 组件。这里采用“自下而上”的流程,从 HLS

2025-07-02 10:55:32 1263

1263

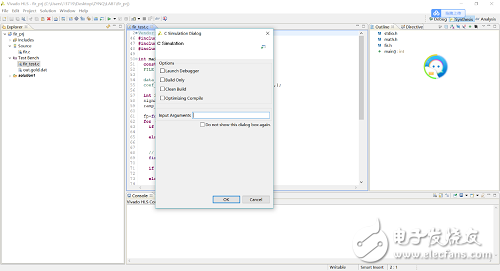

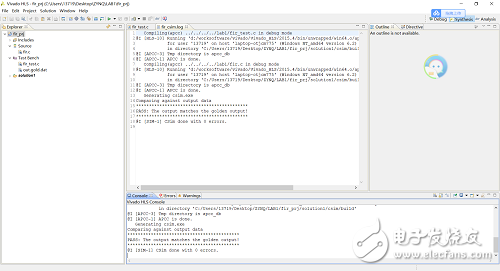

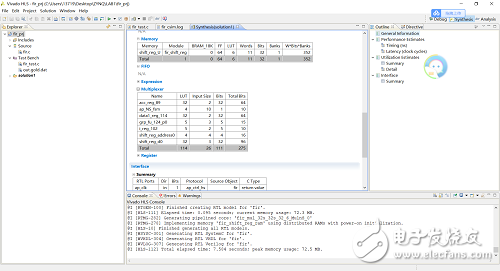

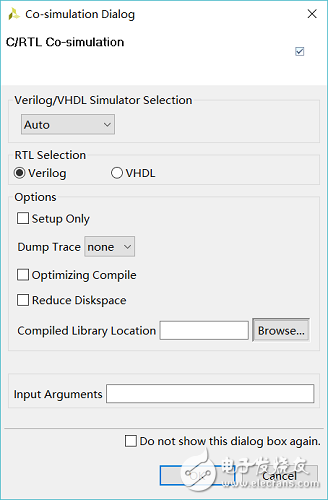

设计来满足各种约束 用不用的指令来探索多个HLS解决方案 2.实验内容 实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench

2020-12-21 16:27:21 4357

4357 用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。 本项目所需应用与工具:赛灵思HLS、Plunify Cloud 以及

2020-12-20 11:46:46 2389

2389

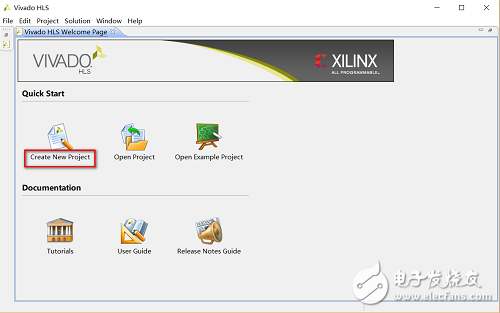

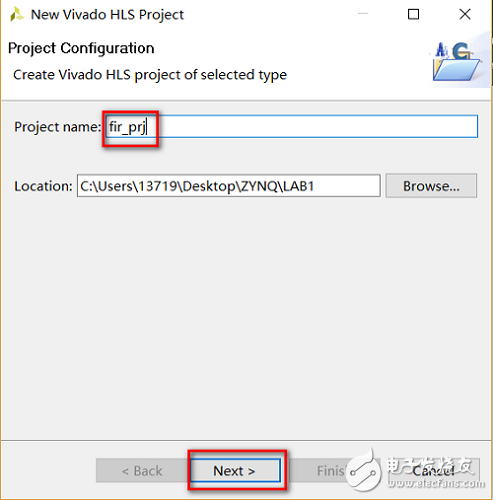

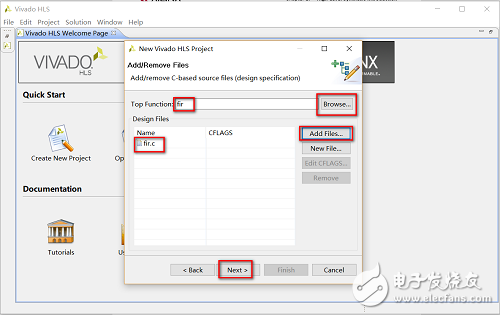

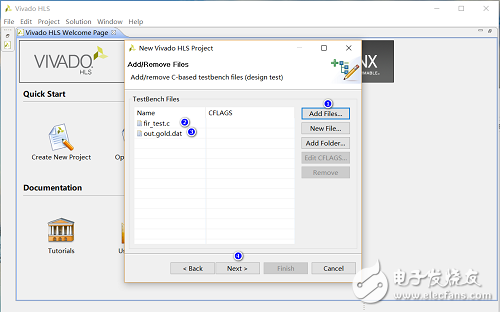

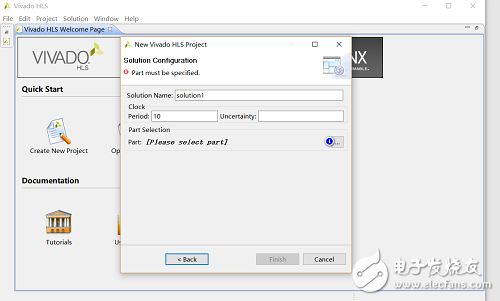

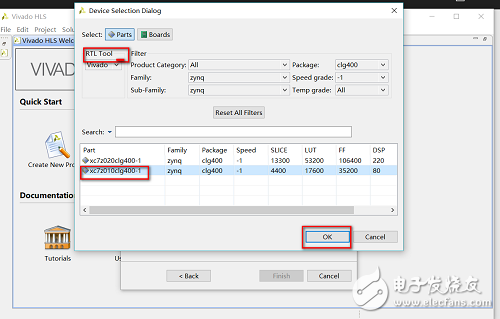

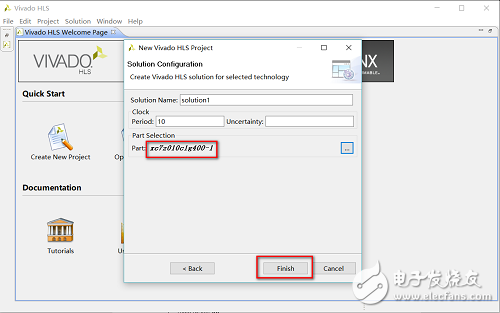

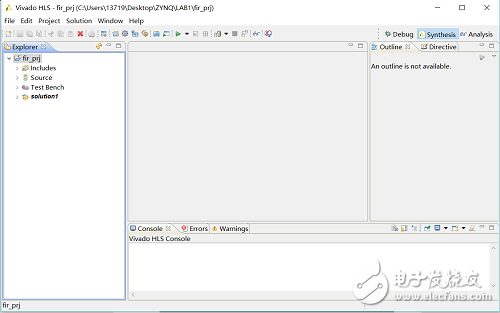

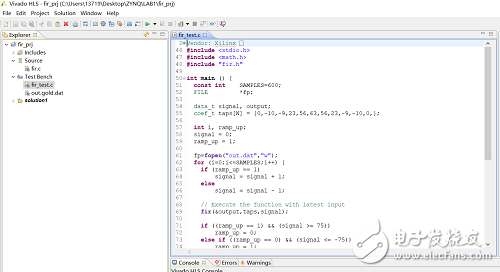

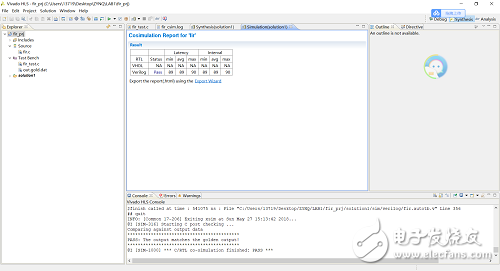

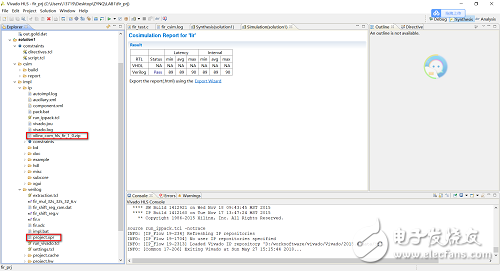

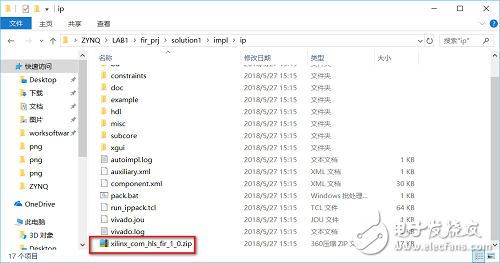

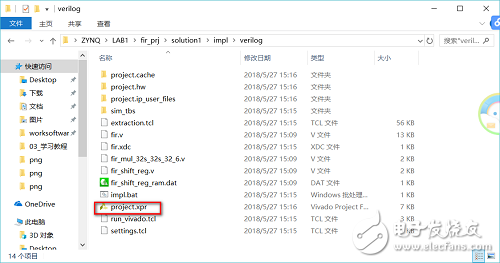

的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

2020-10-14 15:17:19 4185

4185

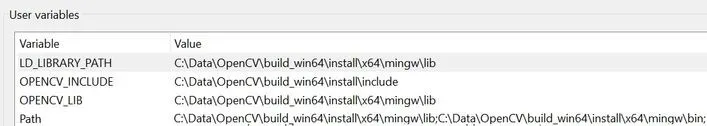

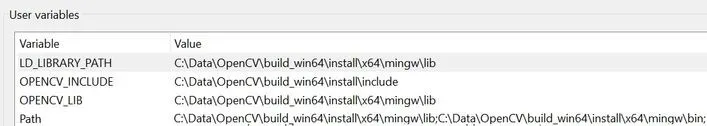

在论坛上遇到在高层次综合工具中调用视觉库遇到的大多数问题都和 opencv 库以及Xilinx Vision 库的安装路径有关,如今 Vitis HLS 2020.1 之后的版本都不再提供

2022-07-25 04:14:00 2362

2362

HLS任务级编程第一篇文章可看这里: HLS之任务级并行编程 HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。对于控制驱动型

2023-07-27 09:22:10 1950

1950

该项目通过一个示例演示了 HLS 中组合电路对设计的影响。

2023-11-03 09:04:09 1549

1549

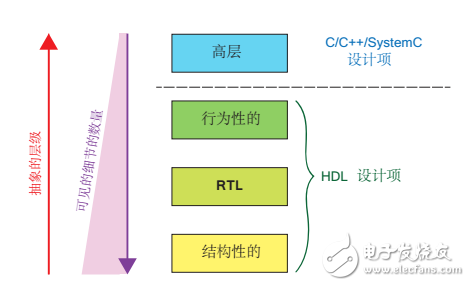

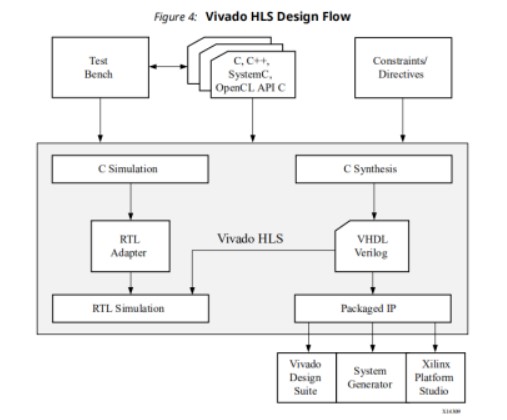

为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx 推出的 Vivado HLS 工具可以

2025-04-16 10:43:12 1432

1432

目录HLS案例开发2_led_flash案例|基于FPGAKintex-7开发板前 言案例功能HLS工程说明编译与仿真IP核测试更多推荐前 言本文led_flash案例是基于创龙科技TLK7-EVM

2021-02-24 19:23:30

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

你好, 我想在HLS中实现反向输入和自然输出算法。 但是,结果始终是: 我的代码是:void reverse_fft(compnum xin [FFT_SIZE]){ const int LH

2019-03-06 12:48:35

请教一下,我在HLS里面要将以下程序生成IP核,C Synthesis已经做好了,但是在export RTL的时候一直在运行

int sum_single(int A int B

2023-09-28 06:03:53

,需要更高级别的工具。Silexica的SLX是唯一真正支持多核自动生成软件的生态系统,无论是硬连线(hardwired),还是在FPGA上实现的软核(如果有的话)。在我们的例子中,SLX解决方案中

2021-07-10 08:00:00

。流水线设计的具体内容在我看到的这篇博客【FPGA中流水线的原因和方法】中讲的很明白,这里不再赘述。

在HLS中,pipeline指令单指函数内部的流水,举一个简单的例子:

void func(int m

2023-12-31 21:20:08

的RTL代码。在ISE或者Vivado开发环境中做RTL的集成和SOC/FPGA实现。2.2.1 VivadoHLS视频库函数HLS视频库是包含在hls命名空间内的C++代码。#include

2021-07-08 08:30:00

多个HLS解决方案2.实验内容实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench文件来与所得结果进行对比验证。...

2021-11-11 07:09:49

,需要更高级别的工具。Silexica的SLX是唯一真正支持多核自动生成软件的生态系统,无论是硬连线(hardwired),还是在FPGA上实现的软核(如果有的话)。在我们的例子中,SLX解决方案中

2021-07-06 08:00:00

:0.189秒!

二者相差15倍!

总结:

其实这个差距并不意外,PL(FPGA)本身就是为加速而生的。跑完这个过程只是验证要实现PL端加速具体需要哪些流程。利用高层次综合 (HLS) 工具,使得开发者

2023-10-13 20:11:51

主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx推出的Vivado HLS工具可以直接使用C、C++或System C来对Xilinx系列的FPGA进行编程,从而提高抽象的层级

2020-10-10 16:44:42

就是加速开发的周期。加速策略可以从两个方面考虑:(一)设计的重用和(二)抽象层次的提升。Xilinx Vivado开发套件中的IP集成功能可以实现设计的重用,而Vivado HLS工具则能够实现对高层次

2020-10-10 16:48:25

实现的图像处理模块已经被综合成FPGA中的硬件模块,可以实时地处理FPGA中的视频流。Vivado HLS所综合出来的视频处理模块同样可以部署在ZYNQ器件的PL端,其常用的架构如下图所示:图

2020-10-13 16:58:56

割。二值化的方法有很多,其中自适应二值化(OTSU)是图像二值化最常用的一种算法。本章我们将在HLS中实现图像的自适应二值化。本章包括以下几个部分:1111.1简介11.2实验任务11.3HLS

2020-10-14 16:04:34

或者更换Vivado版本,可以跳过本章节的学习。因为在18.3及其之后的Vivado HLS工具中,默认是支持HLS视频库的,大家依然可以使用HLS视频库中的函数进行设计开发。GitHub上

2020-10-16 16:22:38

)对正点原子FPGA感兴趣的同学可以加群讨论:8767449005)关注正点原子公众号,获取最新资料第四章呼吸灯实验在前面两个实验中我们学习了如何通过Vivado HLS工具来生成带有一个

2020-10-10 17:01:29

优化 FPGA HLS 设计

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

介绍

高级设计能够以简洁的方式捕获设计,从而

2024-08-16 19:56:07

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis

2022-09-09 16:45:27

模拟过程完成没有0错误,但在合成期间显示错误。我无法找到错误。我在合成期间在HLS工具中收到这样的错误“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

嗨,大家好,我有一个问题,在VIVADO HLS 2017.1中运行C \ RTL协同仿真。我已成功运行2014和2016版本的代码。任何人都可以告诉我为什么报告NA仅用于间隔

2020-05-22 15:59:30

FPGA的HLS案例开发|基于Kintex-7、Zynq-7045_7100开发板前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

嗨〜 如何在HLS 14.3中编写pow功能? HLS 14.3不支持exp和pow功能。我在我的代码中写了“#include math.h”。但是,它不起作用。 另外,我想知道C代码中

2019-03-05 13:40:09

。

Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx

2023-08-24 14:40:42

。Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx

2023-01-01 23:52:54

) xapp890-zynq-sobel-vivado-hls.pdf

5.1 HLS 工程说明(1) 时钟HLS 工程配置的时钟为 100MHz。如需修改时钟频率, 请打开 HLS 工程后点击 ,在弹出的界面中的 Synthesis 栏目进行修改。图 70

2023-08-24 14:54:01

) xapp890-zynq-sobel-vivado-hls.pdf5.1 HLS 工程说明(1) 时钟HLS 工程配置的时钟为 100MHz。如需修改时钟频率, 请打开 HLS 工程后点击 ,在弹出的界面中的 Synthesis 栏目进行修改。图 70(2) 顶层函数

2023-01-01 23:46:20

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 09:38:32

相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。Synphony HLS解决方案架构图

2019-08-13 08:21:49

和生成比特流以对FPGA进行编程4 - 将比特流导入并阻塞到SDK中,基于此生成板级支持包(BSP)并与Zedboard连接。顺便说一下,SDK的目标是成为我在Vivado HLS中的测试平台吗?即在计算机中观察Zedboard产生的结果是否为例外情况。

2020-03-24 08:37:03

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

。Vivado HLS作为该套件的一个组件,能帮助设计人员将采用C/C++语言开发的算法编译为RTL,以便在FPGA逻辑中运行。Vivado HLS工具非常适用于嵌入式视觉设计。在此流程中,您用C/C++

2014-04-21 15:49:33

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包软件。提供了一些基础的函数库以及常用的控制函数模块,配合

2022-05-19 09:16:05

FPGA调试工具chipscope,学习与使用FPGA必用的工具。。

2009-03-23 09:45:00 86

86 基于多种EDA工具的FPGA设计

介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实

2009-05-14 18:38:38 1036

1036

摘 要:在FPGA开发的各个阶段,市场为我们提供了很多优秀的EDA工具。面对眼花缭乱的EDA工具,如何充分利用各种工具的特点,并规划好各种工具的协同使用,对FPGA

2009-06-20 10:51:14 906

906 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

2017-02-07 17:59:29 4760

4760

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 4243

4243

供的数据类型,直接用HLS翻译成硬件的话,可能会造成硬件效率的下降。 举一个常见的例子。在xilinx FPGA中普遍含有DSP48,它可以提供18x18bit的乘法器,假如你的设计只需要17bit的乘法器,那么从FPGA实现角度,只需要1个DSP48就够了。但是由于标准C没有提供17bit的数据类型,

2017-02-08 02:50:11 1253

1253

在上一章HLS的端口综合里有提及,HLS综合后的端口分为2中类型:BlockLevel和Port Level Interface。其中Port level是我们需要重点关注的,它又可以细分为4中类型

2017-02-08 03:27:11 838

838

在之前HLS的基本概念1里有提及,HLS会把c的参数映射成rtl的端口实现。本章开始总结下HLS端口综合的一些知识。 1.HLS综合后的rtl端口大体可以分成2类: Clock Reset端口

2017-02-08 03:29:11 1162

1162

)和VHDL(2000),综合过程中,一般还需要特定的directives(约束脚本)来控制综合结果。 HLS对标准C基本都支持,除了以下4个特例: a)System Calls系统调用,比如printf

2017-02-08 05:23:11 1111

1111

HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

2019-10-12 17:34:00 2937

2937

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 我上篇博文我们能相信HLS吗?Brian Bailey想知道,也许你也想知道,在LinkedIn网站各种FPGA相关的群组中引发

2017-02-08 12:36:11 427

427 众所周知 Hackaday.com 网站上聚集着众多极客(Geeker),他们打破传统,标新立异,敢于尝试新的东西,今天这篇文章搜集了这些极客对Xilinx Vivado HLS工具使用经验和心得

2017-02-08 20:01:59 846

846

高层次综合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA设计工具,它能让用户通过编写C/C++等高级语言代码实现RTL级的硬件功能。随着这款工具

2018-07-14 06:42:00 8006

8006 Luke Miller并非一开始就是HLS(高层次综合)的倡导者。在使用早期的工具版本的时候,他似乎有过一些糟糕的经历。

2017-02-10 18:48:59 3929

3929

在特定图像处理硬件设计中成功运用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 数年之后, Qualcomm 认识到了 HLS

2017-09-11 11:37:38 9

9 使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 4363

4363

如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado® 设计套件高层次综合(HLS) 工具是创建高性能加速器的极好资源。通过向C 语言高级算法描述中添加一些编译指示,就可以在赛灵思FPGA 上快速实现高吞吐量的处理引擎。

2017-11-17 18:12:01 2315

2315 通常基于传统处理器的C是串行执行,本文介绍Xilinx Vivado-HLS基于FPGA与传统处理器对C编译比较,差别。对传统软件工程师看来C是串行执行,本文将有助于软件工程师理解

2017-11-18 12:23:09 3066

3066

摘要:HTTP Live Streaming(缩写是HLS)是一个由苹果公司提出的基于HTTP的流媒体网络传输协议。今天主要以HLS协议为中心讲述它的一些原理。

2017-12-10 09:25:37 56558

56558 在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

2018-01-10 14:33:02 20579

20579

高级综合( HLS)工具及其入门指南

2018-06-20 00:08:00 4927

4927

新思科技公司高层级综合法和系统级别营销总监Chris Eddington介绍说,Synphony HLS解决方案可显着地改变ASIC和FPGA在系统验证和嵌入式软件开发中的应用方式。

2018-07-19 15:40:00 1985

1985 Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS为FPGA流程提供集成化设计与开发环境,率先支持5G无线应用。

2018-08-30 10:09:32 8283

8283 作为集成电路设计领域现场可编程门阵列 (FPGA) 技术的创造者之一,赛灵思一直积极推广高层次综合 (HLS) 技术,通过这种能够解读所需行为的自动化设计流程打造出可实现此类行为的硬件。赛灵思刚刚推出了一本专著,清晰介绍了如何使用 HLS 技术来创建优化的硬件设计。

2018-11-10 11:01:05 3178

3178 转化得到 RTL 基本不可能。其实,使用 FPGA 工具设置来优化设计可以最小限度地减少对性能的牺牲,这种方法是存在的。

2018-12-16 11:19:28 1903

1903

用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。 本项目所需应用与工具:赛灵思HLS、Plunify Cloud 以及 InTime。 前言 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。

2019-09-15 11:56:00 767

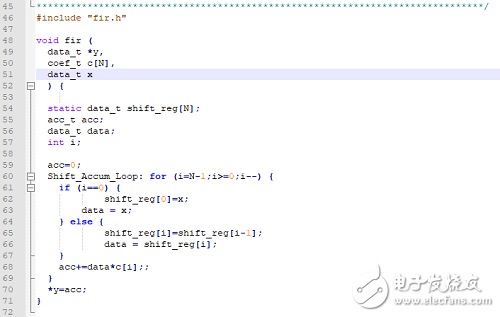

767 介绍了如何利用Vivado HLS生成FIR滤波算法的HDL代码,并将代码添加到ISE工程中,经过综合实现布局布线等操作后生成FPGA配置文件,下载到FPGA开发板中,Darren采用的目标板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 5460

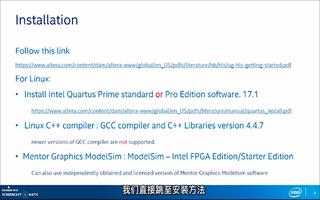

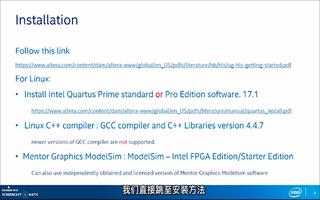

5460 接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写

2019-07-31 09:45:17 7434

7434

本系列教程演示如何使用xilinx的HLS工具进行算法的硬件加速。

2021-06-17 10:20:33 10326

10326

FPGA并没有像软件那样用已有的cache,FPGA的HLS编译器会在FPGA中创建一个快速的memory architecture以最好的适应算法中的数据样式(data layout)。因此FPGA可以有相互独立的不同大小的内部存储空间,例如寄存器,移位寄存器,FIFOs和BRAMs。

2022-04-07 11:31:57 8615

8615 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 3450

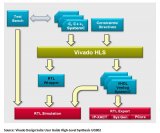

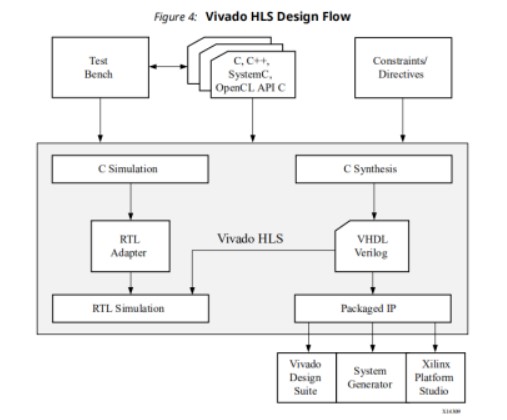

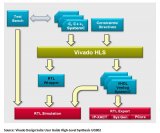

3450 在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 8680

8680 HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 2261

2261

Vitis HLS 工具能够将 C++ 和 OpenCL 功能部署到器件的逻辑结构和 RAM/DSP 块上。在 GitHub 上提供 Vitis HLS 前端为研究人员、开发人员和编译器爱好者开启了无限可能的新世界,使他们可以利用 Vitis HLS 技术并根据其应用的特定需求进行修改。

2022-08-03 09:53:58 1602

1602 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 4612

4612 软件编译器讲高级语言翻译成为机器语言。主要关注的语言的语法转换规则,相比之下,HLS 的翻译难度更大一些,模块中的语句形式上是前后顺序排列。但是HLS尽力转换成为并行执执行的硬件逻辑。

2022-10-10 14:50:29 2419

2419 电子发烧友网站提供《ThunderGP:基于HLS的FPGA图形处理框架.zip》资料免费下载

2022-10-27 16:49:59 0

0 1、HLS简介 HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境中来

2022-12-02 12:30:02 7407

7407 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2023-01-15 11:27:49 4024

4024 是Vitis HLS。在Vivado 2020版本中替代原先的Vivado HLS, 功能略有差异。 HLS 的机理 简单地讲,HLS采样类似C语言来设计FPGA 逻辑。但是要实现这个目标,还是不容易

2023-01-15 12:10:04 6467

6467 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 1730

1730

电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 3

3 在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该是设计上的延时之类的比较大,暂时放弃这个方案,调用HLS中自带的FFT库(hls:fft

2023-07-11 10:05:35 1967

1967

本篇博客介绍 VVAS 框架所支持调用的 H/W(HLS) 内核。 H/W 内核指的是使用 HLS 工具生成的在 FPGA 部分执行的硬件功能模块。

2023-08-04 11:00:43 1647

1647

电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2 电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0 很多人都比较反感用C/C++开发(HLS)FPGA,大家第一拒绝的理由就是耗费资源太多。但是HLS也有自己的优点,除了快速构建算法外,还有一个就是接口的生成,尤其对于AXI类接口,按照标准语法就可以很方便地生成相关接口。

2024-07-16 18:01:03 1940

1940

本文将首先介绍FPGA的基础知识,包括FPGA的工作原理以及为什么要使用FPGA等,然后讨论设计和执行FPGA应用所需的工具。

2024-11-11 11:29:44 2486

2486

在 AI 赋能工程设计的时代浪潮中,智多晶率先迈出关键一步——智多晶正式宣布旗下 FPGA 设计工具 HqFpga 接入 DeepSeek 大模型,并推出 FPGA 设计专属 AI 助手——晶小助!这是 FPGA 领域首次引入大模型 AI 助手,为 FPGA 工程师提供前所未有的智能交互体验。

2025-06-06 17:06:39 1284

1284

电子发烧友App

电子发烧友App

评论