组合电路在 HLS 中的重要性

该项目通过一个示例演示了 HLS 中组合电路对设计的影响。

在 HLS 中描述组合任务非常重要,因为它直接影响整个系统的性能。这里我举一个简单的例子来解释一下这个问题。

介绍

高级综合工具将算法转换为等效的 RTL 描述。该描述代表逻辑电路,可以通过ASIC或FPGA技术来综合。

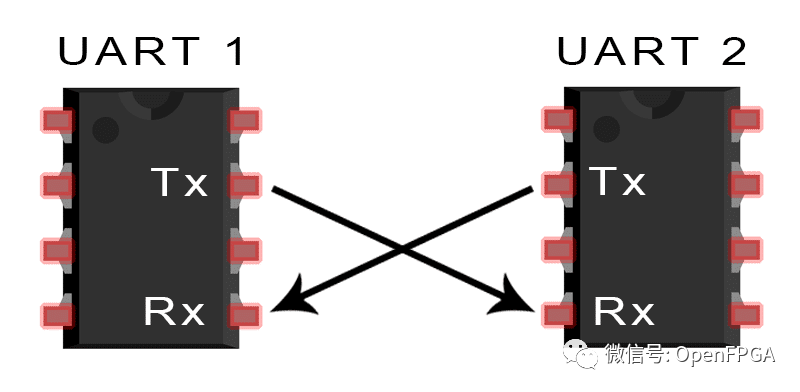

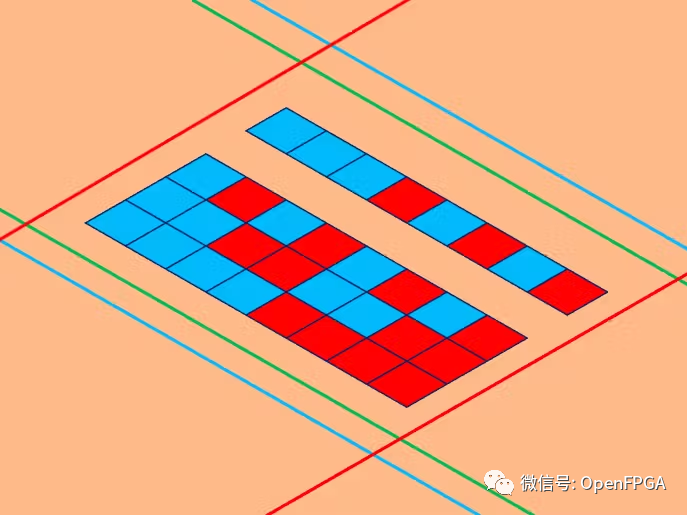

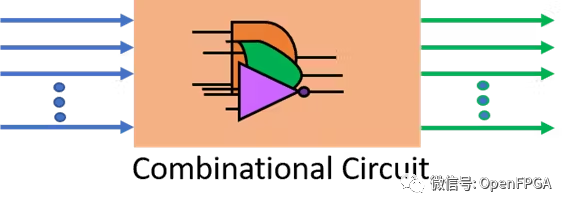

逻辑电路可以是以下两种类型之一:组合电路或时序电路。组合电路的输出仅是其输入上的当前逻辑值的函数。如图1所示,只需使用基本逻辑门即可实现组合电路,不需要存储单元。

图1

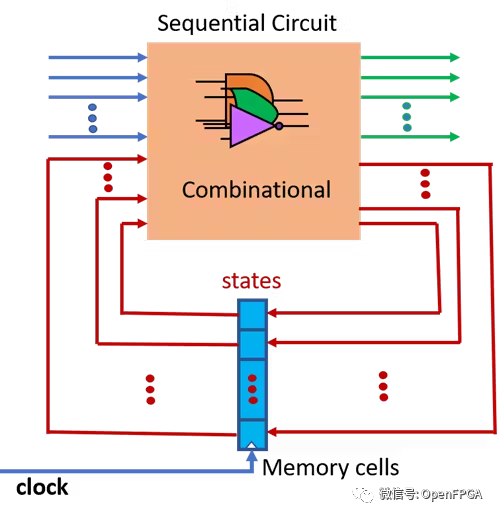

另一方面,时序电路的输出不仅取决于其输入的当前值,还取决于过去时间的输入值的历史记录。

电路状态通常模拟输入值历史的影响。一组存储单元可以代表这些状态。

图2

图2显示了由组合电路和一组保存电路状态的存储单元组成的时序电路的结构。存储器单元可以是触发器、BRAM或DDR存储器的形式。

组合部分接收两组数据:主输入和状态。然后它生成两组输出:主要输出和下一个状态。系统中的其他模块使用主输出,而下一个状态数据修改存储单元并定义新的电路状态。

动机

所有组合电路都需要一个时间间隔,以便在其输入发生任何变化后产生稳定的输出。这个时间被称为传播延迟。组合电路中从输入到输出的不同路径可能具有各种延迟。最长路径也称为关键路径,被定义为设计传播延迟。

在时序电路中,时钟周期对设计性能有直接影响。图 2 中组合部分的传播延迟决定了最小时钟周期。因此,它的好坏直接影响到整个系统的性能。

时序电路通常需要几个时钟周期来完成其相关任务。所需时钟周期的最大数量称为设计延迟。组合部分也对相关时序电路的延迟有直接影响。

因此,了解如何在 HLS 中设计高效的组合电路是在硬件上开发高性能算法的第一步。

组合电路的影响

在这里,将通过一个例子来解释正确的 C/C++ 描述组合设计如何能够加快实现速度。

假设我们要在如图 3 所示的 Basys3 FPGA 评估板上可用的四个七段上显示数字的四位十进制数字。

图3

第一步是提取四位十进制数字,然后找到每个数字对应的七段代码,并将代码发送到板上的段选择上。这里我只解释第一个任务,即提取四位小数。

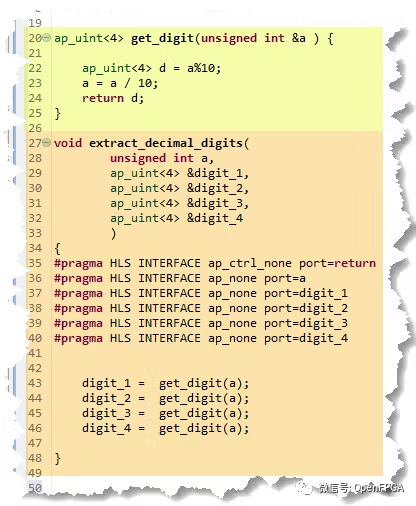

让我们考虑以下 Vivado-HLS 代码,该代码提取 4 位无符号整数的十进制数字。设计顶部函数是extract_decimal_digits ,它接受输入参数(即a )并生成四个输出(即 digital_1、digit_2、digit_3、digit_4)。它调用函数get_digit四次来提取每个数字。get_digit函数提取接收到的号码的第一位数字,然后对其进行修改。

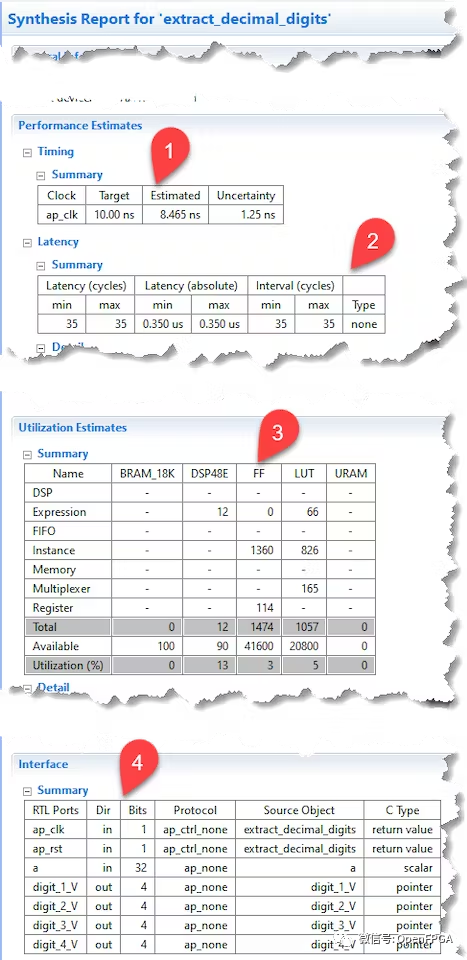

如果我们执行高级综合过程来生成等效的 RTL 设计,则图 5 显示了 Basys3 板的报告。Vivado-HLS 综合过程利用参数化的 Xilinx LogiCORE 除法器内核来实现模运算。该代码具有流水线结构。

可以看出,设计时钟周期约束为10 ns(用1注释)。流水线设计需要 35 个周期来完成其任务,即 0.35 us(用 2 表示)。此外,它还使用了 12 个 DSP、1474 个 FF 和 1057 个 LUT。

图5

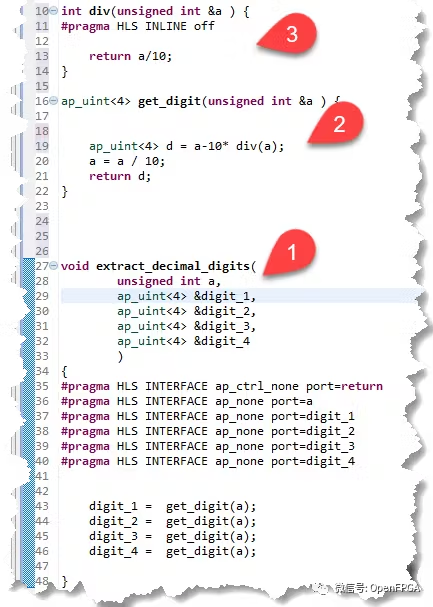

现在让我们考虑以下实现,将模运算替换为其等效的算术表达式,即 a%10 = a – 10*(a/10)。如果我们直接使用这个表达式,编译器会优化代码,再次使用模运算,并生成相同的 RTL 描述。为了阻止编译器优化代码,我使用了一个单独的子函数来执行除 10 运算符。另外,还关闭了编译器函数内联功能。

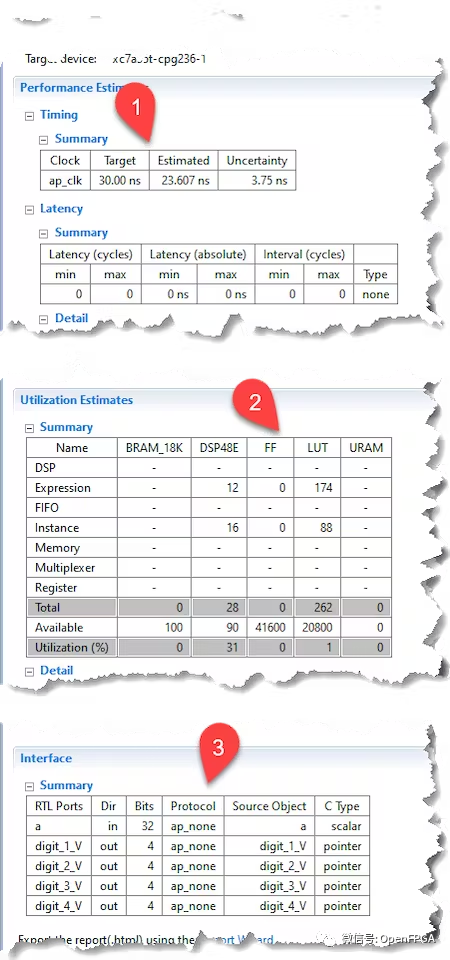

现在,如果我们综合此代码,图 7 将显示相应的报告。

该电路完全由组合电路搭建。电路传播延迟为23.607 ns,使用28个DSP和262个LUT。

图7

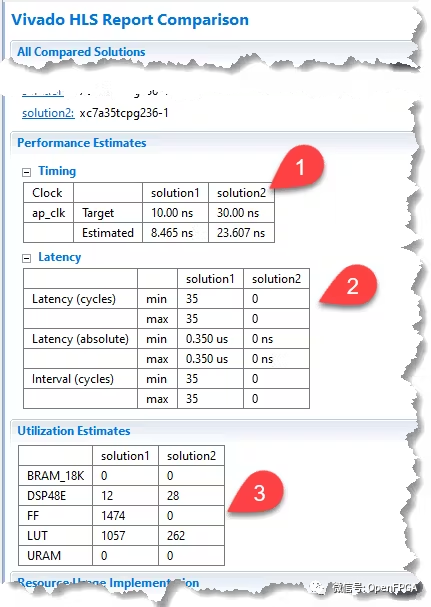

比较这两种实现方式:图 8 显示了比较结果。在该图中,“Solution 1”对应于使用模运算符的第一种方案,“Solution 2”代表第二种方案。

可以看出,第一种方案需要 35 个时钟周期,由于时钟周期为 10 ns,因此需要 350 ns才能生成输出。然而,第二种方案只需要 23.607 ns 即可生成输出。所以第二个实现速度快了 14.83 倍。

此外,第二种方案在 FPGA 上使用的资源要少得多。

结论

设计高效的组合电路是在 HLS 中开发算法或系统控制器的第一步。多种优化技术和编码风格可用于描述复杂算法的组合部分。

审核编辑:刘清

-

逻辑电路

+关注

关注

13文章

503浏览量

43842 -

asic

+关注

关注

34文章

1271浏览量

124087 -

RTL

+关注

关注

1文章

393浏览量

62422 -

组合电路

+关注

关注

0文章

11浏览量

6834 -

HLS

+关注

关注

1文章

133浏览量

25626

原文标题:组合电路在 HLS 中的重要性

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何使用AMD Vitis HLS创建HLS IP

如何在Unified IDE中创建视觉库HLS组件

探索Vivado HLS设计流,Vivado HLS高层次综合设计

如何在HLS 14.3中编写pow功能?

如何使用Vivado HLS生成了一个IP

合成中的Vivado HLS中的Pragma错误怎么解决

【正点原子FPGA连载】第一章HLS简介-领航者ZYNQ之HLS 开发指南

Vivado HLS设计流的相关资料分享

FPGA高层次综合HLS之Vitis HLS知识库简析

使用Vitis HLS创建属于自己的IP相关资料分享

HLS中RTL无法导出IP核是为什么?

hls协议是什么?hls协议详细介绍

FPGA设计中的HLS 工具应用

HLS中组合电路对设计的影响

HLS中组合电路对设计的影响

评论