HLS 的机理

二、HLS技术难点

所谓的高层次综合(HLS)就是将C/C++/System C描述的设计意图, “翻译“成用Verilog/System Verilog描述的RTL,多应用于运算逻辑主导的设计。

这就产生了几个问题:

HLS输入并不是软件语言。相反,它是对硬件的更抽象的描述。大多数HLS工具可以使用C语言、SystemC或者C++作为输入语言。

从技术上来说,C++是一种“语言”,但从C/C++语言生成硬件电路模型来看,它也意味着算法的抽象级别。

原始的C代码经常会被修改

使用HLS将软件代码综合成实际的硬件电路时,存在几个基本挑战

代码必须由HLS引擎合成,也就是说,必须将代码编写或重构为硬件可综合的格式,其对习惯于使用标准C/C++编写的软件工程师而言非常重要。

HLS编码的可综合性准则很重要,工程师必须熟悉这些涵盖数百页文档的准则。

一旦代码可综合,还需要一定程度的底层硬件意识。

扫描二维码获取

更多精彩

FPGA设计论坛

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站):

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂):

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

更多资料下载欢迎注册http://www.fpgaw.com

扫码加微信回复加群

邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA——HLS简介

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22503浏览量

639290

原文标题:FPGA——HLS简介

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

HLS设计中的BRAM使用优势

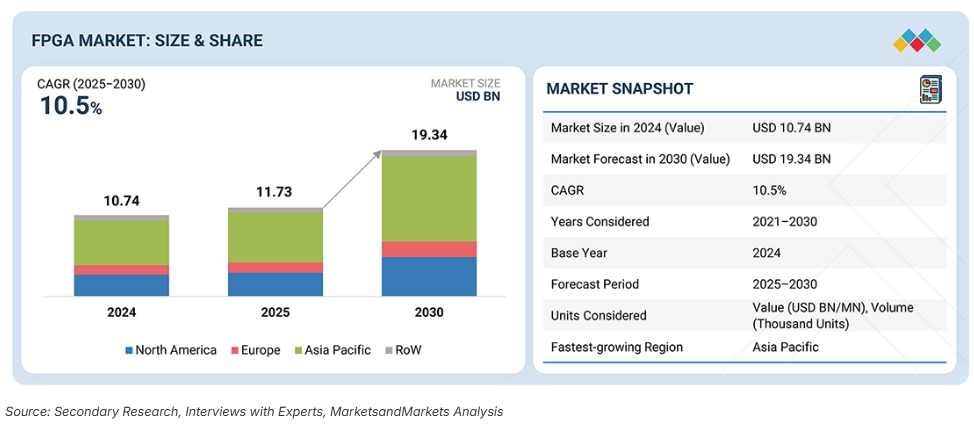

MarketsandMarkets FPGA行业报告,2026~2030 FPGA市场洞察

蜂鸟处理器+OV5640摄像头模块开发

硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......

基于FPGA的肤色检测方案简介

如何在vivadoHLS中使用.TLite模型

Altera Agilex™ 3 FPGA和SoC FPGA

基于FPGA的压缩算法加速实现

如何在Unified IDE中创建视觉库HLS组件

使用AMD Vitis Unified IDE创建HLS组件

开源FPGA硬件,核心开发者招募中......

如何使用AMD Vitis HLS创建HLS IP

FPGA——HLS简介

FPGA——HLS简介

评论