您是否担心 RTL 设计中的延迟?

您的设计是否有效并经过优化?

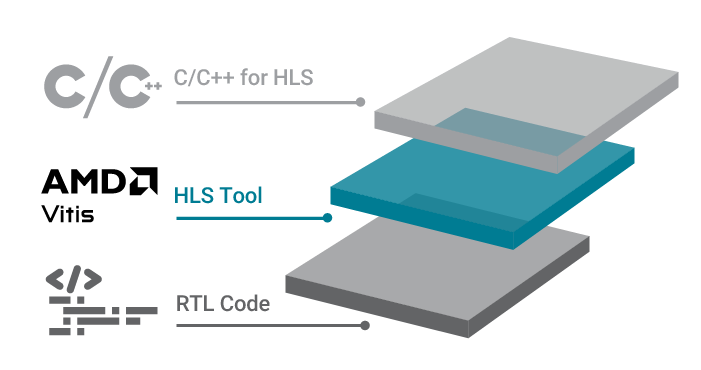

通过 Vitis HLS,您可将 C/C++ 函数综合到 RTL 中,从而轻松创建复杂设计算法。

AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

使用 Vitis HLS 流程,用户可针对 C 代码应用指令,创建专门用于所需实现方案的 RTL。

不仅可从 C 语言源代码创建多个设计架构,而且还可启用用于高质量 Correct-by-Construction RTL 的路径。

C 语言仿真可用于验证设计,支持比基于 RTL 的传统仿真更快的迭代。

Vitis HLS 工具具有一系列丰富的分析及调试工具,其可促进设计优化。

全新推出的Vitis HLS资源,具有以下特点:

较之传统的 RTL,Vitis HLS 可实现更快的设计验证和更高效的迭代

通过 Vitis HLS,开发者可使用 C/C++ 代码中的自动 pragma 推理、流水线循环和函数等高级功能来满足系统性能要求

审核编辑 :李倩

-

amd

+关注

关注

25文章

5708浏览量

140445 -

源代码

+关注

关注

96文章

2953浏览量

70678 -

Vitis

+关注

关注

0文章

158浏览量

8430

原文标题:AMD 全新Vitis HLS资源现已推出

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AMD Power Design Manager 2025.2版本现已发布

全新AMD Vitis统一软件平台2025.2版本发布

AMD Vivado Design Suite 2025.2版本现已发布

如何在AMD Vitis Unified IDE中使用系统设备树

AMD Vitis AI 5.1测试版现已开放下载

AMD Vitis AI 5.1测试版发布

AMD Vivado设计套件2025.1版本的功能特性

如何在AMD Vitis Unified 2024.2中连接到QEMU

AMD Power Design Manager 2025.1现已推出

全新AMD Vitis统一软件平台2025.1版本发布

使用AMD Vitis Unified IDE创建HLS组件

AMD Vivado Design Suite 2025.1现已推出

如何使用AMD Vitis HLS创建HLS IP

AMD全新Vitis HLS资源现已推出

AMD全新Vitis HLS资源现已推出

评论