开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。 第一章:模块书写 Verilog HDL 语言的基本语法与 C语言相似,因此与 VHDL 相比较更容易上手。本章将会在实际小项目的基础上,以 Verilog HDL 语言为主, 教读者怎么更方便、更高效的

2020-11-13 16:02:12 4676

4676

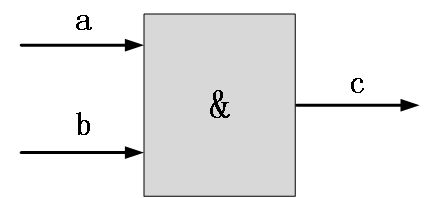

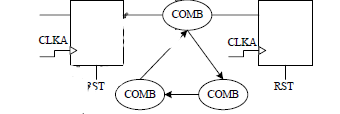

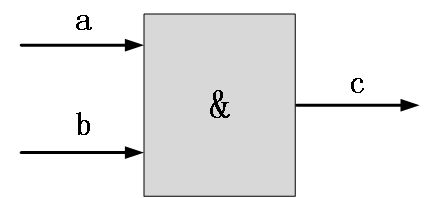

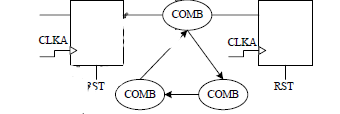

一、逻辑设计 (1)组合逻辑设计 下面是一些用Verilog进行组合逻辑设计时的一些注意事项: ①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表

2020-11-23 13:05:17 3923

3923

优秀的 Verilog/FPGA开源项目介绍(三十四)- PDM音频接口设计及信号处理 绪论 今天介绍几个与PDM接口相关的开源项目。 FPGA使用Delta-sigma ADC实现PDM音频

2022-10-17 09:10:33 4424

4424 可综合的语法是指硬件能够实现的一些语法,这些语法能够被EDA工具支持,能够通过编译最终生成用于烧录到FPGA器件中的配置数据流。

2023-07-23 12:25:10 2600

2600 本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-12-12 09:19:08 3688

3688

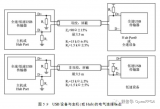

本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试,包括设计SRAM接口模块

2025-10-22 17:21:38 4118

4118

FPGA、CPLD常用protel库FPGA&CPLD_LIB.ddb

2012-08-11 10:32:00

商店的IP核库中索取组件进行配置,最后像搭积木一样完成一个项目,或者整个设计都不需要见到一句代码。当然了,未来什么情况都有可能发生,但是底层的代码逻辑编写方式无论如何还是有其生存空间的,毕竟一个个IP

2015-01-29 09:20:41

可以了解目前最流行的Verilog HDL语言的基本语法,掌握Verilog HDL语言中最常用的基本语法。通过本节课程学习,学员可以设计一些简单的FPGA程序,掌握组合逻辑和时序逻辑电路的设计方法

2014-11-30 17:38:06

。笔者基于实际项目中所涉及到的技术点,一步一步指导初学者学会FPGA设计,要想学会FPGA,必须经历一下几个关键点:1:对一个中等规模的模块(500-1000行代码)必须敢于下手,在综合的过程中

2014-12-12 09:38:19

语法,这些语法能够被EDA工具所支持,能够通过编译最终生成用于烧录到FPGA器件中的配置数据流。无论是Verilog语言还是VHDL语言,可综合的子集都很小。但是如何用好这些语法,什么样的代码风格

2015-06-12 10:59:24

的逻辑电路。模块四 FPGA设计常用IP模块使用[size=12.0000pt]FPGA设计常用IP模块使用课程主要内容为FPGA设计中常用IP模块的使用(单/双口RAM、DPRAM、FIFO、ROM及串行

2015-09-29 16:33:54

的逻辑电路。模块四 FPGA设计常用IP模块使用[size=12.0000pt]FPGA设计常用IP模块使用课程主要内容为FPGA设计中常用IP模块的使用(单/双口RAM、DPRAM、FIFO、ROM及串行

2015-09-30 10:36:41

处理器的数字钟设计 第9章 FPGA系统设计原则和技巧 9.1 FPGA系统设计的3个基本原则 9.2 FPGA系统设计的3种常用技巧 9.3 FPGA系统设计的3种常用IP模块 第10章 利用

2012-02-09 15:45:32

FPGA的IP软核使用技巧主要包括以下几个方面:

理解IP软核的概念和特性 :

IP软核是指用硬件描述语言(如VHDL或Verilog)描述的功能块,但并不涉及具体的电路实现细节。它通常只经过功能

2024-05-27 16:13:24

apex20ke_atoms.v编译到其中。2:在图形界面中的Load Design对话框中装入仿真设计时,在Verilog 标签下指定预编译库的完整路径。(见下图)逻辑综合目前可用的FPGA综合工具

2020-05-15 07:00:00

FPGA系统设计原则和技巧之:FPGA系统设计的3种常用IP模块.pdf(1012.86 KB)

2019-04-24 13:33:04

语言(Verilog HDL)是FPGA工程师的基本要求。通过本节课程的学习,学员可以了解目前最流行的Verilog HDL语言的基本语法,掌握Verilog HDL语言中最常用的基本语法。通过本节课程学习,学员可以

2014-04-23 15:28:29

1. 目的本规范的目的是提高书写代码的可读性、可修改性、可重用性,优化代码综合和仿真的结果,指导设计工程师使用VerilogHDL规范代码和优化电路,规范化可编程技术部的FPGA设计输入,从而做到

2017-12-08 14:36:30

关键字:Altera 、FPGA、软硬件协调设计(Verilog & C)、CPU、总线、外设FPGA硬件结构知识Verilog HDL语言编程基础FPGA常用开发工具 SOPC硬件系统开发SOPC软件系统开发Avalon总线规范Nios II外设及其编程 七段数码管时钟...

2021-12-22 08:06:06

Verilog可综合子集

2013-04-01 12:44:46

这里在网上找到一个fpga/cpld常用protel库,传上来给大家一起分享,好动西就是要大家一起,[hide][/hide]

2012-01-09 10:57:07

语句在用综合工具综合时将被忽略或者报错。作为设计者,应该对可综合模型的结构有所了解。 虽然不同的综合工具对Verilog HDL语法结构的支持不尽相同,但Verilog HDL中某些典型的结构是很

2012-10-20 08:10:13

1,在一个verilog程序里,如果循环是一个循环次数不可定的循环,那么它能被综合工具综合吗2,如果程序里有always @(clock)里面又嵌套了@(clock)这样的控制事件,这个能被综合吗

2015-02-03 15:29:11

,若不是,则只能用于仿真),while, 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

的编程风格SYSTEM VERILOG是VERILOG的一种延伸15.IP核的应用:软核soft core: 功能经过验证的、可综合的、实现后门数在5K以上的HDL代码固核firm core: 功能经过

2012-01-12 15:15:21

可综合的Verilog语法和语义(剑桥大学,影印)

2012-08-06 13:03:57

可综合的VerilogHDL设计实例在前面七章里我们已经学习了VerilogHDL的基本语法、简单组合逻辑和简单时序逻辑模块的编写、Top-Down设计方法、还学习了可综合风格的有限状态机

2009-11-23 16:01:33

请问开源FPGA项目有哪些?

2023-12-26 12:09:06

,都有Xilinx公司自己写好的可综合的模块,想请教一下为什么要分成这样两项?它们里面的模块有区别吗?2、上述谈到的可综合模块和ISE 自带的IP core又有什么区别呢?

2013-09-28 18:17:54

,都有Xilinx公司自己写好的可综合的模块,想请教一下为什么要分成这样两项?它们里面的模块有区别吗?2、上述谈到的可综合模块和ISE 自带的IP core又有什么区别呢?

2013-09-28 18:20:29

7.2设计入门(视频)第8讲:NIOSII 7.2 设计入门(视频)第9讲:FPGA系统设计技巧-乒乓操作(视频)第10讲:FPGA设计常用IP核-锁相环(视频)地址:http

2009-03-26 16:37:40

:从零开始设计FPGA最小系统一: 核心电路(PDF、视频)第3讲:从零开始设计FPGA最小系统二: 外围电路(PDF、视频)第4讲:Verilog HDL语法一:常用语句(视频)第5讲

2009-03-09 22:56:25

方式;固核则通常介于上面两者之间,它已经通过功能验证、时序分析等过程,设计人员可以以逻辑门级网表的形式获取。FPGA的开发方式分为三种,分别是:原理图、Verilog HDL以及IP核。其中原理图方式

2016-12-22 23:37:00

II、ISE等一种以上开发工具进行综合布局布线,熟悉显示行业常用的相关接口;能独立承担硬件FPGA设计项目,按照项目计划要求完成任务,能够独立进行FPGA需求分析、芯片评估、器件选型,并完成相关硬件系统

2017-06-29 13:47:39

的 Verilog/FPGA开源项目》内容介绍更加详细,包括但不限于综合、上板测试等。两者相辅相成,互补互充~

这几年DPU的概念越来越火,有和CPU、GPU并驾齐驱的势头,通俗的讲DPU分担的工作

2023-11-01 16:27:44

XST支持哪些语言?VHDL, Verilog-2002, 以及Mixed Language of VHDL and Verilog。所支持的可综合的VHDL和Verilog的子集可以查看XST

2018-08-08 10:31:27

的基本要求。通过本节课程的学习,学员可以了解目前最流行的Verilog HDL语言的基本语法,掌握Verilog HDL语言中最常用的基本语法。通过本节课程学习,学员可以设计一些简单的FPGA程序

2018-09-19 11:34:03

,是指硬件能够实现的一些语法,这些语法能够被EDA工具所支持,能够通过编译最终生成用于烧录到FPGA器件中的配置数据流。无论是Verilog语言还是VHDL语言,可综合的子集都很小。但是如何用好这些语法

2017-12-06 19:50:25

`勇敢的芯伴你玩转Altera FPGA连载33:可综合的语法子集4特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 连续赋值

2017-12-19 21:36:24

工程师的基本要求。通过本节课程的学习,学员可以了解目前最流行的Verilog HDL语言的基本语法,掌握Verilog HDL语言中最常用的基本语法。通过本节课程学习,学员可以设计一些简单的FPGA

2015-10-27 17:57:38

1 背景知识采用基于FPGA的方式进行系统设计,具备运行传输速度快、并行处理内部程序、有大量开发好的IP核、引脚众多、设计灵活等优点。针对被测样机的功能模式和受控电路模块众多,对控制器I/O引脚资源

2018-08-07 10:08:19

的挑战。本文采用RFC815中的重组算法实现的基于FPGA的IP碎片重组模块能够提供对OC-48接口流量的支持,具有硬件开销小,可扩展性好的特点,并提供了一种针对IP碎片攻击的预警机制,能够抵抗常见

2008-10-07 11:00:19

作为我项目的一部分,我需要将ADC与7系列FPGA接口,我有一个SelectIO™接口向导的IP核。但是,我的整个项目都在VHDL中,IPi得到的是Verilog。请指出我如何在我的VHDL顶级模块中使用该IP核的一些示例。最好的祝福

2020-05-21 12:31:59

阅读目录 linux/嵌入式常用开源库列表其他资料参考资料linux下/嵌入式常用的开源库名字及简介,使用文档和教程可以自己百度 (自己整理,不定时完善) linux/嵌入式常用开源库列表

2021-12-24 06:53:15

verilog代码,该代码描述了一个加法器功能。该代码经过综合器解释后,转化成一个加法器电路。QUARTUS、ISE和VIVADO都是综合器,集成电路常用的综合器是DC。我们在FPGA设计的过程中,不可避免

2018-10-08 15:19:23

是在描述硬件,即用代码画图。在 Verilog 语言中,always 块是一种常用的功能模块,也是结构最复杂的部分。笔者初学时经常为 always 语句的编写而苦恼.

2021-07-29 07:42:25

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包软件。提供了一些基础的函数库以及常用的控制函数模块,配合

2022-05-19 09:16:05

Verilog HDL 综合实用教程第1章 基础知识第2章 从Verilog结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

2009-07-20 11:21:13 86

86 给出了一种基于FPGA的分频电路的设计方法.根据FPGA器件的特点和应用范围,提出了基于Verilog的分频方法.该方法时于在FPGA硬件平台上设计常用的任意偶数分频、奇数分频、半整数分频

2011-11-09 09:49:33 355

355 可综合的Verilog语法和语义(剑桥大学,影印):第七版

2012-05-21 14:50:14 27

27 文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法

2012-12-24 09:51:45 2670

2670 Xilinx FPGA工程例子源码:IP camera的开源系统

2016-06-07 14:13:43 13

13 FPGA verilog 相关设计实践

2017-09-06 11:19:34 34

34 本文档的主要内容详细介绍的是常用模块的Verilog HDL设计详细资料免费下载。

2018-10-16 11:12:54 20

20 本文档的主要内容详细介绍的是FPGA视频教程之Verilog基础的详细资料说明包括了:1.Verilog HDL简介,2.Verilog HDL模型的基本结构,3.Verilog HDL模块的组成

2019-03-21 15:02:49 37

37 在接触Verilog 语法参考手册的时候,我们发现其提供了一组非常丰富的功能来描述硬件。所以大家往往会疑惑那些Verilog语句是可综合的,那些是只能用于写Testbench的,其实,参考手册中只有

2019-04-20 10:59:39 5221

5221 本文档的主要内容详细介绍的是FPGA的视频教程之Verilog模块的基本构成要素资料说明。

2019-03-26 16:55:21 13

13 本文档的主要内容详细介绍的是FPGA的视频教程之Verilog模块中的信号详细资料说明。

2019-03-26 16:55:23 17

17 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-02 07:10:00 3646

3646

Verilog中提供了四种循环语句,可用于控制语句的执行次数,分别为:for,while,repeat,forever。其中,for,while,repeat是可综合的,但循环的次数需要在编译之前就确定,动态改变循环次数的语句是不可综合的。forever语句是不可综合的,主要用于产生各种仿真激励。

2019-10-13 12:23:00 20332

20332 端口添加多数表决电路。构建这种三重化方案是一项非常重要的任务,需要花费大量的时间和精力来修改设计代码。本文开发了RASP-TMR工具,该工具具有以可综合的Verilog设计文件为输入,对设计进行解析和三次复制的功能。该工具还生成了一个顶层模块,其中所有三个模块都

2020-04-16 08:00:00 5

5 可综合模块最终生成的bit文件会烧录进芯片运行,而仿真模块编译过后是在仿真软件(例如modelsim)上运行的。仿真模块是基于可综合模块进行例化,并通过仿真软件的模拟,可以初步验证我们写的可综合模块的实现现象。

2020-11-27 14:27:27 4454

4454 本文主要介绍verilog基础模块,夯实基础,对深入学习FPGA会有很大帮助。

2022-02-08 15:04:08 3315

3315

本文主要介绍verilog基础模块,夯实基础,对深入学习FPGA会有很大帮助。

2021-01-22 10:41:17 5

5 本教程解释了如何在基于Verilog的设计中包含Altera的库模块,这些设计是使用Quartus R:II软件实现的。

2021-01-22 15:34:12 4

4 开发所有可综合Verilog的语义所选择的方法是从过于简单的{V0{开始,然后在简单的语义中断时使其更加复杂。这样可以避免不必要的复杂性。计划对越来越大的子集(V1、V2等)进行重新排序,这些子集将收敛到剑桥VFE project2中使用的Verilog版本。

2021-02-05 16:24:05 14

14 电路“胸有成竹”; 牢记可综合Verilog HDL与电路结构一一对应的关系; 确认电路指标是什么:性能?面积? 硬件思维方式,代码不再是一行行的代码而是一块一块的硬件模块; 达到以上几点,就可以确保写出行云流水般的高质量代码。 关于代码与硬件电路的对应关系,参见如下图

2021-04-04 11:19:00 4854

4854

FPGA CPLD中的Verilog设计小技巧(肇庆理士电源技术有限)-FPGA CPLD中的Verilog设计小技巧

2021-09-18 16:49:18 37

37 该FPGA项目旨在详细展示如何使用Verilog处理图像,从Verilog中读取输入位图图像(.bmp),处理并将处理结果写入Verilog中的输出位图图像。提供了用于读取图像、图像处理和写入图像

2021-09-23 16:17:07 5361

5361 该FPGA项目旨在详细展示如何使用Verilog处理图像,从Verilog中读取输入位图图像(.bmp),处理并将处理结果写入Verilog中的输出位图图像。提供了用于读取图像、图像处理和写入图像

2021-09-23 15:50:21 7240

7240 优秀的 Verilog/FPGA开源项目介绍(一)-PCIe通信 今天开始会陆续介绍一些优秀的开源项目,项目基本都是和FPGA或HDL相关的。对于一些找工作或者急需项目经验的人来说,这些项目都有一定

2021-10-11 15:31:47 11032

11032

阅读目录linux/嵌入式常用开源库列表其他资料参考资料linux下/嵌入式常用的开源库名字及简介,使用文档和教程可以自己百度 (自己整理,不定时完善)linux/嵌入式常用开源库列表

2021-10-20 19:20:59 5

5 优秀的 Verilog/FPGA开源项目介绍(五)- USB通信 USB是我们生活中非常非常常见的接口,鼠标、键盘以及常见的U 盘等,可以说现在的USB设备已经渗透到生活中的方方面面,下面就介绍几个

2021-11-02 14:54:15 10037

10037

优秀的 Verilog/FPGA开源项目介绍(七)- CAN0、CAN总线介绍《【科普】CAN总线介绍及FPGA实现方案简介》 1、CAN权威文档CAN总线有两个ISO国际标准:ISO11898

2021-11-17 11:19:56 3801

3801 了解决这个复杂的问题,设计了这个库,它可以帮助您简化设计流程。使用一些简单的 API 可以轻松地在测试台中读取和写入标准位图文件 (.BMP)。并且,使用 AXI-Stream Video

2022-05-05 09:48:09 2500

2500 ARTIX-xlinx 版本FPGA 串口通信模块(含IP核)

2022-06-20 11:07:28 16

16 电子发烧友网站提供《TTL FPGA开源项目.zip》资料免费下载

2022-07-28 10:18:33 3

3 电子发烧友网站提供《树莓派计算模块开源项目.zip》资料免费下载

2022-08-05 09:25:58 1

1 电子发烧友网站提供《FPGA与MCU单片机的综合开发板开源.zip》资料免费下载

2022-08-09 09:41:41 2

2 电子发烧友网站提供《快充模块IP6505T开源分享.zip》资料免费下载

2022-08-10 14:33:38 10

10 电子发烧友网站提供《可远程监控蜂巢的开源项目.zip》资料免费下载

2022-11-17 09:24:33 0

0 Verilog 例化说明 1.什么是模块例化?为什么要例化? 模块例化可以理解成模块调用。对于一个 FPGA 工程,通常是由一个顶层模块与多个功能子模块组成,为了实现顶层模块与子模块的连接,需要进行

2022-12-12 09:50:06 5338

5338 一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块有交互联系的现存电路或激励信号源。

2023-02-02 10:03:38 12464

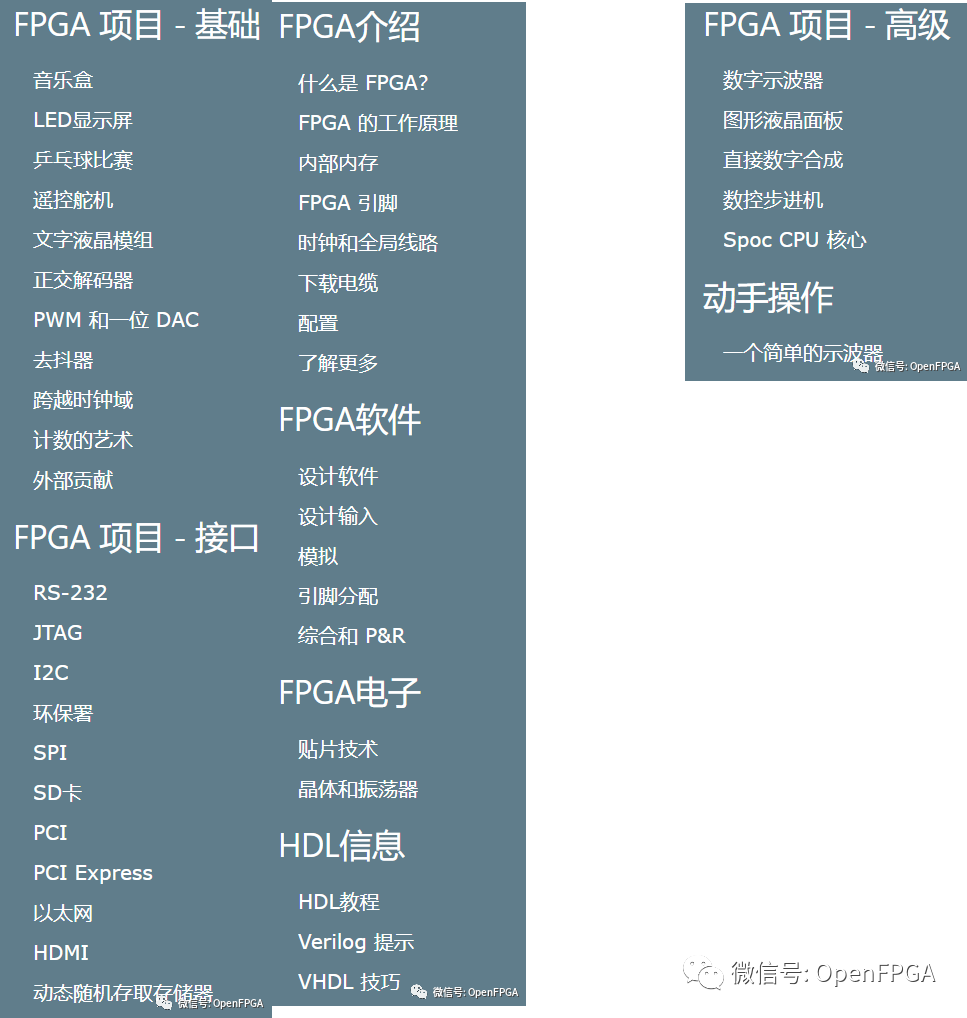

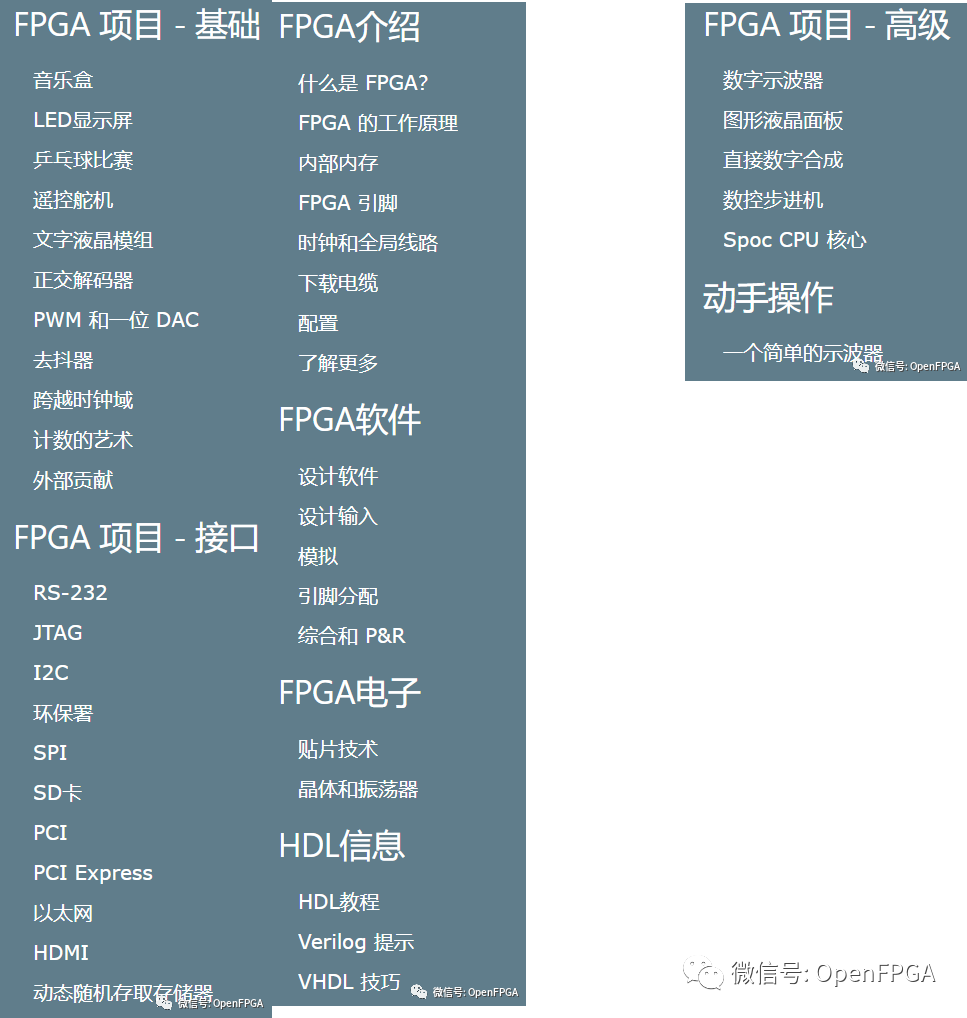

12464 FPGA 项目使用一种称为 Verilog 的语言,您需要学习它才能理解项目。但是通过此处显示的示例以及其他可用的在线资源,这并不太难。

2023-04-06 14:33:10 1692

1692

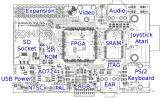

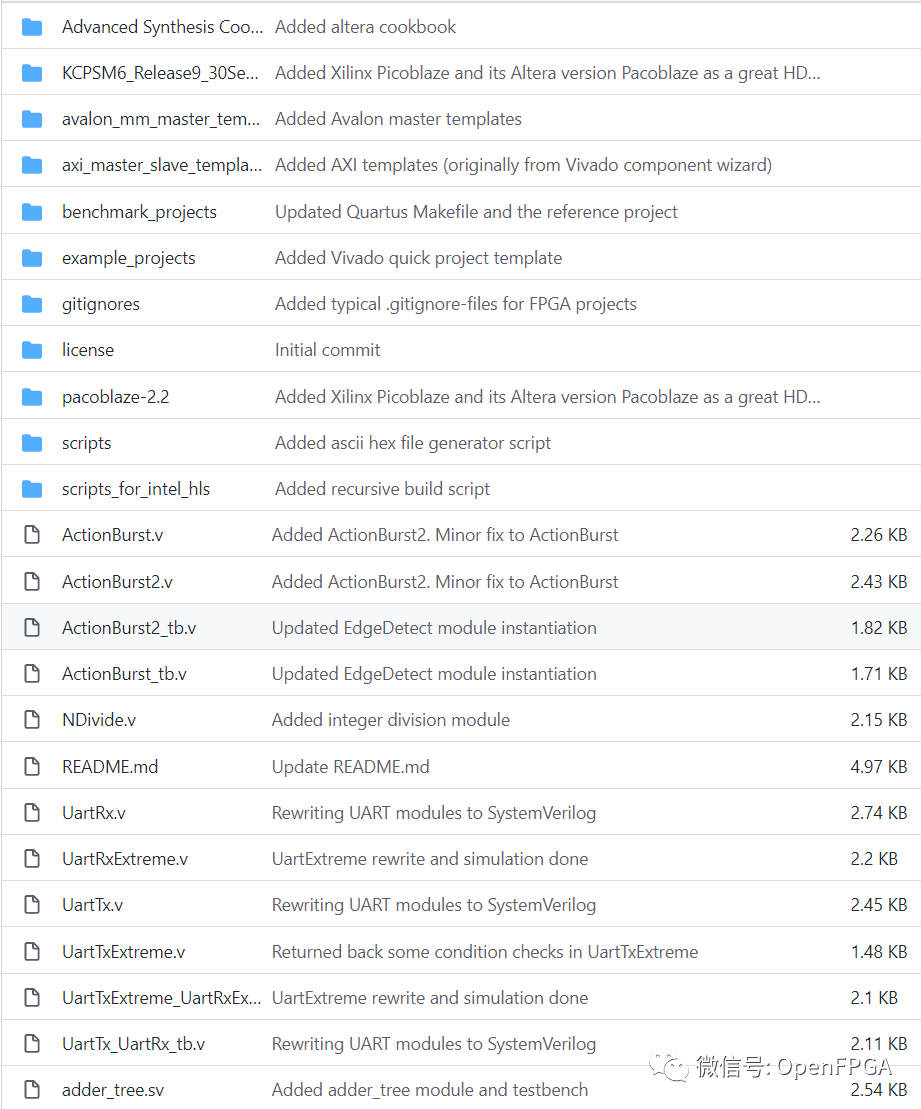

一直想做一个可以供大家学习、使用的开源IP库,类似OpenCores,OC上IP在领域内的IP很少,通用性强一点,所以作为OC的“补充”,所以做了一个开源IP库,

2023-05-06 09:16:08 1606

1606

本文是本系列的第三篇,本文主要介绍FPGA常用运算模块-乘加器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:17:12 2959

2959

本文是本系列的第四篇,本文主要介绍FPGA常用运算模块-除法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:20:45 5431

5431

本文是本系列的第五篇,本文主要介绍FPGA常用运算模块-复数乘法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:23:28 4135

4135

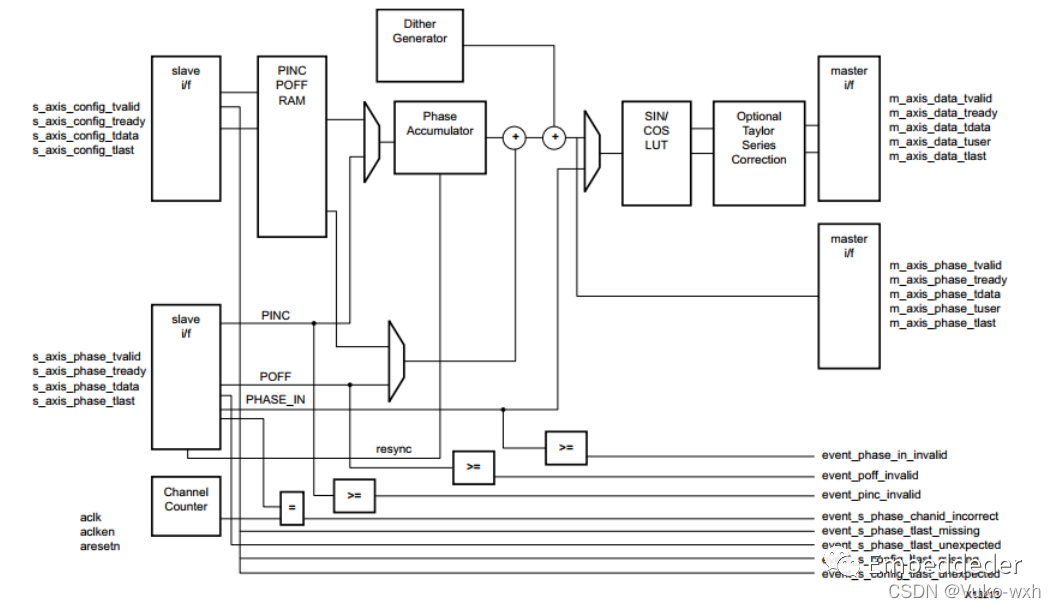

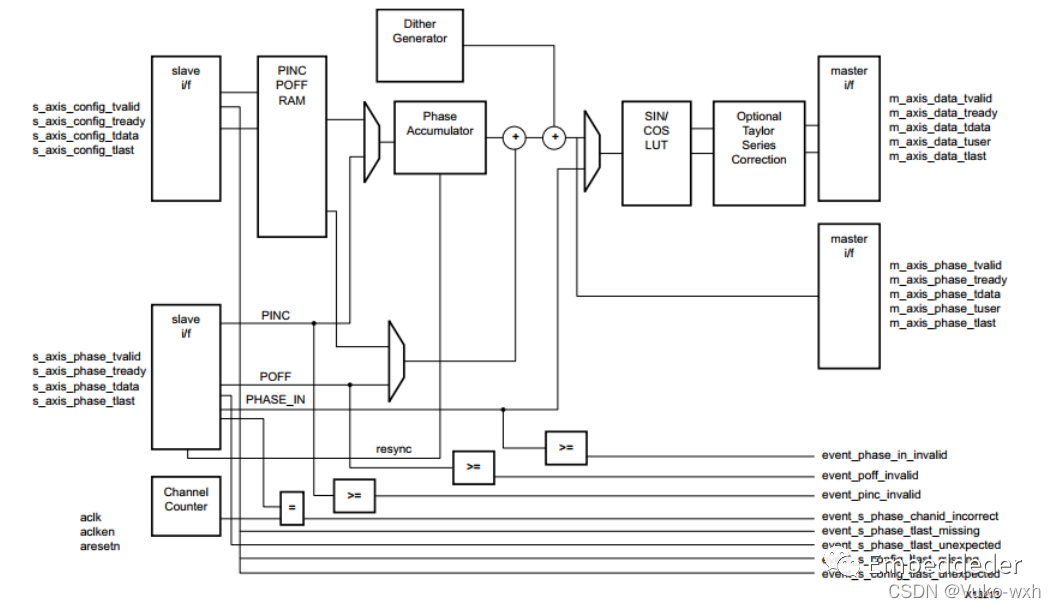

本文是本系列的第六篇,本文主要介绍FPGA常用运算模块-DDS信号发生器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-24 10:37:18 7398

7398

建立用于RTL综合的Verilog标准化子集。他是贝尔实验室所开发的ArchSyn综合系统的主要设计者之一。他曾为AT&T和Lucent的许多设计师讲授Verilog HDL语言和Verilog HDL综合课程。

2023-05-26 16:59:30 2182

2182

《优秀的IC/FPGA开源项目》是新开的系列,旨在介绍单一项目,会比《优秀的 Verilog/FPGA开源项目》内容介绍更加详细,包括但不限于综合、上板测试等。两者相辅相成,互补互充。

2023-06-09 09:42:41 3531

3531

电子发烧友网站提供《可缓解潮热症状的开源项目.zip》资料免费下载

2023-07-03 10:15:11 0

0 FPGA IP核(Intellectual Property core)是指在可编程逻辑器件(Field-Programmable Gate Array,FPGA)中使用的可复用的设计模块或功能片段。它们是预先编写好的硬件设计代码,可以在FPGA芯片上实现特定的功能。

2023-07-03 17:13:28 8969

8969 IP(Intellectual Property)是知识产权的意思,半导体行业的IP是“用于ASIC或FPGA中的预先设计好的电路功能模块”。一些常用的复杂的功能模块(如FIFO、RAM、FIR

2023-08-22 15:04:43 7796

7796

Hello,大家好,之前给大家分享了大约一百多个关于FPGA的开源项目,涉及PCIe、网络、RISC-V、视频编码等等,这次给大家带来的是不枯燥的娱乐项目,主要偏向老的游戏内核使用FPGA进行硬解,涉及的内核数不胜数,主要目标是高的可实现性及复现性。

2024-01-10 10:54:24 2672

2672

FPGA(现场可编程逻辑门阵列)开发主要使用的编程语言是硬件描述语言(HDL),其中Verilog是最常用的编程语言之一。而C语言通常用于传统的软件编程,与FPGA的硬件编程有所区别。

2024-03-27 14:38:14 3907

3907 Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及Verilog FPGA开发

2024-12-17 09:50:06 1630

1630 /prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 项目落后于计划,12% 的项目落后计划 50% 以上。 为此,很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法。

2025-01-15 10:47:37 1246

1246

电子发烧友App

电子发烧友App

评论