SystemVerilog常用可综合IP模块库

想拥有自己的SystemVerilog IP库吗?设计时一个快捷键就能集成到自己的设计,酷炫的设计你也可以拥有!

每个公司应该都会维护属于自己公司风格的IP库,作为个人学习或者持续使用的方式,这种方法很有用。今天肯定不是分享我司的IP库,而是一个开源库,每个人都可以使用、维护或者修改,当然作为学习(多人维护)也是不可多得的资料。把该库集成到自己常用的文本编辑器(SublimeVScodeVim等等)可以很快完成代码设计。

简介

这是verilog/systemverilog 可综合模块的集合。

所有代码在典型的 FPGA 和主流 FPGA 供应商中都具有高度可重用性。

本项目是几个常用可综合模块集合的集合,下面分别介绍这些项目。

工程链接

❝https://github.com/suisuisi/basic_systemverilog

详细介绍

basic_verilog

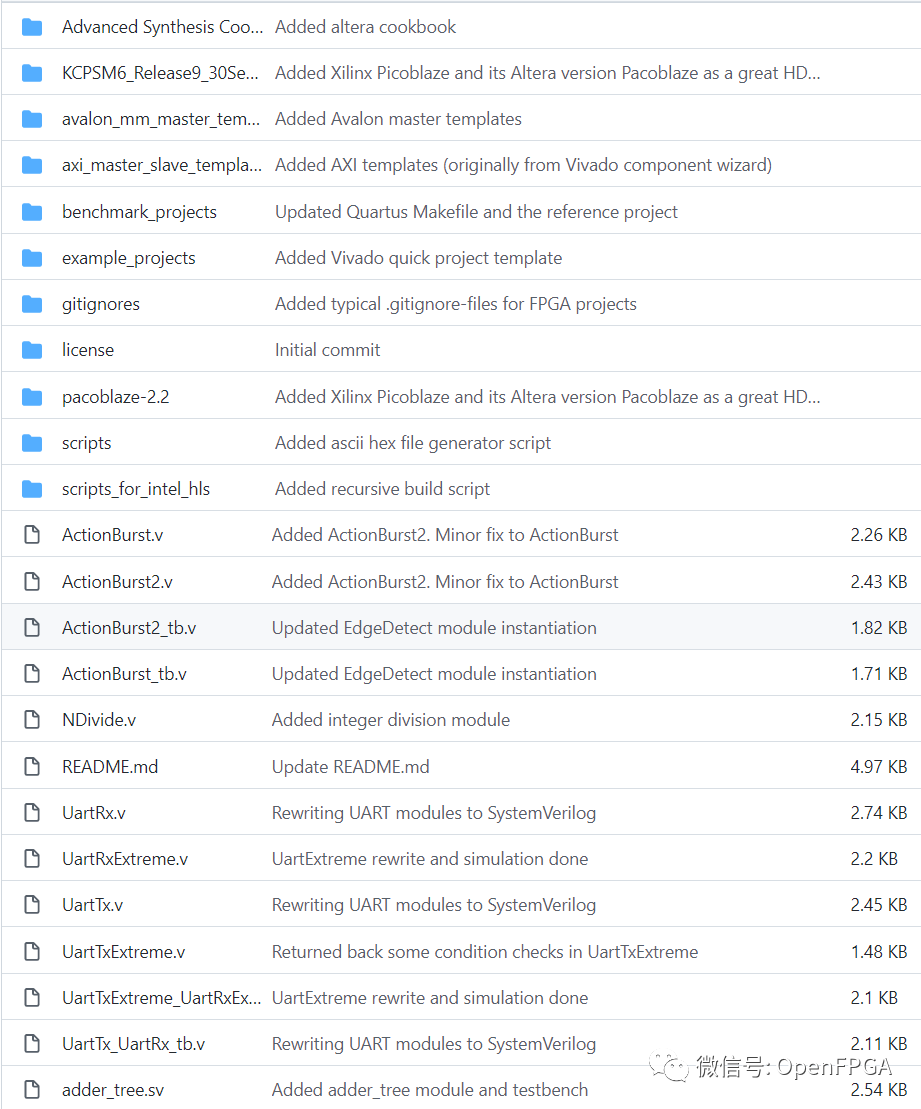

文件夹外的文件根据文件名很容易判断其用途,下面着重介绍文件夹内部文件:

| 目录 | 描述 |

|---|---|

| Advanced Synthesis Cookbook/ | Altera cookbook中的有用代码 |

| KCPSM6_Release9_30Sept14/ | Xilinx 的 Picoblaze 软处理器 |

| pacoblaze-2.2/ | 适用于 Altera 器件的 Picoblaze 版本 |

| example_projects/ | FPGA 项目示例 |

| benchmark_projects/ | 多种 FPGA 类型的编译时间基准 |

| scripts/ | 有用的 TCL 脚本 |

注1:cookbook:类似技巧大全的意思

这里还有一个TCL脚本文件,再简单介绍一下:

| 脚本 | 描述 |

|---|---|

| scripts/allow_undefined_ports.tcl | 允许为 Vivado IDE 生成带有未定义引脚的测试项目 |

| scripts/compile_quartus.tcl | Quartus IDE 中用于命令行项目编译的样板脚本 |

| scripts/convert_sof_to_jam.bat | Altera/Intel FPGA 配置文件转换器 |

| scripts/convert_sof_to_rbf.bat | 另一个 Altera/Intel FPGA 配置文件转换器 |

| scripts/iverilog_compile.tcl | 使用 iverilog 工具编译 Verilog 源代码并在 gtkwave 工具中运行模拟的完整脚本 |

| scripts/modelsim_compile.tclModelsim | 无项目模式编译脚本 |

| scripts/post_flow_quartus.tcl | 英特尔 Quartus IDE 的自定义报告或报告分析 |

| scripts/post_flow_vivado.tcl | Xilinx Vivado IDE 的自定义报告或报告分析 |

| scripts/program_all.bat | Altera/Intel FPGA 的命令行编程器示例 |

| scripts/project_version_auto_increment.tcl | Quartus IDE 的项目版本自动增量脚本 |

| scripts/quartus_system_console_init.tcl | 通过 JTAG-to-Avalon-MM 桥 IP 读/写 Avalon-MM 的初始化脚本 |

| scripts/set_project_directory.tcl | 更改当前目录以匹配 Vivado IDE 中的项目目录 |

| scripts/write_avalon_mm_from_file.tcl | 通过 JTAG-to-Avalon-MM 桥 IP 将二进制文件中的批量二进制数据写入 Avalon-MM |

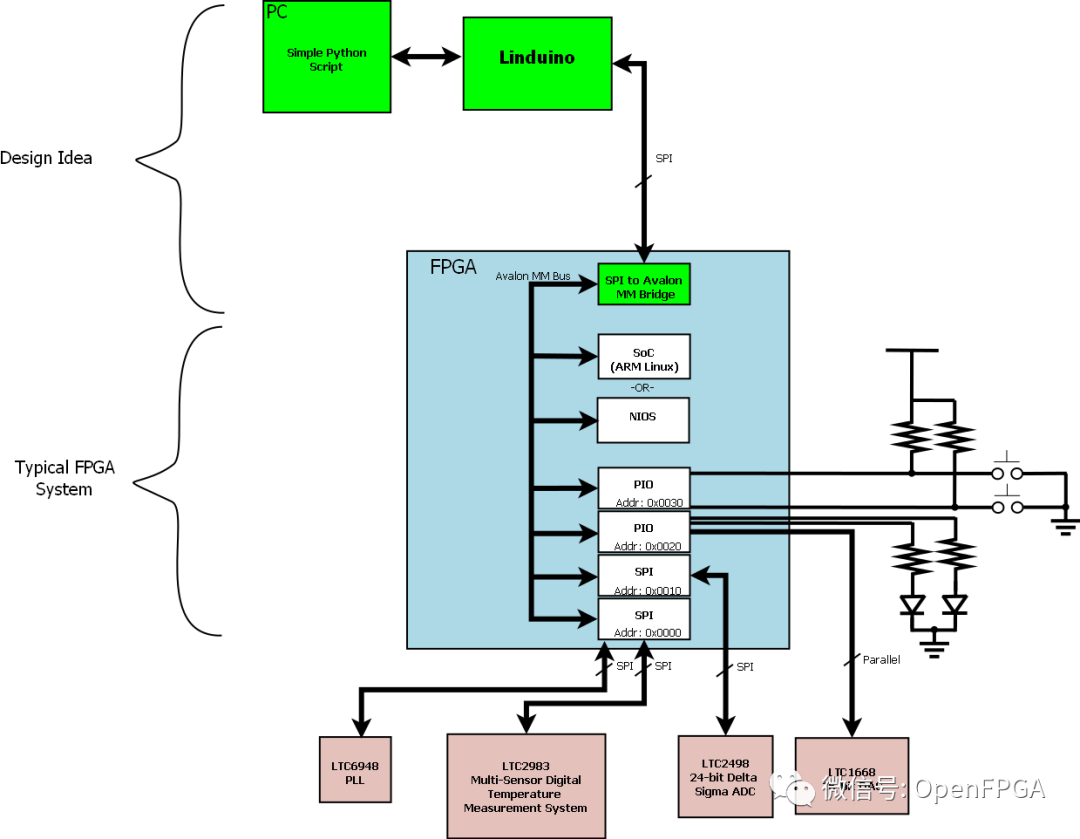

注2:Avalon:ALTERA公司FPGA内部使用的总线,下图是典型Altera FPGA系统

其他模块说明

| 脚本 | 描述 |

|---|---|

| ActionBurst.v | 多通道一次性触发模块 |

| ActionBurst2.v | 可变步长的多通道一次性触发 |

| adder_tree.sv | 将多个值并行相加 |

| bin2gray.sv | 格雷码到二进制转换器 |

| bin2pos.sv | 将二进制编码值转换为one-hot代码 |

| clk_divider.sv | 宽参考时钟分频器 |

| debounce.v | 输入按钮的两周期去抖动 |

| delay.sv | 用于产生静态延迟或跨时钟域同步的有用模块 |

| dynamic_delay.sv | 任意输入信号的动态延迟 |

| edge_detect.sv | 组合边沿检测器,在每个信号边沿上提供一个滴答脉冲 |

| lifo.sv | 单时钟 LIFO 缓冲器(堆栈)实现 |

| NDivide.v | 原始整数除法器 |

| prbs_gen_chk.sv | PRBS 模式生成器或检查器 |

| pulse_gen.sv | 产生具有给定宽度和延迟的脉冲 |

| spi_master.sv | 通用spi主模块 |

| UartRx.v | 简单明了的 UART 接收器 |

| UARTTX.v | 简单明了的 UART 发送器 |

| uart_rx_shifter.sv | 类似 UART 的接收器移位器,用于 FPGA 内部或 FPGA 之间的简单同步消息传递 |

| uart_rx_shifter.sv | 类似 UART 的接收器移位器,用于 FPGA 内部或 FPGA 之间的简单同步消息传递 |

| UartRxExtreme.v | 极小的 UART 接收器实现 |

| UartTxExtreme.v | 极小的 UART 发送器实现 |

| ... | ... |

generic_systemverilog_designs_library

- binary_counter

SystemVerilog 中具有异步复位的 n 位二进制计数器。

- binary_to_gray

SystemVerilog中的n位二进制到格雷码组合转换器电路。

- demultiplexer

具有宽度和输出端口数量参数化的解复用器。

- full_adder

SystemVerilog 中的 n 位全加器

- full_subtractor

SystemVerilog 中的 n 位全减法器

- gray_counter

使用 SystemVerilog 中的二进制计数器和二进制到格雷码组合转换器电路实现的具有异步复位的 n 位格雷码计数器。

- multiplexer

具有宽度和输入端口数量参数化的多路复用器。

SvLibDR

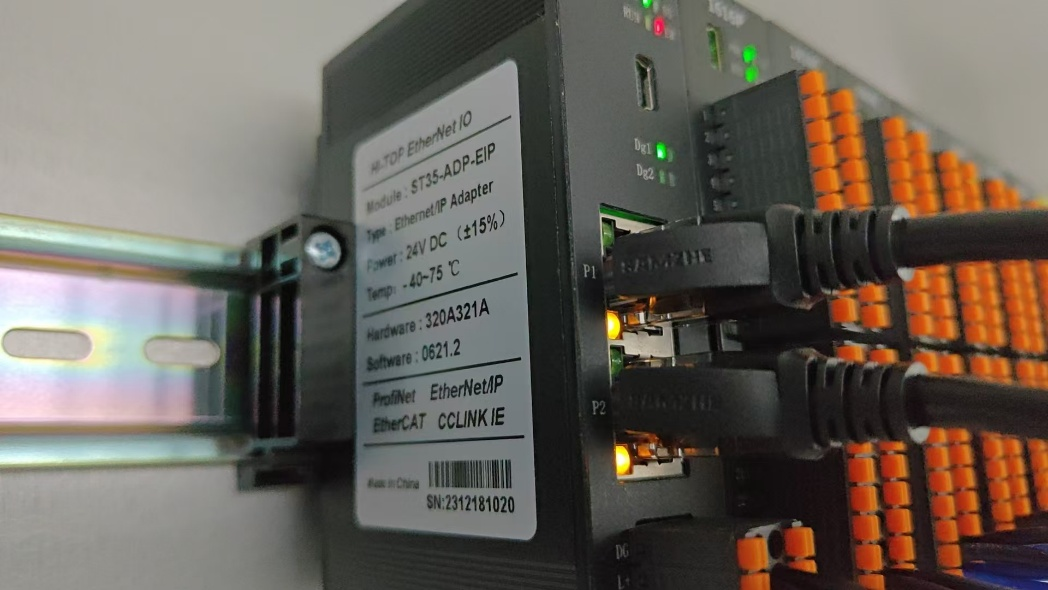

包括串口和SPI接口的可综合IP模块

SystemVerilog-Bitmap-Library-AXI-Image-VIP

描述

要验证视频或图像处理 IP,可能需要将真实图像读取到设计中,并通过接口发送其数据。然后,从界面获取输出,并将其转换为新图像,保存或比较。

为了解决这个复杂的问题,设计了这个库,它可以帮助您简化设计流程。使用一些简单的 API 可以轻松地在测试台中读取和写入标准位图文件 (.BMP)。并且,使用 AXI-Stream Video Image VIP,可以轻松地将图像发送到与 Xilinx 用户指南 UG934 兼容的标准 AXI-Stream 视频接口,从输出接口接收图像并保存。

位图处理库可以通过 System Verilog 将 Windows 位图文件 (.BMP) 读取和写入位数组(虚拟内存),以进行 IP 验证。该库支持 24 位和 32 位位图读入和 32 位位图写出。

使用位图处理库的 AXI-Stream Video Image VIP。“axi_stream_video_image_in_vip”IP 可以将位图文件读入内存,并通过 AXI-Stream 视频接口(在 Xilinx 用户指南 UG934 中定义)发送。而“axi_stream_video_image_out_vip”IP可以监控一个AXI-Stream接口,获取在接口上传输的帧并保存到位图文件中。

一般信息

支持的位图:

输入:24-bpp/32-bpp RGB/RGBA 位图输出:32-bpp RGBA 位图

这个库的优势

- 简单的 API

- 开源

- 与流行的 EDA 工具兼容(在 Modelsim 和 Qustasim 上测试)

包中的文件

| 文件 | 描述 |

|---|---|

| bitmap_processing.sv | 位图处理库。 |

| axi_stream_video_image.sv | AXI 流视频图像库(用于回调类)。 |

| axi_stream_video_image_in_vip.sv | VIP 用于读取位图并将其发送到接口。 |

| axi_stream_video_image_out_vip.sv | VIP 用于监控界面并将图像保存为位图。 |

| axi_stream_video_image_example.sv | 如何使用 VIP 和库的简单示例。 |

关于包使用等详细信息,请查看项目介绍。

总结

今天只介绍了一个项目,这个项目可以给大家提供一个思路尤其对于没有工作或者刚入门不久的同行,自己在编写代码时要想着可继承性,这样在以后做类似项目时可以借用,并且长期维护一个代码对于这个模块的理解有很大帮助。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

审核编辑 :李倩

-

System

+关注

关注

0文章

166浏览量

38820 -

编辑器

+关注

关注

1文章

829浏览量

33061 -

模块库

+关注

关注

0文章

2浏览量

5151

原文标题:优秀的 Verilog/FPGA开源项目介绍(二十二)- SystemVerilog常用可综合IP模块库

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IP6162 集成隔离通信,可级联使用的光伏MPPT DC-DC

疆鸿智能Ethernet/IP转DeviceNet,库卡机器人智联枢纽,破壁协同高效智造

Profinet转Ethernet IP网关连接库卡机器人问答式精简配置指南

【「龙芯之光 自主可控处理器设计解析」阅读体验】--LoongArch逻辑综合、芯片设计

一文详解SystemC仿真库的编译

RDMA设计6:IP架构2

创客匠人创始人IP+AI万人大会次日:深度探讨AI时代IP价值重塑与可持续增长路径

50 欧姆、高 IP3、低噪声宽带增益模块 skyworksinc

华秋 KiCad 发行版 9.0.4 发布:属于您自己的云端器件库及模块电路库

零基础在智能硬件上克隆原神可莉实现桌面陪伴(提供人设提示词、知识库、固件下载)

SmartDV推出先进的H.264和H.265视频编码器和解码器IP

SystemVerilog常用可综合IP模块库

SystemVerilog常用可综合IP模块库

评论