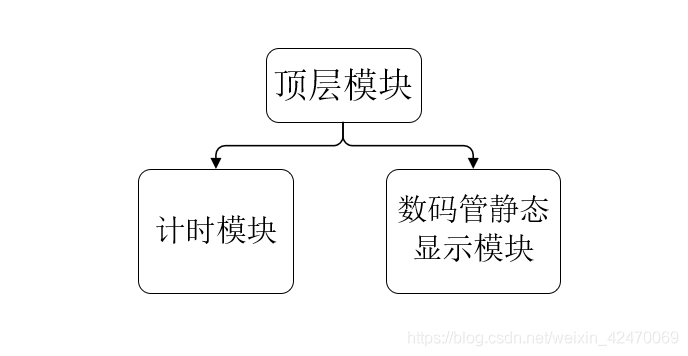

Verilog例化说明

1.什么是模块例化?为什么要例化?

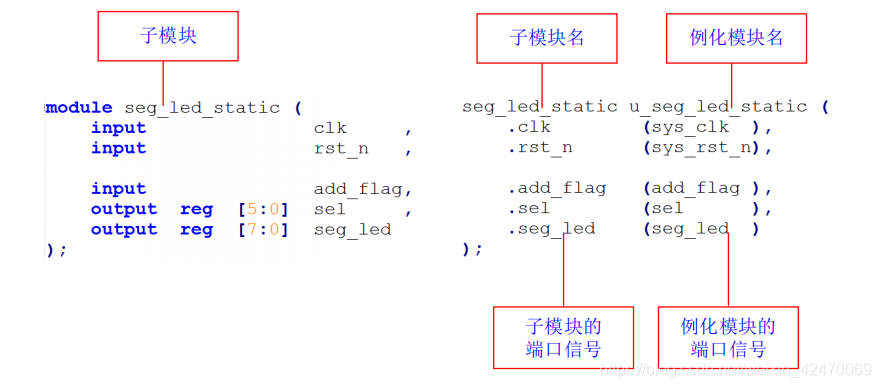

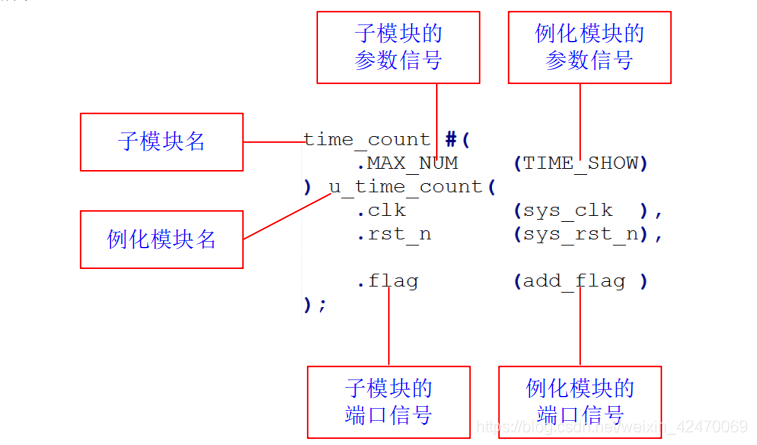

2.实例说明例化方法

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-Verilog例化说明

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22494浏览量

638991

原文标题:FPGA学习-Verilog例化说明

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

Verilog HDL语法学习笔记

Verilog HDL 语 言 最 初 是 作为 Gateway Design Automation 公 司 ( Gateway DesignAutomation 公司后来被著名的 Cadence Design Systems 公司收购)模拟器产品开发的硬件建模语言。

FPGA 入门必看:Verilog 与 VHDL 编程基础解析!

很多开发者第一次接触FPGA,都会有同样的疑问:FPGA是硬件,不是软件,怎么写程序?答案就是用硬件描述语言(HDL),最常用的就是Verilog和VHDL。今天,我们就带你入门,搞清楚FPG

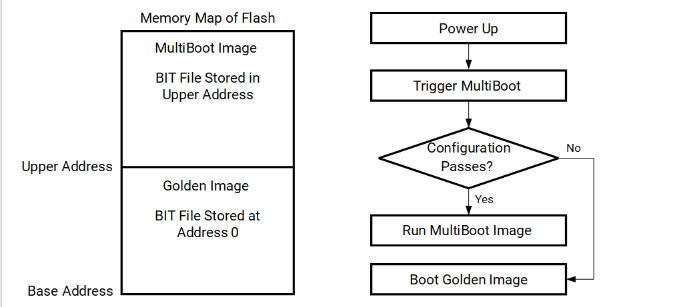

【ALINX 教程】FPGA Multiboot 功能实现——基于 ALINX Artix US+ AXAU25 开发板

至安全镜像(Golden Image)。 适用对象 已掌握 FPGA 基础开发(会写Verilog、会生成bitstream) 熟悉 Vivado 工程流程 对 FPGA 配置机制尚不深入,希望进入

如何使用FPGA实现SRIO通信协议

本例程详细介绍了如何在FPGA上实现Serial RapidIO(SRIO)通信协议,并通过Verilog语言进行编程设计。SRIO作为一种高速、低延迟的串行互连技术,在高性能计算和嵌入式系统中广

请问测试用例.verilog文件是怎么生成的呢?

在仿真时可以通过添加.verilog文件,直接读入ITCM中,从而在仿真时我们就可以知道处理器的运行结果,例如打印hello_world字样。

发表于 11-11 07:56

在verilog testbench中运行测试用例时,运行到make run_test出错怎么解决?

按照胡老师书上的在verilog testbench中运行测试用例时,在运行到make run_test步骤时出错,查了很多方案没有解决。

发表于 11-11 06:52

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

1.简述

首先感谢芯来开源了蜂鸟E203 risc-v处理器,提供了比较完整的工程环境、配套的软硬件。但是配套的FPGA板卡实在太贵,对于自费学习的来说是不小的学习成本,而且我也认为完备环境

发表于 10-31 08:46

蜂鸟E203移植到FPGA开发板前的IP核例化工作

和3.2768KHz低频时钟,在FPGA板上只有外部晶振提供时钟,因此需要例化clocking wizard IP核提供时钟,并且例化res

发表于 10-27 07:35

E203外设的例化与编译配置

外设,包括硬件例化、总线连接、底层开辟空间等一系列过程,同时需要在软件中配置地址、接口信号数据类型等,才能正常编译使外设运行相应的程序。接下来将以SHA256外设模块为例,介绍上述过程。

SHA即

发表于 10-24 07:14

Xilinx BRAM IP核配置及其例化

)的,所以通过合理分配例化BRAM的大小,可以提高片上block的利用率。

例化完成以后,进行综合,可以通过report utilization来查看资源消耗情况

可以看到使用的板子

发表于 10-24 06:10

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试,包括设计SRAM接口模块

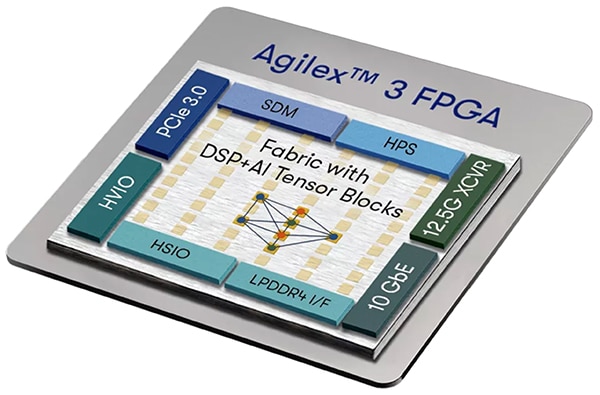

如何在资源受限型应用中使用 FPGA

的性能需求,同时在严格的功耗、尺寸和成本限制内运行。现代现场可编程门阵列 (FPGA) 可以满足这些相互竞争的需求。 本文回顾了为资源受限型应用选择 FPGA 时需要考虑的关键设计标准。然后,以 [Altera] 经过[功率和成本优化的

FPGA在机器学习中的具体应用

随着机器学习和人工智能技术的迅猛发展,传统的中央处理单元(CPU)和图形处理单元(GPU)已经无法满足高效处理大规模数据和复杂模型的需求。FPGA(现场可编程门阵列)作为一种灵活且高效的硬件加速平台

【高云GW5AT-LV60 开发套件试用体验】基于开发板进行深度学习实践,并尽量实现皮肤病理图片的识别

可以多看看。*附件:fpga_cnn.rar

相关文件都在里面了

探索了一阵子cnn,并且也跟着网上的一些开源的方案学习一些

比如这里的:# 一起学习用Verilog在

发表于 06-11 22:35

FPGA学习-Verilog例化说明

FPGA学习-Verilog例化说明

评论