大家好,又到了每日学习的时间了,今天我们来聊一聊基于FPGA的异步FIFO的实现。 一、FIFO简介 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通

2018-06-21 11:15:25 7148

7148

之前介绍了 SelectIO 逻辑资源,本篇咱们就聊一聊与SelectIO 逻辑资源水乳交融、相得益彰的另一个概念IO_FIFO。 1个IO_FIFO包括1个IN_FIFO 和1个OUT_FIFO

2020-11-29 10:08:00 3670

3670

FIFO是队列机制中最简单的,每个接口上只有一个FIFO队列,表面上看FIFO队列并没有提供什么QoS保证,甚至很多人认为FIFO严格意义上不算做一种队列技术,实则不然,FIFO是其它队列的基础

2022-07-10 09:22:00 2155

2155 FIFO (先入先出, First In First Out )存储器,在 FPGA 和数字 IC 设计中非常常用。 根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。

2023-06-27 10:24:37 3136

3136

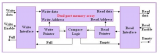

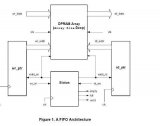

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于读操作和写操作

2023-09-11 09:12:23 1198

1198

FIFO自带的set_max_delay生效? 对于异步FIFO,复位信号的使用要特别注意,如下图所示。复位信号必须和wr_clk同步,如果异步,要在wr_clk时钟下同步释放,否则会出现数据无法写入

2023-11-02 09:25:01 2266

2266

最近加的群里面有些萌新在进行讨论**FIFO的深度**的时候,觉得 **FIFO的深度计算比较难以理解** 。所

2023-11-28 16:19:46 2024

2024

按照正常的思路,在前文完成前向时序优化和后向时序优化后,后面紧跟的应该是双向时序优化策略了,不过不急,需要先实现一下握手型同步FIFO。

2023-12-04 14:03:49 1473

1473

FIFO是一种先进先出数据缓存器,它与普通存储器的区别是没有外部读写地址线,使用起来非常简单,缺点是只能顺序读写,而不能随机读写。

2024-04-09 14:23:15 4603

4603

RTL8316E-CG

2023-03-29 21:41:56

RTL8382L-VB-CG

2023-03-29 21:46:25

同步FIFO代码已经写好了,但是怎么判断写入的数据和读出的数据是否一致呢?求代码

2016-04-26 15:58:34

我想问一下什么情况下需要用异步FIFO,什么情况下用同步FIFO?

2014-11-03 17:19:54

我试图了解专用线程和当前线程标志之间的差异,因为它涉及同步从FIFO读/写时序。AN6994表示,对于当前线程标志,存在两个周期延迟。它不指定读或写,虽然两个周期的延迟与同步从属读取时序图一致。如果

2019-05-07 12:17:40

位总线,同步--我想--,40mhz IFC时钟由FPGA提供脉冲时,SLWR有数据的饲料,等)。当我用cyconsole,我的设备出现,我在终点的报道,并且能够读取512个字节时,我做了一个大。我

2019-07-24 13:31:58

异步FIFO的读写时序。图9.72 异步FIFO实例功能框图本实例的异步FIFO与上一个实例的同步FIFO有别,这个异步FIFO不仅读写的位宽不同,读写的时钟也不同。异步FIFO对于跨时钟域的应用非常

2019-05-06 00:31:57

,就可以写入数据;对于输出端口来说,只要FIFO中还有数据,就可以读出数据。 写一侧的所有信号都同步于写时钟,读一侧的所有信号都同步于读时钟。 · 设计要求设计宽度为8、缓冲深度为256、输入速率为

2023-03-15 16:19:35

RAM,使用FPGA内部的寄存器和查找表搭建起来的RAM,当深度要求小于32的时候可以使用;Shift Register: 使用FIFO产生一个移位寄存器;Common clock: 指的就是同步

2023-04-11 20:50:21

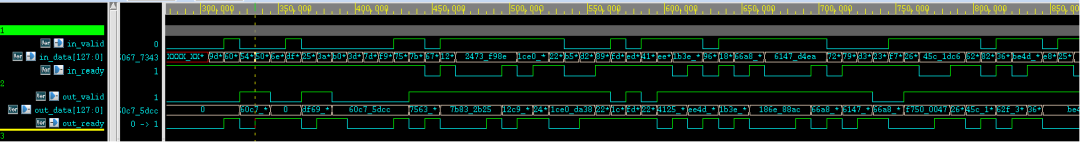

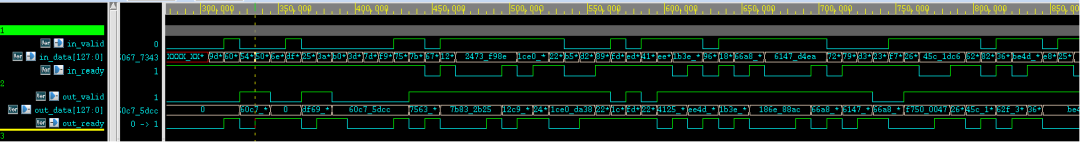

数据满标志位,fifo写满置1read读使能信号,高电平有效fifo_emptyfifo空标志位,空时置1clock时钟信号fifo_halffifo写数据达到8个,或读数据时,fifo数据小于8个2、仿真波形(一)连续写数据至fifo满(二)连续读数据至fifo空(三)边写边读三、实验代码

2016-11-07 00:18:04

入的指令先完成并引退,跟着才执行第二条指令。 1.什么是FIFO? FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成

2022-02-16 06:55:41

完所有寄存器之后拉高TXENABLE信号,输入数据变为正弦信号,同时给SYNC信号一个上升沿用于同步3482内部的PLL。

在以上配置和时序的情况下,每次FIFO都会冲突,复位后还是冲突,请各位朋友帮我分析一下原因,在线等,比较急,谢谢!

2024-12-23 06:02:20

异步fifo是用于跨时域时钟传输的,但是同步fifo做缓存我就不是很理解了,到底这个缓存是什么意思,这样一进一出,不是数据的传输吗,为什么加个fifo,还有,如果是两组视频流传输,在切换的过程中如何能保证无缝切换?希望哪位好心人帮我解答一下

2013-08-27 19:23:36

大小包了,但我的理解是,最好是有一个更快的USB端,为了避免全FIFO的事件和数据丢失(没有其他缓冲区之间)。我说的对吗?最后一个问题:当FIFO从全空和旗帜去断言,这是标志变化同步或异步发生ifclk

2019-04-19 11:19:17

这是网上比较流行的一个异步fifo方案,但是fifo的空满判断不是应该是立即的吗,加上同步器之后变成写指针要延时两个读周期再去个读指针做空比较,而读指针要延时两个写周期再去和写指针做满比较,这样虽然可以避免亚稳态之类的问题,可是这个延时对总体的空满判断没有影响吗,如果没有影响是怎么做到的呢,求解

2016-07-24 16:25:33

FPGA片内异步FIFO的读写时序。图9.72 异步FIFO实例功能框图本实例的异步FIFO与上一个实例的同步FIFO有别,这个异步FIFO不仅读写的位宽不同,读写的时钟也不同。异步FIFO对于跨时钟域

2018-08-28 09:39:16

来决定需要哪些信号。点下一步设置两个内容,一个是FIFO的输出的两种形式,一种是传统的同步方式,即你在有readreq='1'的一个周期后才能读取数取,另一种为show ahead,即为你在

2012-03-27 12:28:32

现在有10个fifo,当其中任何一个满512字节就进行数据处理,应该如何实现呢?多个FIFO的数据输出data_out连接在一起,然后连接到数据处理模块(也是FPGA的一个逻辑模块)的data_in行不行?

2012-09-14 15:11:37

我们正试图使用 FX3 同步从属 fifo 模式通过 FPGA 传输传感器数据。

USB type-C 接口需要选择一个多路复用器来决定使用哪一边的 USB。 因此,我们考虑使用 FX3 GPIO

2024-07-17 08:04:35

您好!我读了AN694.4.PDF的数据表。在同步从属FIFO写序列中,如果必须使用部分标志以不丢失数据,则从SLWRγ到标记有3个周期延迟。如何用GPIF设计器修改代码?谢谢! 以上来自于百度

2019-04-10 14:32:05

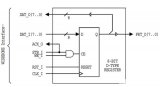

如图所示的异步FIFO,个人觉得在读写时钟同步时会产生两个时钟周期的延时,如果读写时钟频率相差不大,某一时刻读写指针相等,当写指针同步到读模块时会产生延时,实际同步到读模块的写指针是两个时钟周期之前的,这样就不会产生空满信号,要两个周期之后才能产生空满信号,结果是写溢出或读空

2015-08-29 18:30:49

我自己写了一个FIFO,但是我总是不理解Paper中讲的要把读写指针同步,如果我将两个不同时钟产生的读写地址直接比较,产生读写,请问这个亚稳态是怎么产生的,不要复制网上的那些东西,我都看了买就是不太

2016-04-11 23:13:45

你好我想实现一个同步FIFO 2点有两个输出eindpoints和两个端点,我创造的这些enpoints描述符中并创建为每个端点的DMA通道,但我仍然找不到工作。我怎么能用2在端点的端点,实现Slave FIFO亲切问候Ragy;

2019-09-20 14:06:58

急需同步FIFO,我这有一个,但是仿真图不对,我也不知道是不是代码有问题。

2015-03-15 09:25:06

也就是说用一个25M频率的FIFO写入数据,用另一个100M(或者不同频)的FIFO读出数据。该如何实现呢?不使用异步FIFO

2020-12-03 20:47:22

我准备用24位的A/D采集地震信号(加速度芯片采集的加速度值),信号先存入FIFO中,对信号设置一个阈值,当数值超过阈值时报警,并记录报警前30秒地震数据,报警后10秒(30秒也行)的数据。没有报警

2011-10-20 16:37:04

的缩写,就是先入先出的意思,按照我的理解就是,先进去的数据先出,例如一个数组的高位先进,那么读出来的时候也就高位先出。下面是百度百科的解释。FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一

2014-08-21 15:35:07

1.什么是FIFO?FIFO是英文First In First Out 的缩写,是一种先进先出的数

2009-07-22 16:00:48 0

0 A7105 Reference code for FIFO mode:1. 简介这文件系对 RF chip -A7105 FIFO mode 做一简单的应用范程序,供使用者能够快速应用这 RF chip。2. 系统概述本范程序使用简单的跳频(frequency hop

2009-09-29 10:22:17 37

37 设计一个FIFO是ASIC设计者遇到的最普遍的问题之一。本文着重介绍怎样设计FIFO——这是一个看似简单却很复杂的任务。一开始,要注意,FIFO通常用于时钟域的过渡,是双时钟设计

2009-10-15 08:44:35 94

94 摘要:使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FUFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路

2006-03-24 12:58:33 1660

1660

什么是fifo (First Input First Output,先入先出队列)这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。1.什么是FIFO

2007-12-20 13:51:59 13167

13167 RTL,RTL是什么意思

电阻晶体管逻辑电路

RTL电路-电

2010-03-08 11:19:22 14703

14703 本文采用VHDL描述语言,充分利用Xilinx公司Spartan II FPGA的系统资源,设计实现了一种非对称同步FIFO,它不仅提供数据缓冲,而且能进行数据总线宽度的转换。

2011-01-13 11:33:43 2240

2240 设计可复用的基本要求是RTL 代码可移植。通常的软件工程指导原则在RTL 编码时也适用。类似软件开发,基本的编码指导原则要求RTL 代码简单、结构化和规则化。这样的代码也易于综合

2011-12-24 00:46:00 32

32 在这个系列的上一篇文章“HighLevel Synthesis(HLS) 从一个最简单的fir滤波器开始1”中,我们从一个最简单的FIR滤波器,介绍了HLS是如何把C映射成RTL代码的一些基本细节

2017-02-08 05:10:34 743

743 FIFO 很重要,之前参加的各类电子公司的逻辑设计的笔试几乎都会考到。

2017-02-11 06:51:50 5203

5203

RTL8139C RTL8139C-LF RTL8139CL RTL8139CL-LF

2017-10-25 14:48:54 23

23 (每个数据的位宽) FIFO有同步和异步两种,同步即读写时钟相同,异步即读写时钟不相同 同步FIFO用的少,可以作为数据缓存 异步FIFO可以解决跨时钟域的问题,在应用时需根据实际情况考虑好fifo深度即可 本次要设计一个异步FIFO,深度为8,位宽也是8。

2017-11-15 12:52:41 9176

9176

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

2018-07-17 08:33:00 8860

8860

上集成的高速FIFO实现采集数据的高速缓存并通过对高速FIFO的读写操作实现总线同步数据传输,提高数据的传输速率。

2018-07-12 09:06:00 6077

6077

FIFO( First In First Out)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性。

2017-12-06 14:29:31 11098

11098

在现代的集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟。多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(Firstln F irsto ut)是解决这个

2018-02-07 14:22:54 0

0 异步FIFO(Fist-In-First-Out)是一种先入先出的数据缓冲器[1]。由于可以很好地解决跨时钟域问题和不同模块之间的速度匹配问题,而被广泛应用于全局异步局部同步[2](Globally

2018-06-19 15:34:00 3780

3780

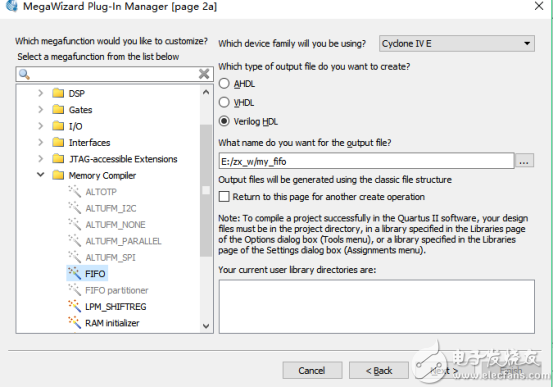

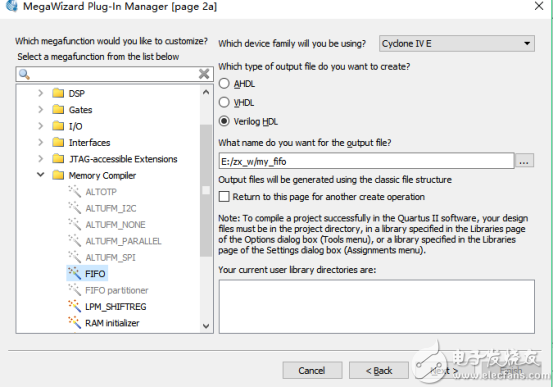

配置FIFO的方法有两种:

一种是通过QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中选择FIFO参数编辑器来搭建自己需要的FIFO,这是自动生成FIFO的方法

2018-07-20 08:00:00 17

17 前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示。该从

2018-07-31 09:11:30 5058

5058

设计背景: First Input First Output的缩写,先入先出队列,这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。FIFO是队列机制中最简单的,每个接口

2018-08-07 11:11:15 5706

5706

异步FIFO广泛应用于计算机网络工业中进行异步数据传送,这里的异步是指发送用一种速率而接收用另一速率,因此异步FIFO有两个不同的时钟,一个为读同步时钟,一个为写同步时钟。

2019-06-11 08:00:00 3853

3853

FIFO队列具有处理简单,开销小的优点。但FIFO不区分报文类型,采用尽力而为的转发模式,使对时间敏感的实时应用(如VoIP)的延迟得不到保证,关键业务的带宽也不能得到保证。

2019-11-29 07:10:00 2159

2159 根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2019-11-29 07:08:00 2265

2265 FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼写为FirstIn First Out,即先进先出。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据

2021-03-12 16:30:48 4047

4047

1.定义 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序

2021-04-09 17:31:42 6216

6216

通过在MEMS信号处理电路中设计一个异步结构的FIFO,可以有效地降低系统对MEMS的频繁访问。设计一个具有多种工作模

2021-04-15 11:23:37 2363

2363

是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。 FIFO是队列机制中最简单的,每个接口上只有一个FIFO队列,表

2021-05-29 09:10:49 32947

32947 异步FIFO通过比较读写地址进行满空判断,但是读写地址属于不同的时钟域,所以在比较之前需要先将读写地址进行同步处理,将写地址同步到读时钟域再和读地址比较进行FIFO空状态判断(同步后的写地址一

2021-08-04 14:05:21 5131

5131 入的指令先完成并引退,跟着才执行第二条指令。 1.什么是FIFO? FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成

2021-12-17 18:29:31 10

10 进行读写。如果这样的话,FIFO就变成了一个“存储器件”,而不是一个“缓存器件”,对于FIFO的这种用法无疑是毫无意义的。

2022-02-26 17:41:52 4177

4177

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的。

2022-03-08 11:06:12 5714

5714

在FPGA中对图像的一行数据进行缓存时,可以采用FIFO这一结构,如上图所示,新一行图像数据流入到FIFO1中,FIFO1中会对图像数据进行缓存,当FIFO1中缓存有一行图像数据时,在下一行图像数据来临的时候,将FIFO1中缓存的图像数据读出,并传递给下一个FIFO

2022-05-10 09:59:29 4734

4734 在STM32上移植的一个稳定可靠的FIFO,可移植到其他的STM32的单片机上。

2022-09-26 16:08:43 6

6 FIFO的分类根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2022-11-01 09:57:08 2857

2857 同步FIFO的意思是说FIFO的读写时钟是同一个时钟,不同于异步FIFO,异步FIFO的读写时钟是完全异步的。同步FIFO的对外接口包括时钟,清零,读请求,写请求,数据输入总线,数据输出总线,空以及满信号。

2022-11-01 09:58:16 2461

2461 FIFO 是我们设计中常用的工具,因为它们使我们能够在进行信号和图像处理时缓冲数据。我们还使用异步FIFO来处理数据总线的时钟域交叉问题。

2022-11-04 09:14:11 6431

6431 电子发烧友网站提供《设计一个简单的SOC.zip》资料免费下载

2022-11-16 11:08:27 0

0 和写入数据(对于大型数据存储,在性能上必然缓慢),其数据地址是由内部读写指针自动加一完成的,不能像普通的存储器一样,由地址线决定读取或者写入某个特定地址的数据,按读写是否为相同时钟域分为同步和异步FIFO,这里主要介绍异步FIFO,主要用于跨时钟域传输数据。 FIFO是

2022-12-12 14:17:41 5421

5421 方案介绍该方案展示了如何制作一个简单的 Arduino 示波器。示波器可显示的最大信号频率为 20 kHz,不带分压器时最大输入电压为 5 V。示波器由四个按钮控制:- “HOLD”按钮 - 用于

2022-12-23 10:45:29 9

9 FIFO用于为匹配读写速度而设置的数据缓冲buffer,当读写时钟异步时,就是异步FIFO。多bit的数据信号,并不是直接从写时钟域同步到读时钟域的。

2023-01-01 16:48:00 1857

1857 FIFO(First In First Out )先入先出存储器,在FPG设计中常用于跨时钟域的处理,FIFO可简单分为同步FIFO和异步FIFO。

2023-04-25 15:55:28 5975

5975

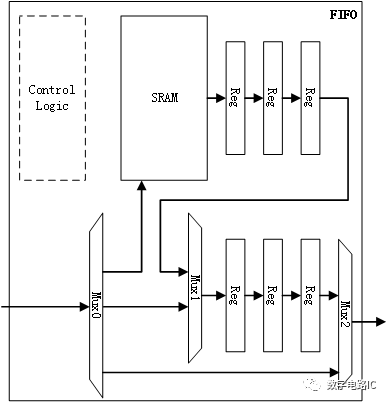

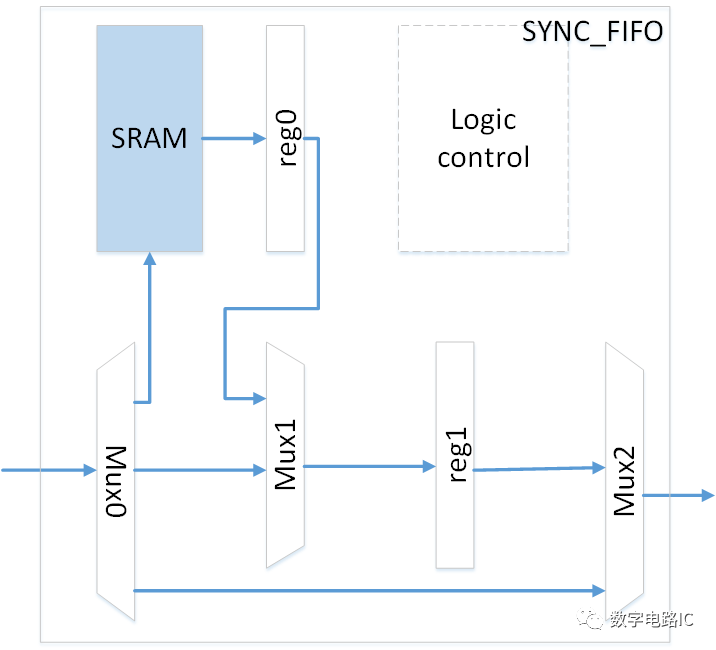

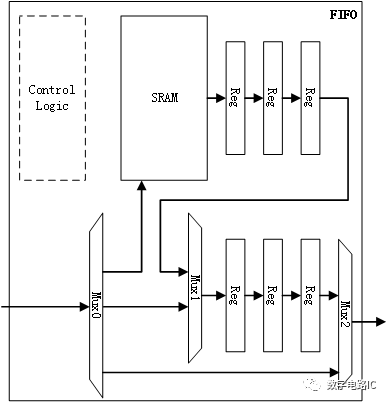

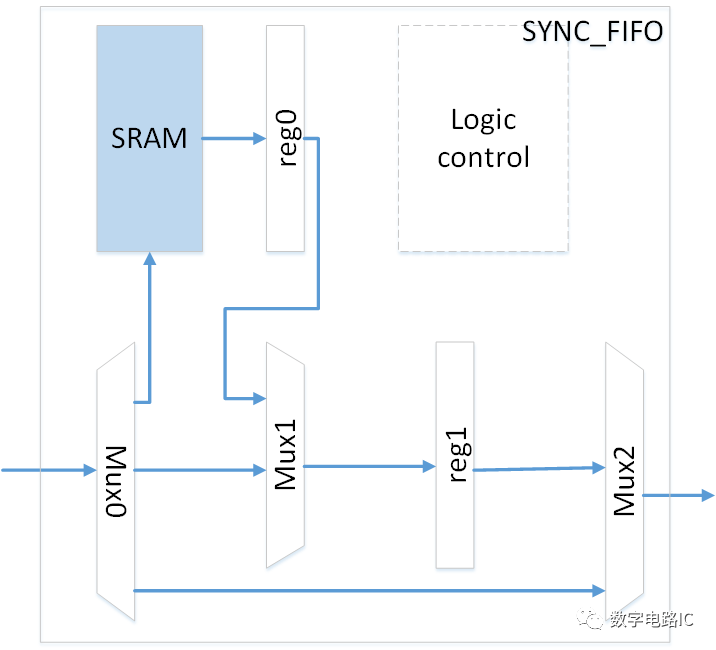

今天咱们开始聊聊FIFO的设计。FIFO是一个数字电路中常见的模块,主要作用是数据产生端和接受端在短期内速率不匹配时作为数据缓存。FIFO是指First In, First Out,即先进先出,跟大家排队一样。越早排队的人排在越前面,轮到他的次序也越早,所以FIFO有些时候也被称为队列queue。

2023-05-04 15:48:20 1504

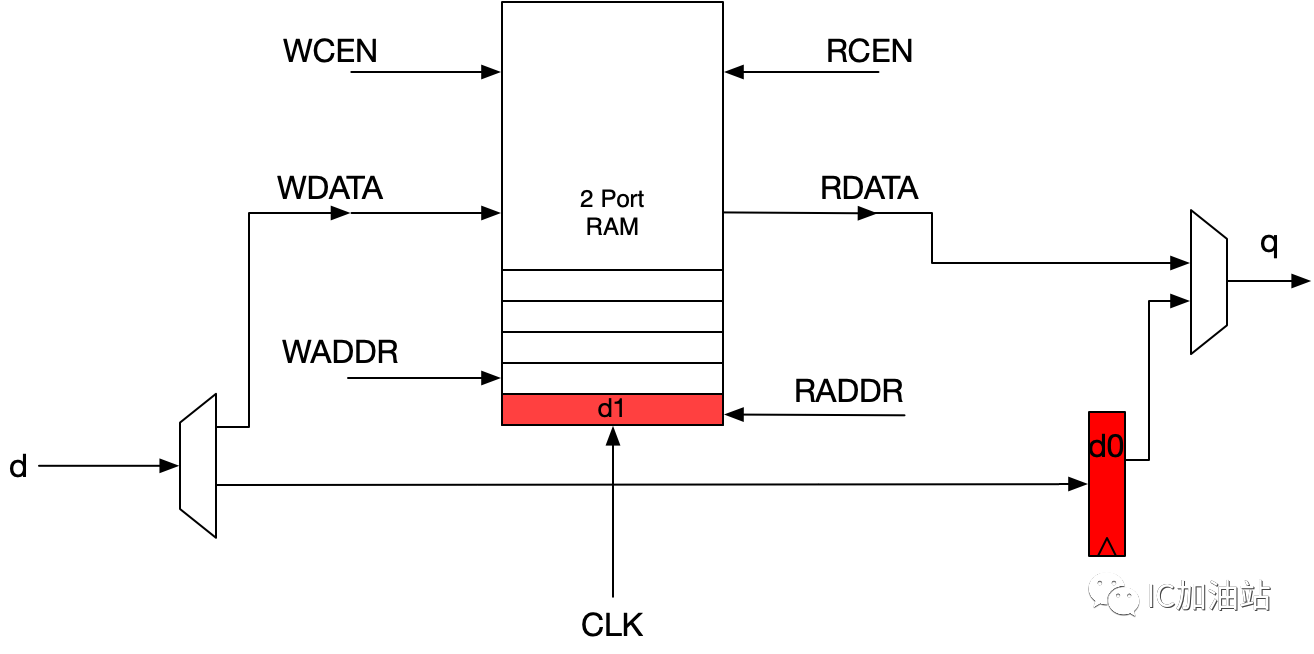

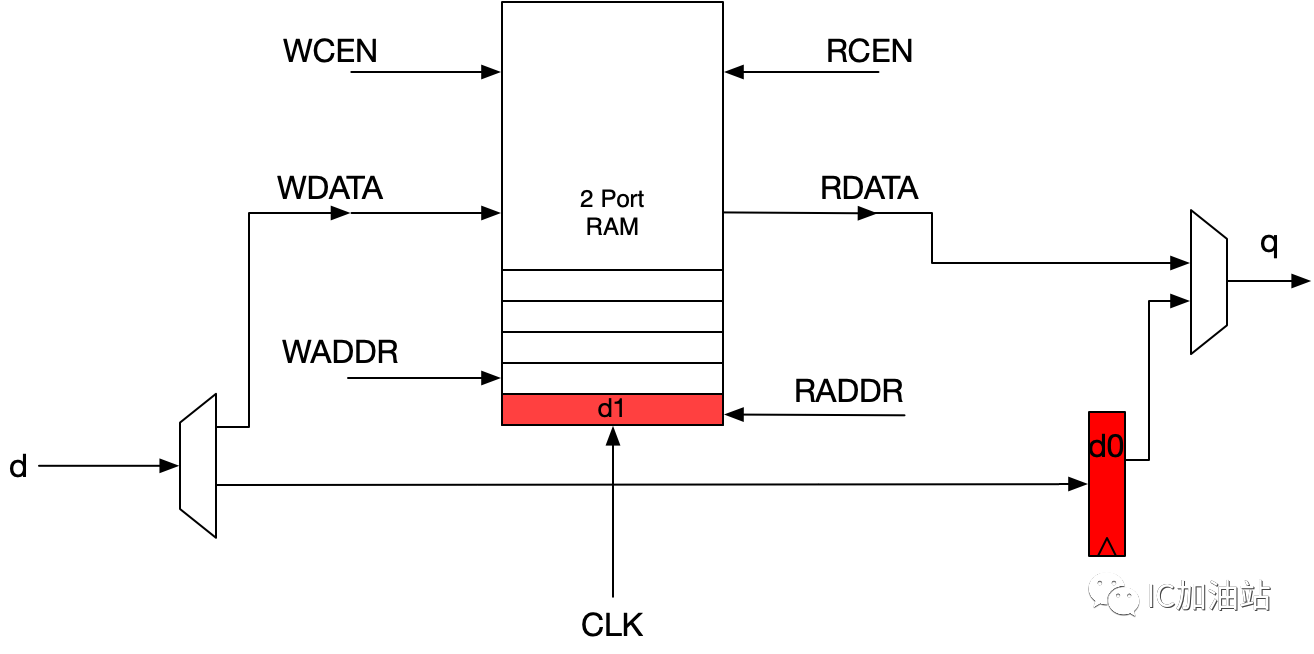

1504 开始往下读之前,老李先问一个问题,假如现在让你设计一个深度为N的基于2port SRAM的同步FIFO,请问至少需要多大的SRAM? 假设SRAM的位宽就是你的数据宽度,那么问题就是问你需要的SRAM的行数至少是多少?如果你觉得答案是显而易见的N,那么你值得读完这一篇。

2023-05-04 15:55:49 1705

1705

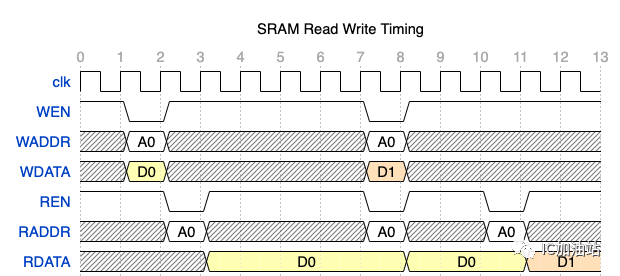

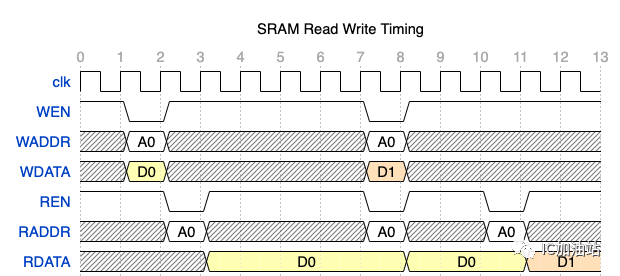

我们说这个结构之所以使得FIFO的输出Q在读完SRAM之后保持稳定,其实需要SRAM本身可以保持RDATA在读操作之后的多个周期保持稳定。即SRAM本身的读时序如下图所示:图中cycle 4,5,6都没有读操作,SRAM的RDATA依然保持D0不变。

2023-05-04 15:59:46 1132

1132

FIFO是异步数据传输时常用的存储器,多bit数据异步传输时,无论是从快时钟域到慢时钟域,还是从慢时钟域到快时钟域,都可以使用FIFO处理。

2023-05-26 16:12:49 2243

2243

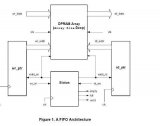

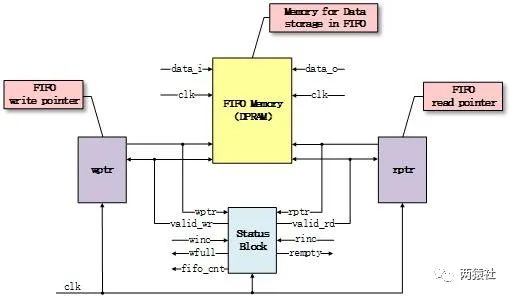

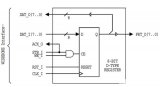

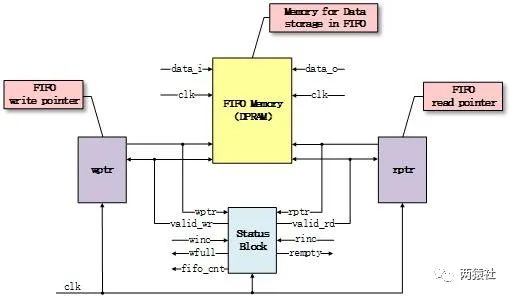

异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

2023-05-26 16:17:20 2201

2201

FIFO,First In First Out,先入先出队列,顾名思义,即第一个到达的数据也将会是第一个离开。

2023-06-05 14:39:33 1600

1600

FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。 在这篇文章中,展示了一个简单的 RTL 同步

2023-06-14 09:02:19 1414

1414 本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对PLL操作有基本的了解。

2023-07-10 10:22:24 1952

1952

同步FIFO的设计主要包括读写地址的产生、数据的读写、以及状态的控制。下面我们将分别介绍这三个方面的设计。

2023-08-31 12:53:04 1513

1513 上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数

2023-09-07 18:31:35 3352

3352

FIFO在设计是一个非常常见并且非常重要的模块,很多公司有成熟的IP,所以一部分人并没有人真正研究写过FIFO,本文仅简述FIFO中部分值得保留的设计思路。

2023-09-11 17:05:51 1557

1557

模块虽小但是要有新意,首先写一个同步FIFO,这是一个烂大街的入门级项目,但是我肯定不会写的那么简单

2023-09-11 17:11:07 1212

1212

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 1421

1421 简单的一种,其特点是输入和输出都与时钟信号同步,当时钟到来时,数据总是处于稳定状态,因此容易实现数据的传输和存储。 而异步FIFO则是在波形的上升沿和下降沿上进行处理,在输入输出端口处分别增加输入和输出指针,用于管理数据的读写。异步FIFO的输入和输出可同时进行,中间可以

2023-10-18 15:23:58 2603

2603 1. FIFO简介 FIFO是一种先进先出数据缓存器,它与普通存储器的区别是没有外部读写地址线,使用起来非常简单,缺点是只能顺序读写,而不能随机读写。 2. 使用场景 数据缓冲:也就是数据写入过快

2024-06-04 14:27:37 3489

3489

电子发烧友App

电子发烧友App

评论