同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用?

1. 同步FIFO和异步FIFO的区别

同步FIFO和异步FIFO在处理时序有明显的区别。同步FIFO相对来说是较为简单的一种,其特点是输入和输出都与时钟信号同步,当时钟到来时,数据总是处于稳定状态,因此容易实现数据的传输和存储。

而异步FIFO则是在波形的上升沿和下降沿上进行处理,在输入输出端口处分别增加输入和输出指针,用于管理数据的读写。异步FIFO的输入和输出可同时进行,中间可以插入任意个周期,比同步FIFO具有更好的灵活性。

2. 同步FIFO和异步FIFO各在什么情况下应用?

同步FIFO在设计上更为简单,使用范围也比较广泛,主要应用于数据传输和存储能力要求不高的场合。此外,由于同步FIFO只需要信号同步,因此在设计上电路也更为简洁,往往会占用比较小的面积和资源。

而异步FIFO则更适合于数据存储和传输量大,且对时序要求较高的场合。其优点在于输入和输出端口的灵活性,以及针对不同情况可以进行相应的调整。此外,由于异步FIFO需要考虑到时序问题,因此设计上也相对复杂一些。

总的来说,同步FIFO适用于数据量小、速度较慢的场合,视数据时序为基础,适用于控制逻辑的设计;而异步FIFO则适用于数据量大、速度要求高的场合,其重点在于时序控制,需要根据具体情况进行调整。

需要特别注意的是,在具体的使用过程中还需要考虑到其他因素,比如电路的功耗、占用的面积等。因此,需要根据具体情况选择适合的FIFO类型,才能实现最优的系统设计。

以上就是同步FIFO和异步FIFO的区别以及各自应用的情况的详细介绍,希望能够对读者有所帮助。

-

fifo

+关注

关注

3文章

407浏览量

45893

发布评论请先 登录

FT245BQ USB FIFO:实现高效数据传输的利器

探索TL16C752D:具有64字节FIFO的双路UART的卓越性能与应用

求助,关于串口设备驱动fifo问题

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

cy7c68013a异步slave fifo模式,外部mcu无法读写fifo怎么解决?

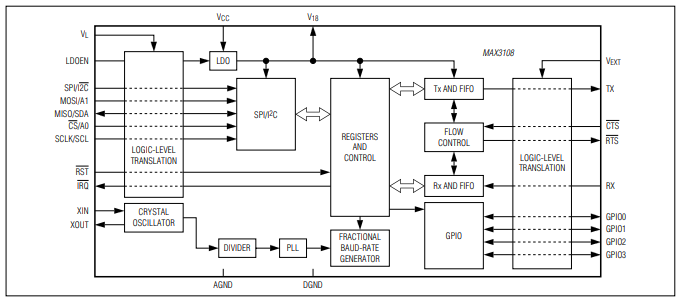

MAX3107SPI/I²C UART,具有128字FIFO技术手册

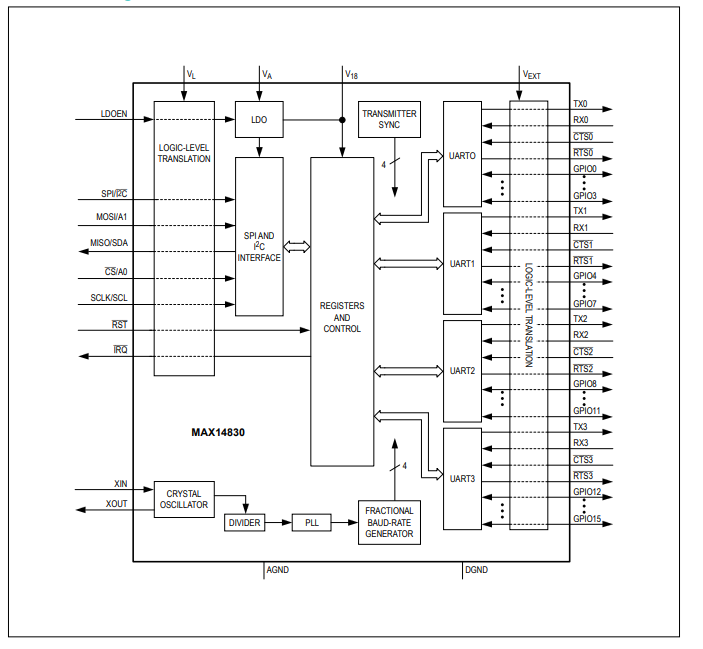

MAX14830四通道串行UART,具有128字FIFO技术手册

MAX3108 SPI/I²C UART,具有128字FIFO,WLP封装技术手册

MAX3109双通道串行UART,带有128字FIFO技术手册

如何利用5位从FIFO接口优化FX3性能并避免数据丢失?

使用CYUSB3014作为同步从设备FIFO,什么情况会导致FLAG跌至低电平而无法恢复正常呢?

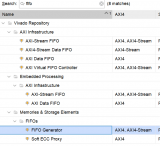

智多晶FIFO_Generator IP介绍

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用

评论