异步fifo详解

一. 什么是异步FIFO

FIFO即First in First out的英文简称,是一种先进先出的数据缓存器,与普通存储器的区别在于没有外部读写的地址线,缺点是只能顺序的读取和写入数据(对于大型数据存储,在性能上必然缓慢),其数据地址是由内部读写指针自动加一完成的,不能像普通的存储器一样,由地址线决定读取或者写入某个特定地址的数据,按读写是否为相同时钟域分为同步和异步FIFO,这里主要介绍异步FIFO,主要用于跨时钟域传输数据。

FIFO是一种数据缓冲器,用来实现数据先入先出的读/写方式。FIFO有一个写端口和一个读端口,外部无需使用者控制地址,使用方便。FIFO与普通的Block RAM有一个很明显的区别就是使用Block RAM来做数据缓存处理,使用者必须自己控制读和写地址的管理,必须保证写的数据不把Block RAM中未被读出的内容覆盖掉从而造成数据错误,同时保证读的时候要读出未被写入的地址。而采用FIFO时,只需要关注FIFO控制器给出的空满状态信号即可知道当前有没有错误的操作了FIFO,使FIFO的数据写溢出或读空。

异步FIFO读写分别采用相互异步的不同时钟,使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据

FIFO的常见参数

FIFO的宽度:即FIFO一次读写操作的数据位;

FIFO的深度:指的是FIFO可以存储多少个N位的数据(如果宽度为N)。

满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出(overflow)。

空标志:FIFO已空或将要空时由FIFO的状态电路送出的一个信号,以阻止FIFO的读操作继续从FIFO中读出数据而造成无效数据的读出(underflow)。

读时钟:读操作所遵循的时钟,在每个时钟沿来临时读数据。

写时钟:写操作所遵循的时钟,在每个时钟沿来临时写数据。

二、设计原理

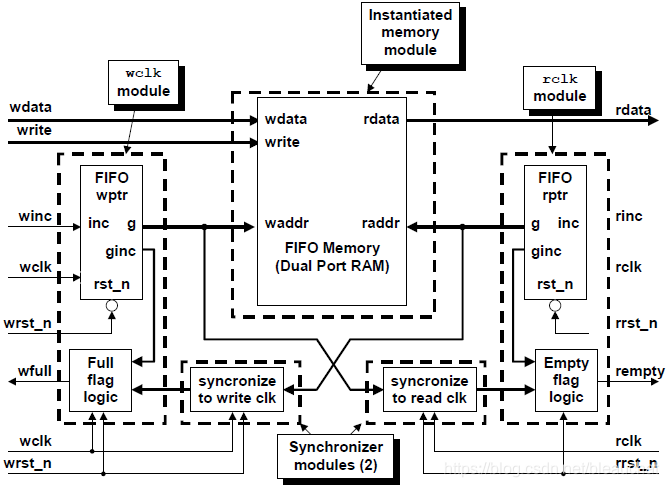

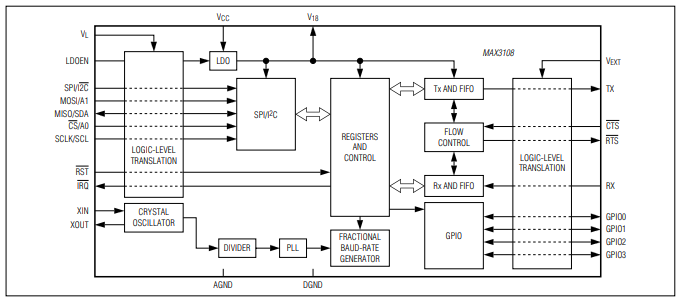

2.1结构框图

如上图所示的同步模块synchronize to write clk,其作用是把读时钟域的读指针rd_ptr采集到写时钟(wr_clk)域,然后和写指针wr_ptr进行比较从而产生或撤消写满标志位wr_full;类似地,同步模块synchronize to read clk的作用是把写时钟域的写指针wr_ptr采集到读时钟域,然后和读指针rd_ptr进行比较从而产生或撤消读空标志位rd_empty。

另外还有写指针wr_ptr和写满标志位wr_full产生模块,读指针rd_ptr和读空标志位rd_empty产生模块,以及双端口存储RAM模块。

2.2 二进制计数器存在的问题

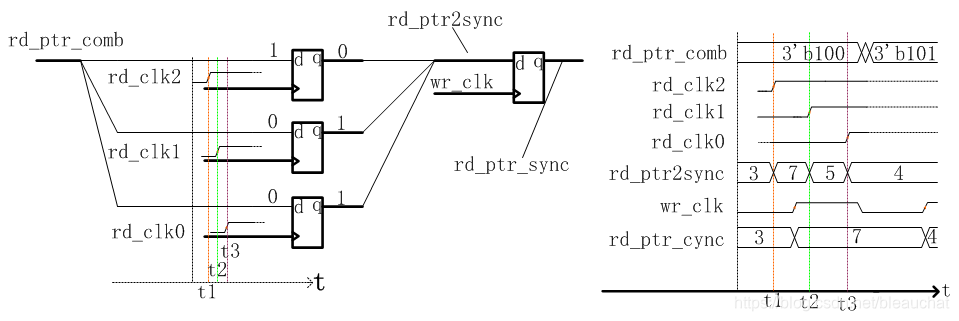

异步FIFO读写指针需要在数学上的操作和比较才能产生准确的空满标志位,但由于读写指针属于不同的时钟域及读写时钟相位关系的不确定性,同步模块采集另一时钟域的指针时,此指针有可能正处在跳变的过程中,如下图所示,那么采集到的值很有可能是不期望的值,当然,不期望的错误结果也会随之发生。

上图中,rd_ptr2sync 3和4以及4和5之间的中间态是由于到各寄存器的时钟rd_clk存在偏差而引起的。二进制的递增操作,在大多数情况下都会有两位或者两以上的bit位在同一个递增操作内发生变化,但由于实际电路中会存在时钟偏差和不同的路径延时,二进制计数器在自增时会不可避免地产生错误的中间结果,如下图。

由于rd_clk上升沿到达三寄存器的时间各不相同,这就导致了rd_ptr2sync的值从3’b011跳变3’b100的过程中经历了3’b111和3’b101,直到最后一个时钟(rd_clk0)沿的到来后rd_ptr2sync才跳变到正确结果3’b100。中间结果的持续的时间虽然相对短暂,但是这些不正确的中间结果完全有可能被其它时钟域的同步模块采集到而产生错误的动作,见上图。

由此可见,要避免中间结果的产生,其中一个可行的方案就是使被同步模块采集的数据递变时,每次只有一个bit位发生改变。格雷码计数器就是一个不错的选择。

-

fifo

+关注

关注

3文章

407浏览量

45898

发布评论请先 登录

淘宝券后价异步数据

详解SRC4192和SRC4193:专业音频领域的异步采样率转换器

探索TL16C550D/DI:高性能异步通信元件的技术剖析

详解TL16C550C:高性能异步通信芯片的卓越之选

探索TL16C752D:具有64字节FIFO的双路UART的卓越性能与应用

求助,关于串口设备驱动fifo问题

从底层解读labview的TDMS高级异步写入的工作原理

cy7c68013a slave fifo写数据出现异常的原因?怎么解决?

cy7c68013a异步slave fifo模式,外部mcu无法读写fifo怎么解决?

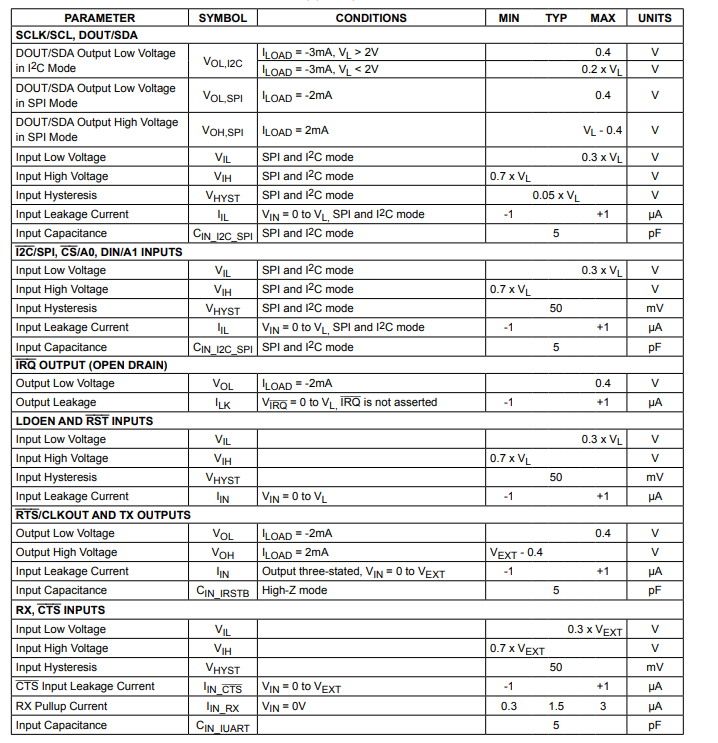

MAX3107SPI/I²C UART,具有128字FIFO技术手册

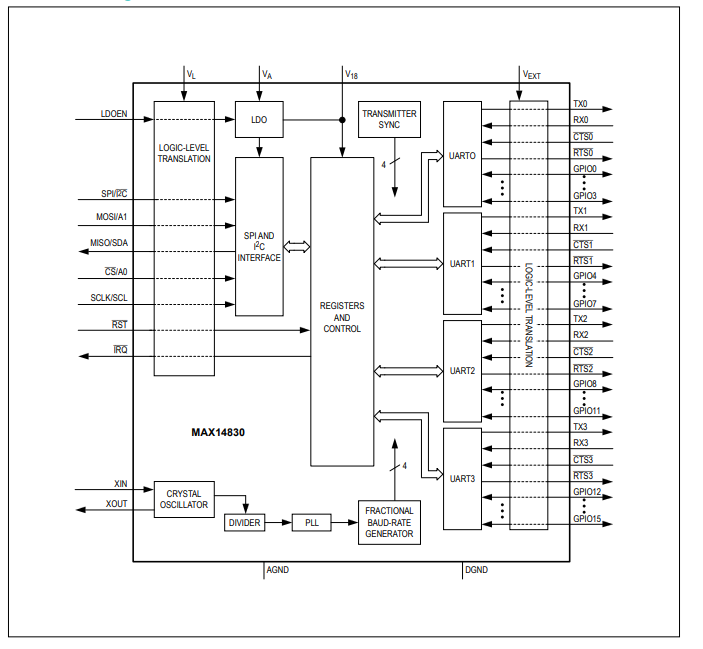

MAX14830四通道串行UART,具有128字FIFO技术手册

MAX3108 SPI/I²C UART,具有128字FIFO,WLP封装技术手册

MAX3109双通道串行UART,带有128字FIFO技术手册

智多晶FIFO_Generator IP介绍

异步fifo详解

异步fifo详解

评论