当我们安装好Vivado 的时候,也同时装好了Vivado HLS.。 这是个什么东西?我就有一种想一探究的感觉。网上一查,Vivado High-Level Synthesis。学习了一段时间

2020-10-14 15:17:19 2881

2881

HLS任务级编程第一篇文章可看这里: HLS之任务级并行编程 HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。对于控制驱动

2023-07-27 09:22:10 732

732

HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。

2023-07-27 09:21:40 579

579

1、FIR 滤波器是在数字信号处理(DSP)中经常使用的两种基本的滤波器之一,另一个为IIR滤波器。 2、FIR代表有限冲激响应(Finite Impulse Response)的简称。 3

2011-09-24 16:05:53

本帖最后由 xie0517 于 2016-8-8 08:52 编辑

FIR是有限冲击响应;IIR是无限冲击响应。 FIR和IIR滤波器的一个主要区别:FIR是线性相位,IIR为非线性

2016-08-08 08:49:32

FIR和IIR滤波器的一个主要区别:FIR是线性相位,IIR为非线性相位(双线性变换法),对于非线性相位会造成的影响,可以这样考虑:对于输入的不同频率分量,造成的相位差与频率不成正比,则输出

2018-03-12 13:21:07

滤波;IIR需要等待上一个信号的滤波输出,存在一定的时间延迟,所以处理速度上没有FIR快。图6 FIR和IIR滤波对比图从上面的简单比较可以看到IIR与FIR滤波器各有所长,所以在实际应用时应该从多方面

2019-06-27 04:20:31

我在长度为2500的信号上执行46阶FIR低通滤波器;在16 MIPS下使用PIC24FJ256GB206。所有的值都是浮动的。使用该链路实现算法。目前,正在执行2.76秒来执行对我的应用程序不可

2019-10-17 06:28:21

数字滤波器的类型有FIR(有限长冲击与IIR(无限长。离散数字系统中,滤波器的表述为差分方程。FIRFIR基本特性:FIR 滤波器永远是稳定的(系统只有零点);FIR 滤波器的冲激响应是有限长序列

2021-08-17 06:19:17

第一个问题的基础上,我是设置unsigned还是signed?3、滤波器的设计,我要给他什么样子的输入,仿真看得出什么样子的结果?部分代码如下

2017-05-09 14:18:17

。首先数据经过18个点FIR滤波器,这个滤波器系数是根据不同空间环境总结出来,这里提供一份18抽样点做参考,它是模拟波士顿交响乐演播厅得到的。然后会经过6个低通的梳妆滤波器,最后在经过1个全通滤波器。二、回音echo效果。echo效果结构较为简单,只是需要较多的内存存放数据,结构如下。decay为衰

2021-08-17 09:24:44

请教一下,我在HLS里面要将以下程序生成IP核,C Synthesis已经做好了,但是在export RTL的时候一直在运行

int sum_single(int A int B

2023-09-28 06:03:53

对于fir滤波器,已经在前面的文章中记录了仿制DIY&关于MATLAB中滤波器设计工具的使用心得记录),其设计和实现都非常简单。如果在嵌入式系统中可以满足且有必要实时iir运算,那么

2021-12-22 08:29:40

最近在做一个FPGA的课程设计,遇到一个比较烦人的问题,希望大神们可以指点迷律。一个16阶的FIR滤波器,采用分布式算法实现的,采样率1M,fc=100K,频率到了30K以上时就会出现那些尖刺,很

2018-02-25 19:25:50

就说明,要增加DSP的计算量。DSP需要更多的计算时间,对DSP的实时性有影响。 以下都是低通滤波器的设计。 FIR的设计: FIR滤波器的设计比较简单,就是要设计一个数字滤波器去逼近一个理想

2019-09-29 14:06:31

。流水线设计的具体内容在我看到的这篇博客【FPGA中流水线的原因和方法】中讲的很明白,这里不再赘述。

在HLS中,pipeline指令单指函数内部的流水,举一个简单的例子:

void func(int m

2023-12-31 21:20:08

1、HLS最全知识库介绍高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD Xilinx而言

2022-09-07 15:21:54

的输入信号值。对于IIR滤波器,冲激响应理论上应会无限持续,其输出不仅取决于当前和过去的输入信号值,也取决于过去的信号输出值。2.FIR:有限脉冲响应滤波器。有限说明其脉冲响应是有限的。与IIR相比

2019-06-26 06:15:35

像素访问对应方法2.3 用HLS实现OpenCV应用的实例(快速角点滤波器image_filter)我们通过快速角点的例子,说明通常用VivadoHLS实现OpenCV的流程。首先,开发

2021-07-08 08:30:00

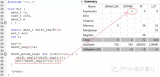

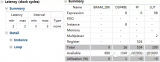

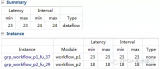

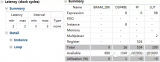

多个HLS解决方案2.实验内容实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench文件来与所得结果进行对比验证。...

2021-11-11 07:09:49

问题 1:如何利用labview来设计一个升余弦FIR滤波器问题2:labview中digital filter toolkit是个怎么回事?我看了一些英文的书里,经常介绍这个,但是我安装的版本里没有。

2014-01-16 17:01:20

不同的编译器,Xilinx Vivado High-Level Synthesis(高层综合,HLS)工具同样是一种编译器,只不过它是用来将C或者C++程序部署到FPGA上,而不是部署到传统的处理器上。在

2020-10-10 16:44:42

的文件夹重命名为“xfopencv”,如下图所示:图 13.3.2 解压之后的xfopencv库我们在电脑中的“F:\ZYNQ\High_Level_Synthesis”目录下新建一个名为

2020-10-16 16:22:38

结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。所谓串行结构,即串行实现滤波器的累加运算,将每级延时单元与相应系数的乘积结果进行累加后输出,因此整个滤波器实际上只需要一个乘法器运算单元。串行

2017-04-14 15:20:31

FIR滤波器如何定义?为什么要使用FIR滤波器?

2021-04-06 07:48:45

1、使用Vitis HLS创建属于自己的IP高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD

2022-09-09 16:45:27

脉冲响应(ⅡR)滤波器和有限长单位脉冲响应(FIR)滤波器两种,其中,FIR滤波器能提供理想的线性相位响应,在整个频带上获得常数群时延从而得到零失真输出信号,同时它可以采用十分简单的算法实现,这两个

2019-08-30 07:18:39

DSPBuilder设计了一个4阶FIR滤波器,并用QuartusII进行硬件仿真,仿真结果表明设计FIR滤波器的正确性。同时使用IPCore开发基于FPGA的FIR数字滤波器,利用现有的IPCore在FPGA器件上实现滤波器设计。

2012-08-11 15:32:34

Vivado 2017.4、Xilinx VivadoHLS 2017.4、Xilinx SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

本文提出一种基于Stratix系列FPGA器件的新的实时高速脉动FIR滤波器的快速实现方法。

2021-05-06 09:50:42

本文首先介绍了FIR滤波器和脉动阵列的原理,然后设计了脉动阵列结构的FIR滤波器,画出电路的结构框图,并进行了时序分析,最后在FPGA上进行验证。结果表明,脉动阵列的模块化和高度流水线的结构使FIR

2021-04-20 07:23:59

相位,简单可扩展到多速率情况,以及充足的硬件支持除了其他原因之外。此示例展示了DSP System Toolbox™中用于设计具有各种特性的低通FIR滤波器的功能。内容获得低通FIR滤波器系数最小阶低通滤波器

2018-08-23 10:00:16

Vivado HLS 2017.4 、Xilinx SDK 2017.4。

测试板卡是基于创龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC

2023-08-24 14:44:10

Vivado HLS 2017.4 、Xilinx SDK 2017.4。测试板卡是基于创龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业

2023-01-01 23:51:35

) ug871-vivado-high-level-synthesis-tutorial.pdf(2) ug902-vivado-high-level-synthesis.pdf

1 HLS 开发流程说明本章节以产品资料“4-

2023-08-24 14:40:42

) ug871-vivado-high-level-synthesis-tutorial.pdf(2) ug902-vivado-high-level-synthesis.pdf1 HLS 开发流程说明本章节以产品资料“4-软件资料\Demo

2023-01-01 23:52:54

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。

Xilinx Vivado HLS (High-Level Synthesis

2023-08-24 14:52:17

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS (High-Level Synthesis,高层次

2023-01-01 23:50:04

(High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加速算法开发的进程,缩短

2023-01-01 23:46:20

(High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加速算法开发的进程,缩短

2023-08-24 14:54:01

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 09:38:32

频率分量,为了节省资源,使用IIR滤波器即可。FIR滤波器FIR的最大特点就是其系统响应 h(n)是一个N点的有限长序列,FIR的输出y(n)本质上就是输入信号x(n)和h(n)的卷积(根据傅里叶变换

2020-09-25 17:44:38

新思科技公司(Synopsys)目前推出该公司最新研发的Synphony HLS (High Level Synthesis)解决方案。该解决方案集成了M语言和基于模型的综合法,与 传统RTL流程

2019-08-13 08:21:49

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-23 06:39:46

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-27 07:16:54

最近在学习全相位滤波器,请问有人做过全相位FIR滤波器吗?能不能用matlab程序来比较一下全相位FIR滤波器与传统方法设计的FIR滤波器有什么区别??希望有人能帮我解答。。。感激不尽。。。。

2011-05-10 15:34:03

用窗函数设计FIR滤波器实验一、实验目的1、熟悉FIR滤波器设计的基本方法。2、掌握用窗函数设计FIR数字滤波器的原理及方法,熟悉相应的计算机高级语言编程。3、熟悉线性相位FIR滤波器的幅频特性

2009-05-12 01:47:22

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 15:54:48

转dsp系列教程 FIR滤波器设计到的内容比较多,本章节主要经行了总结性的介绍,以帮助没有数字信号处理基础的读者能够有个整体的认识,有了这个整体的认识之后再去查阅相关资料可以到达事半功倍的效果

2016-09-29 08:23:26

转dsp系列教程 本章节讲解FIR滤波器的低通,高通,带通和带阻滤波器的实现。 37.1 FIR滤波器介绍 37.2 Matlab工具箱生成C头文件 37.3 FIR低通滤波器设计 37.4 FIR

2016-09-29 08:32:34

最近总是遇到很多大侠在问滤波器相关的问题,之前对这一方面接触不是很多,最近也是在学习一些这方面的知识,今天先和大侠简单聊一聊FIR滤波器和IIR滤波器的区别,后续等研究的差不多了,再更新有关滤波器

2023-05-29 16:47:16

AD9361的FIR滤波器是否可以配置成RRC滤波器?只能用作低通滤波器吗?另外,FIR滤波器的2/4倍插值是对原信号进行补0吗?

2019-01-07 11:31:53

你好,我有一个与switch语句的合成有关的问题。我开始使用Vivado HLS并且我已经创建了一个小的file.cpp,仅用于学习,但是当Vivado HLS合成文件时,我没有得到任何开关语句

2019-11-05 08:21:53

FIR滤波器是什么?DSPBuilder是什么?FIR数字滤波器的DSPBuilder设计

2021-04-30 07:14:19

描述 HLS系列霍尔效应液位传感器(HLS)是用于连续液位监测的定制设计解决方案,适用温度范围宽广,可校准定制编程输出以适应各种几何形状的液位储存箱。HLS系列是一款智能传感器,带有板载

2021-07-14 14:08:24

用窗函数设计FIR滤波器一、实验目的1、熟悉FIR滤波器设计的基本方法。2、掌握用窗函数设计FIR数字滤波器的原理及方法,熟悉相应的计算机高级语言编程。3、熟悉线性

2009-05-10 10:02:15 97

97 什么是fir数字滤波器

Part 1: Basics1.1 什么是FIR滤波器?FIR 滤波器是在数字信号处理(DSP)中经常使用的两种

2008-01-16 09:42:22 16243

16243 Synopsys天宣布推出其Synphony HLS (High Level Synthesis)解决方案

新思科技公司,今天宣布推出其Synphony HLS (High Level Synthesis)解决方案。该解决方案集成了M语言和基于模型的综合

2009-11-04 16:55:53 962

962 fir滤波器的有关资料 fir_滤波器sourc.rar

2015-12-14 14:12:56 24

24 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 基于MATLAB的FIR滤波器设计与滤波。

2016-12-14 22:08:25 63

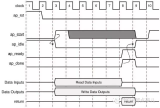

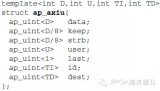

63 在前几章里,已经分别介绍了BlockLevel Interface,Port Level Interface中的NoI/O Protocol和AXI4。本章里着重介绍下Port Level

2017-02-08 02:42:41 801

801

继续HLS的基本概念。 1、DataFlow的概念,以及Dataflow和Pipeline的区别 如下所示的图像处理过程,数据处理由2个滤波器构成: 默认情况下,HLS会遵循c逻辑中的先后顺序,依次

2017-02-08 03:20:41 622

622

在上一章HLS的端口综合里有提及,HLS综合后的端口分为2中类型:BlockLevel和Port Level Interface。其中Port level是我们需要重点关注的,它又可以细分为4中类型

2017-02-08 03:27:11 475

475

在之前HLS的基本概念1里有提及,HLS会把c的参数映射成rtl的端口实现。本章开始总结下HLS端口综合的一些知识。 1.HLS综合后的rtl端口大体可以分成2类: Clock Reset端口

2017-02-08 03:29:11 544

544

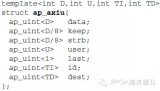

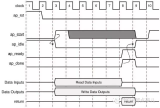

在上一章HLS提到了axi lite端口的综合方式,以及directive的一些语法规则。这一章里面,介绍一下axi-stream和full axi端口的综合实现问题。 1. AXI-Stream

2017-02-08 03:31:04 414

414

在上一章HLS提到了axi lite端口的综合方式,以及directive的一些语法规则。这一章里面,介绍一下axi-stream和full axi端口的综合实现问题。 AXI FULL端口的实现

2017-02-08 03:35:34 776

776

在之前的3章里,着重讲解了HLS对AXI端口(包括axi-lite,axi-stream和full axi端口)的综合实现问题,下面让我们来介绍一下其它的端口类型是如何实现的。 在开始之前,先来

2017-02-08 03:39:11 354

354

下面先介绍下No I/OProtocol ap_none: ap_none是HLS最简单的一种接口协议类型,不论是input还是output端口,综合后都不附带额外的控制信号,在rtl里面所呈现的唯一

2017-02-08 03:45:02 500

500

众所周知,HLS是Xilinx于几年前推出的一个高级综合工具,可以直接把C/C++代码,转换成可综合的verilog/VHDL代码。听起来很高级,是不是?。但看新鲜的人多,愿意吃螃蟹的人却很少。这里

2017-02-08 05:07:20 1183

1183

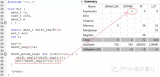

在上一章“High LevelSynthesis(HLS) 从一个最简单的fir滤波器开始2”中,我们通过修改c的头文件里面的类型精度定义,把DSP48E的消耗数量从8个压缩到了2个: 但这个结果

2017-02-08 05:11:11 341

341

在这个系列的前3篇文章“HighLevel Synthesis(HLS) 从一个最简单的fir滤波器开始1-3”中,我们从一个最简单的FIR滤波器,一步步优化,得到了一个比较理想的HLS综合结果

2017-02-08 05:13:37 983

983

在这个系列的前4篇文章“HighLevel Synthesis(HLS) 从一个最简单的fir滤波器开始1-4”中,我们从一个最简单的FIR滤波器,一步步优化,得到了一个资源和Latency都比

2017-02-08 05:18:11 456

456

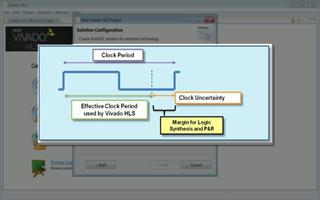

相信通过前面5篇fir滤波器的实现和优化过程,大家对HLS已经有了基本的认识。是时候提炼一些HLS的基本概念了。 HLS支持C,C++,和SystemC作为输入,输出为Verilog(2001

2017-02-08 05:23:11 674

674

1. HLS仅支持一个主时钟和复位 因此,目前还没有办法完全用HLS做出一个多时钟域的设计。 2. 对于同一个参数,HLS可以综合出各种各样的端口类型 这也需要额外的约束去进行设置 3. 虽然

2017-02-08 05:24:31 271

271

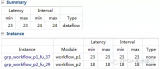

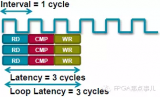

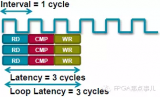

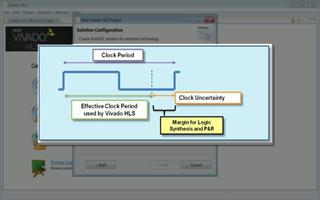

继续HLS的基本概念。 Latency 和 Interval(II)的区别 当HLS综合完后,在performance报告中,会看到这2个指标,它们都跟性能相关。那么这两个参数的区别和含义具体

2017-02-08 05:28:12 708

708

高层次综合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA设计工具,它能让用户通过编写C/C++等高级语言代码实现RTL级的硬件功能。随着这款工具

2018-07-14 06:42:00 5868

5868 数字滤波器广泛应用于硬件电路设计,一般分为FIR滤波器和IIR滤波器。那么FIR滤波器和IIR滤波器有什么区别呢?本文通过几个例子做一个简单的总结。

2017-05-03 11:36:31 19

19 在特定图像处理硬件设计中成功运用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 数年之后, Qualcomm 认识到了 HLS

2017-09-11 11:37:38 9

9 摘要:HTTP Live Streaming(缩写是HLS)是一个由苹果公司提出的基于HTTP的流媒体网络传输协议。今天主要以HLS协议为中心讲述它的一些原理。

2017-12-10 09:25:37 54718

54718 Xilinx公司讲述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47:00 3416

3416

在集成电路行业飞速发展的今天,缩短产品开发的周期而又不牺牲验证过程,这不可避免地成为了商业市场的一个关键因素。Xilinx Vivado High Level Synthesis (即Vivado

2018-06-04 01:43:00 7171

7171

HLS高阶综合(high level synthesis)在被广泛使用之前,作为商业技术其实已经存在了20多年。设计团队对于这项技术可以说呈现出两极化的态度:要么坚信它是先进技术之翘楚,要么对其持谨慎怀疑态度。

2020-11-04 13:45:03 3035

3035 【导读】:前面的文章介绍了移动平均滤波器、IIR滤波器、梳状滤波器,今天来谈谈FIR滤波器的设计实现。

2022-02-07 11:34:32 13

13 1、HLS简介 HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境

2022-12-02 12:30:02 2571

2571 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 数字滤波器是数字信号处理中最常用的一种技术,可以对数字信号进行滤波、降噪、增强等处理,其中最常见的两种数字滤波器是IIR滤波器和FIR滤波器。本文将从IIR滤波器和FIR滤波器的原理、特点和应用等方面进行详细介绍,以便更好地理解两种滤波器的区别。

2023-06-03 10:21:43 12909

12909 电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 1

1 该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的时间内对测试图像进行去噪,同时消耗不到 25% 的可用 PL 资源。特征如下:

2023-07-03 09:06:43 466

466

电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2

电子发烧友App

电子发烧友App

评论