FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。

2017-06-21 16:05:57 8433

8433

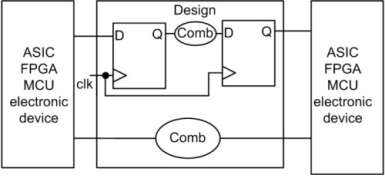

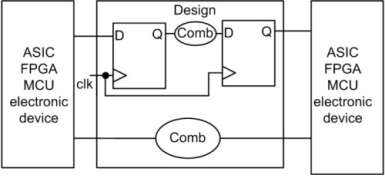

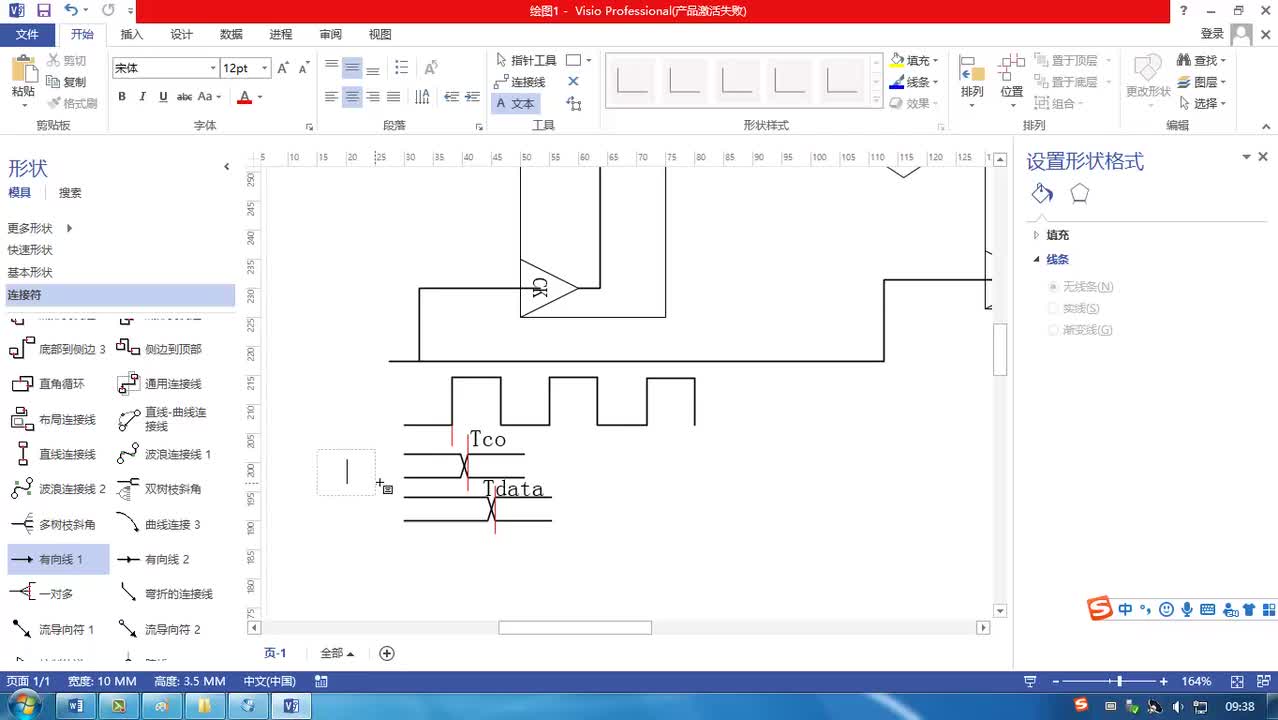

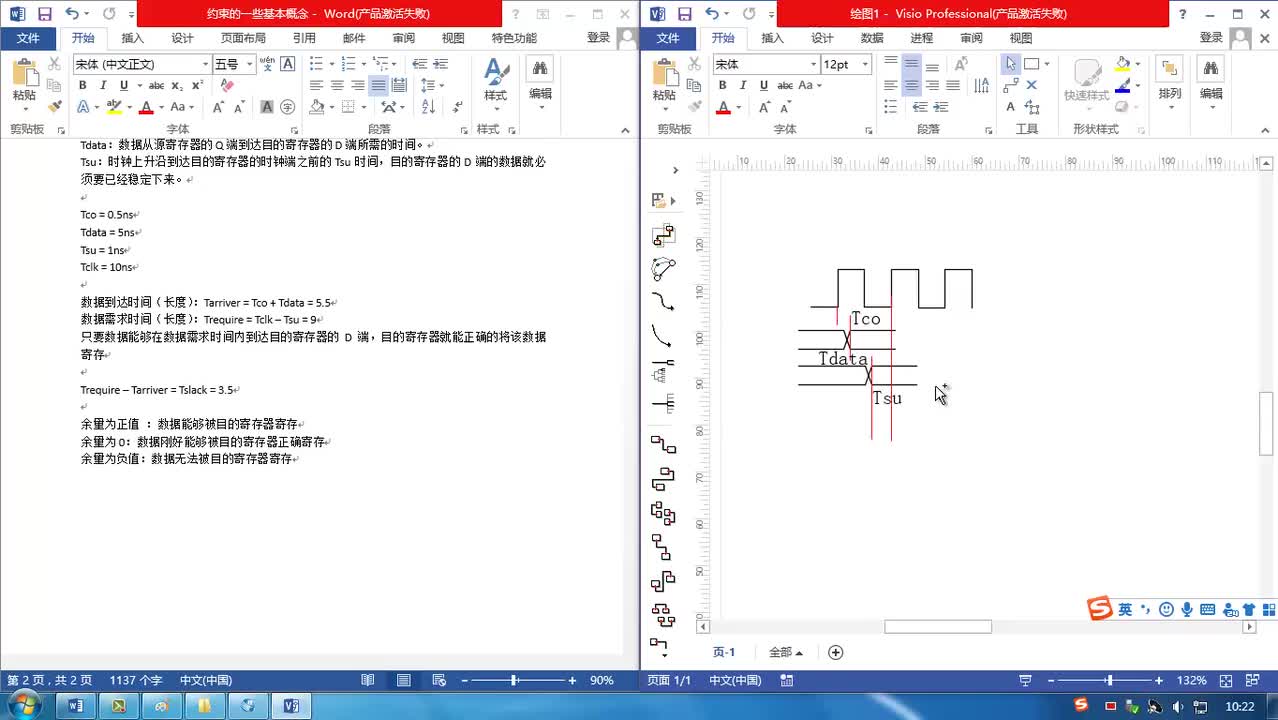

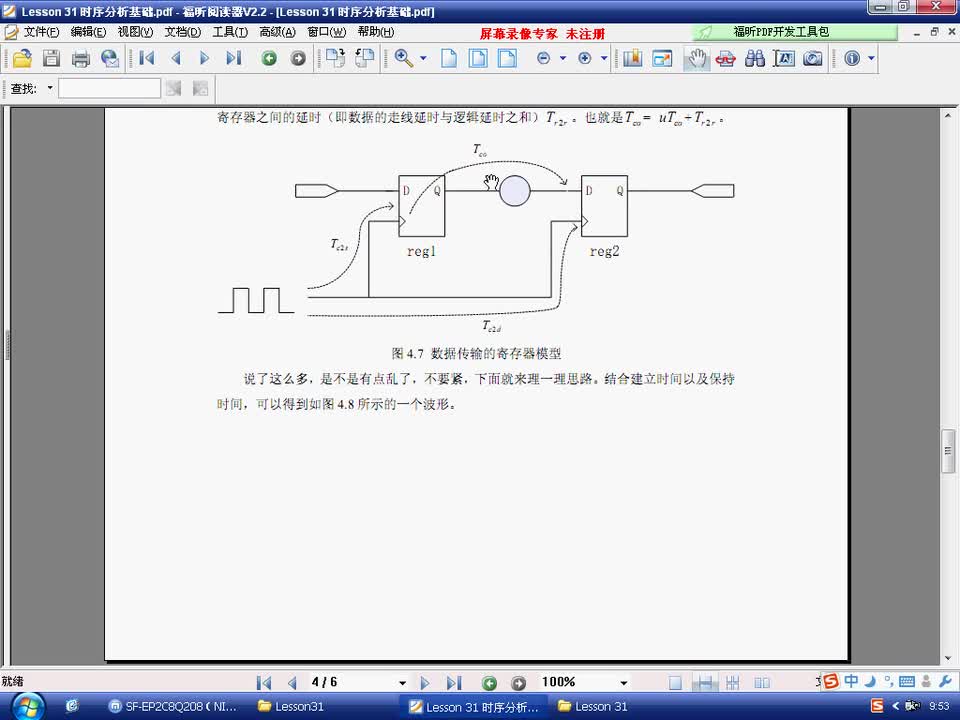

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 3687

3687

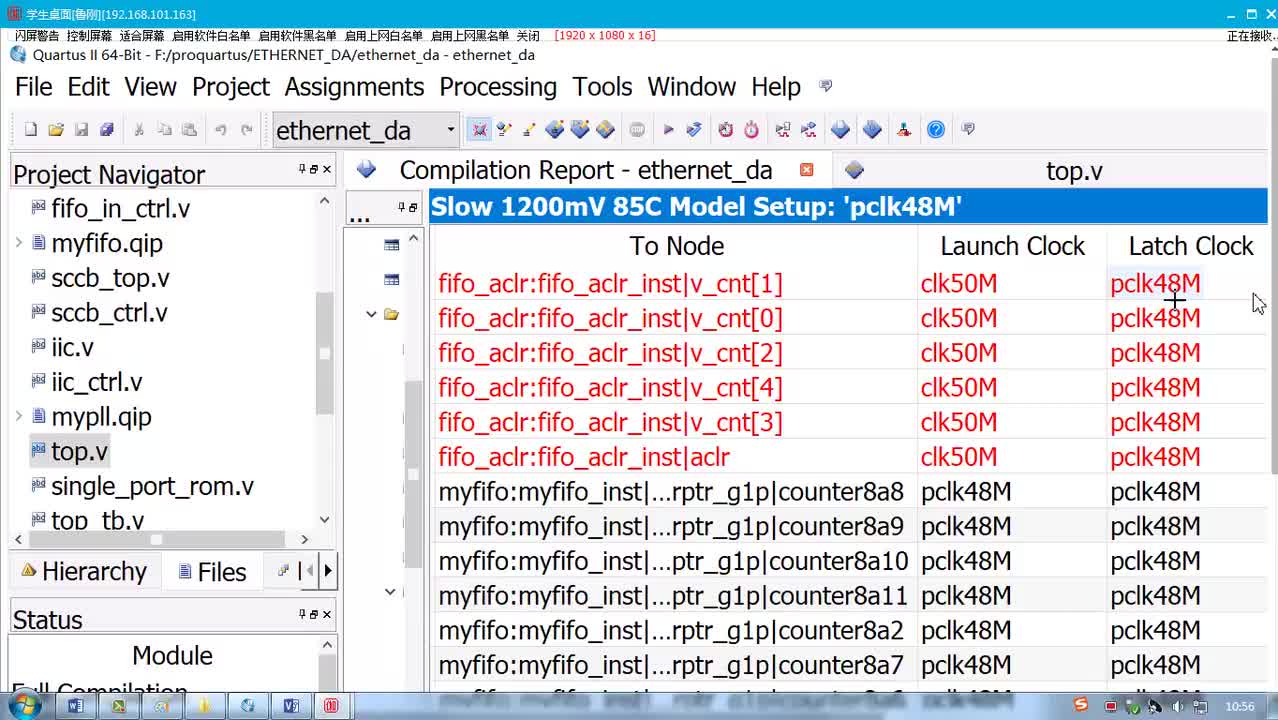

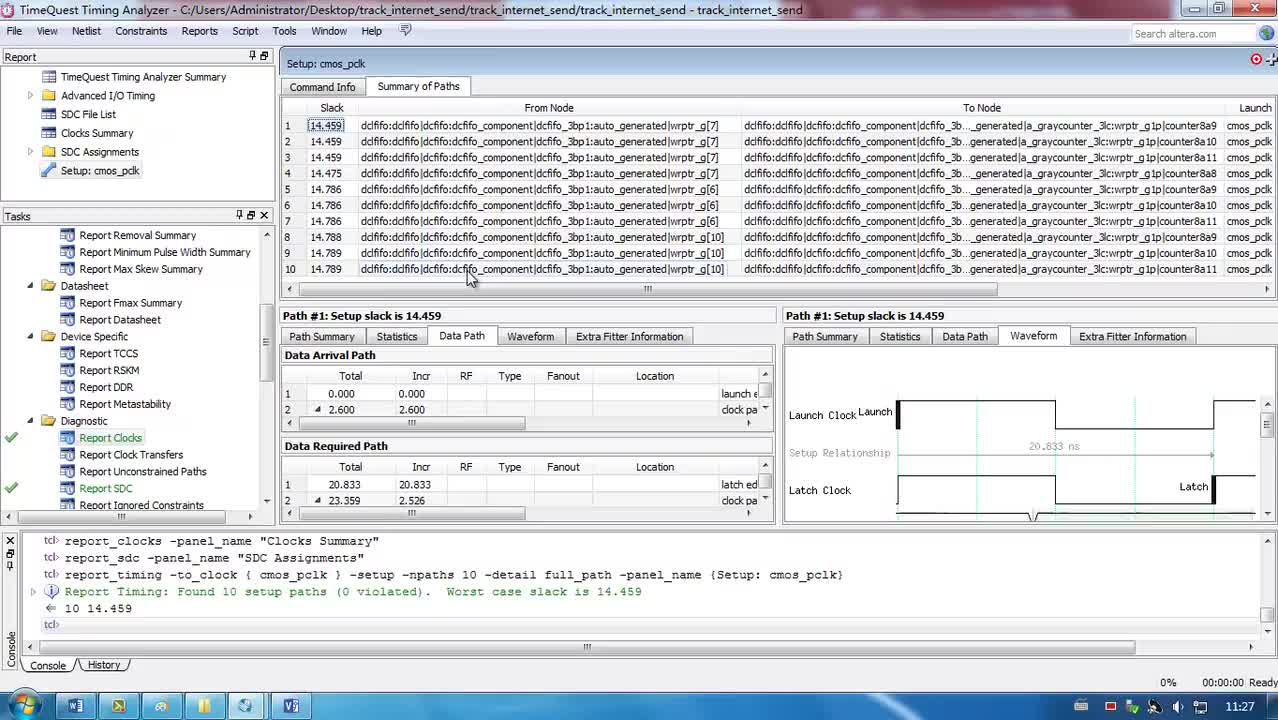

在fpga工程中加入时序约束的目的: 1、给quartusii 提出时序要求; 2、quartusii 在布局布线时会尽量优先去满足给出的时序要求; 3、STA静态时序分析工具根据你提出的约束去判断

2020-11-25 11:39:35 7608

7608

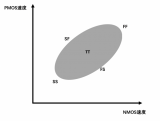

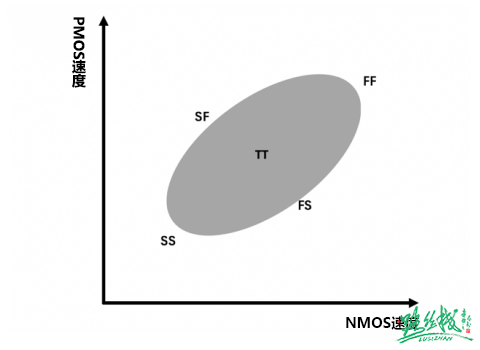

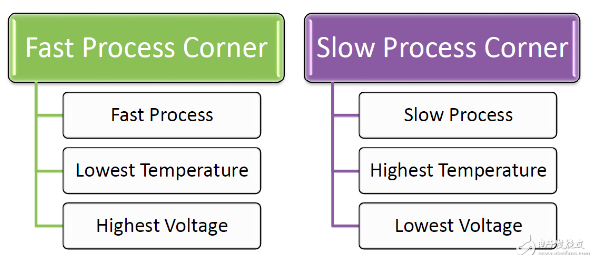

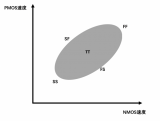

静态时序分析用工艺角(Corner)来反映不同的工艺/电压/温度等环境下电路的工作条件。工艺角下的单元库中定义了单元的时序模型(包括时序延迟值和时序约束值)。理论上时序收敛要保证芯片在各个工作场景(Scenario)下都没有时序违例,而实际操作中会选取某一个或几个特殊的工艺角去检查。

2022-08-30 10:17:49 2898

2898 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 时序分析是FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-10-21 09:28:58 4570

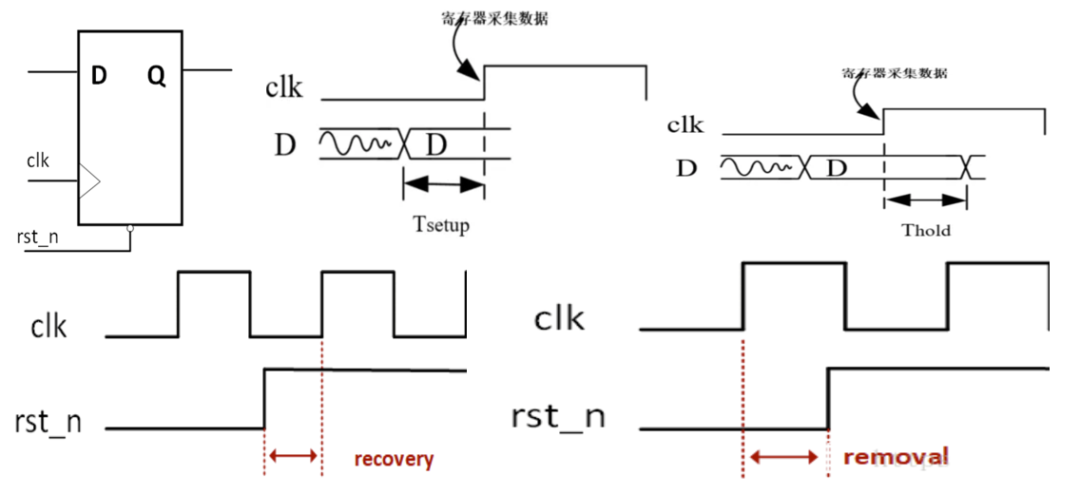

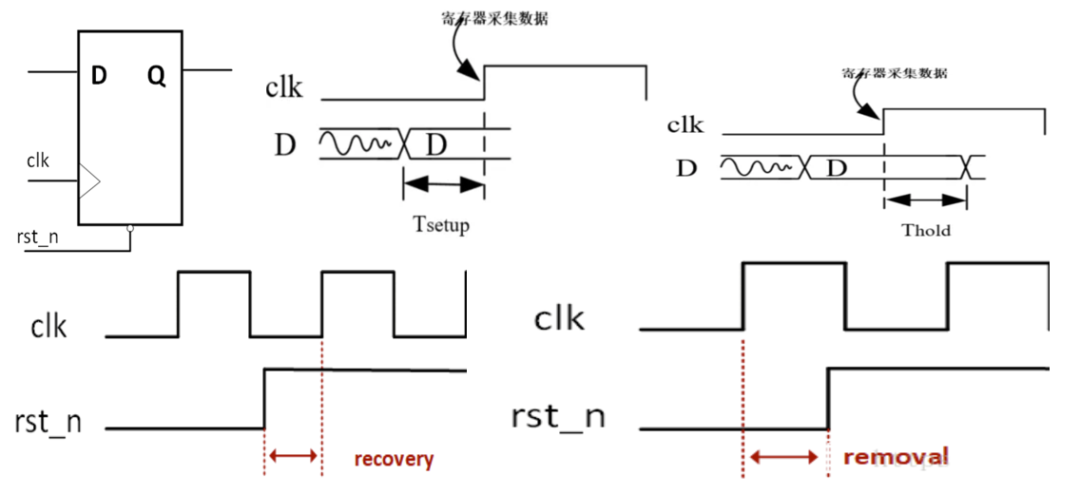

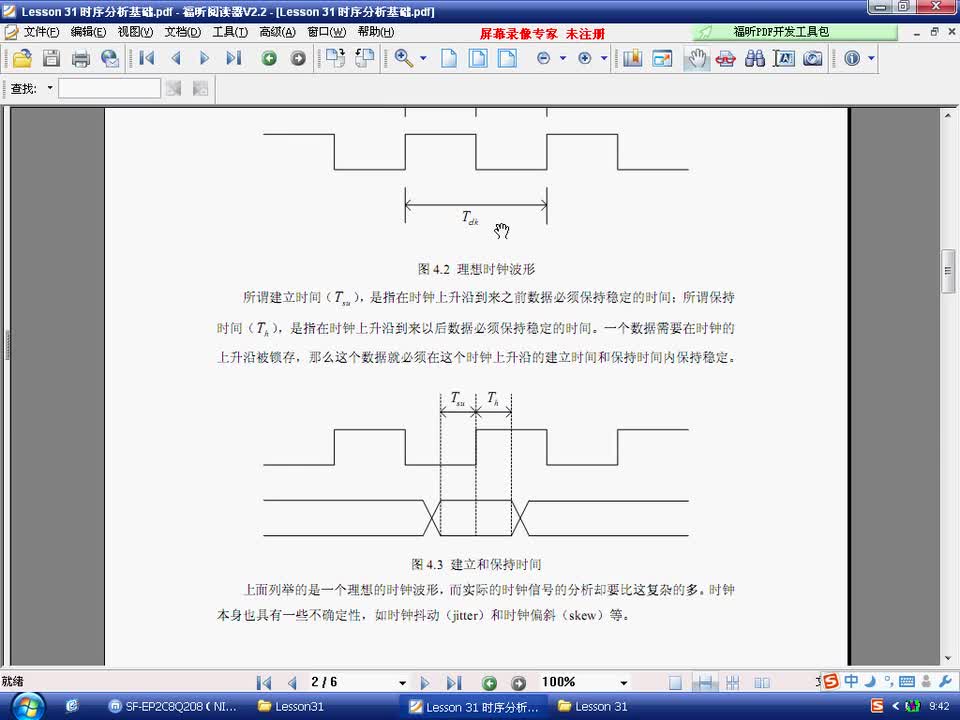

4570 时序分析本质上就是一种时序检查,目的是检查设计中所有的D触发器是否能够正常工作,也就是检查D触发器的同步端口(数据输入端口)的变化是否满足建立时间要求(Setup)和保持时间要求(Hold);检查D

2023-07-14 10:48:19 5776

5776

今天跟大家分享的内容很重要,也是调试FPGA经验的总结。随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码

2023-08-01 09:18:34 3075

3075

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 3030

3030

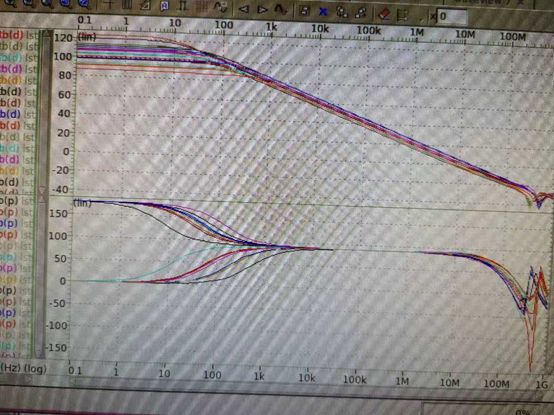

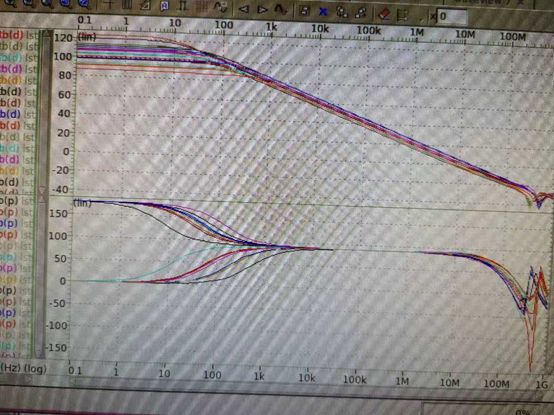

一个运放,使用电阻接成负反馈的形式,闭环放大倍数为-1。进行环路stb仿真,有些corner下相位曲线从0开始,但其他corner正常。这种是什么原因?该怎么解决?

2023-11-07 14:52:35 3907

3907

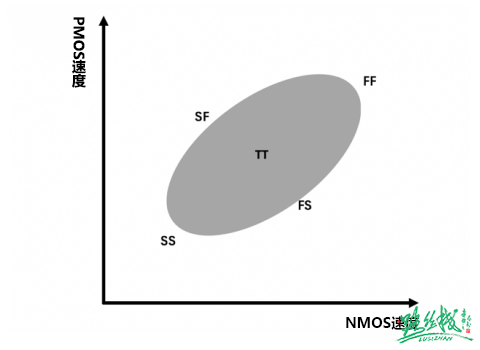

:Typical N Typical P FF:Fast N Fast P SS:Slow N Slow P FS:Fast N Slow P SF:Slow N Fast P

2023-12-01 13:31:22 5214

5214

电子发烧友网报道(文/梁浩斌)Corner case在自动驾驶中是指行驶过程中可能出现,但发生频率极低的小概率事件。尽管平时很少会遇到,但对于自动驾驶系统来说,遇到无法做出决策的corner

2022-10-19 01:21:00 5073

5073 今天给大侠带来FPGA 高级设计:时序分析和收敛,话不多说,上货。

这里超链接一篇之前的STA的文章,仅供各位大侠参考。

FPGA STA(静态时序分析)

什么是静态时序分析?静态时序分析就是

2024-06-17 17:07:28

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

FPGA时序相关的资料。都看完看懂时序就没问题了。分了三个附件:第一个是通过一些例子教你如何搞定时序分析。第二个附件是网上各种大神们对时序的理解,主要是他们的博客链接以及网站链接。第三个是其他的一些零散的关于时序的资料。

2012-11-12 17:45:28

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

基本的时序分析理论2本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 下面我们再来看一个例子,如图8.2所示

2015-07-14 11:06:10

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

FPGA静态时序分析——IO口时序(Input Delay /output Delay)1.1概述 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能

2012-04-25 15:42:03

如题:fpga时序分析一般都做哪些分析我自己研究时序分析也有一段时间了 ,从理论到altera的timequest,差不多都了解了 ,但就是不知道一个具体的项目都要做哪些约束。求大神知道,或者有没有这方面的资料(网上资料基本都看过了,没有说明具体项目的)。

2012-10-22 22:20:32

在学习fpga的过程中的疑问:1、在功能仿真和板级验真后没问题,还需要进行时序分析吗2、怎么知道自己写的代码有时序问题?

2017-01-08 17:50:35

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

大家好

我想请教一下大家关于TLV5616和TLV5636的工作模式,具体就是两种工作模式FAST和SLOW分别有什么特点,优势,选择时应该注意什么?谢谢!

2025-02-07 07:02:58

什么是时序分析?时序约束的作用是什么?FPGA组成的三要素分别是哪些?

2021-09-18 06:05:51

各位好,初次使用pt对fpga进行静态时序分析,想请教下需要哪些文件。是不是需要:1、在ise或qutartus生成的网表2、SDC文件3、.db文件.db文件必须且只能从dc生成吗,要是从.lib转化而来,这个lib文件在fpga设计时又从哪里得到问题貌似比较多,谢谢回答

2014-12-18 16:15:12

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一个时钟周期对于FPGA内部的寄存器都有特殊的意义,不同的时钟周期执行不同的操作

2017-02-26 09:42:48

器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。基本的电子系统如图 1所示,一般自己的设计都需要时序分析,如图 1所示的Design,上部分为时序组合逻辑,下部分只有组合

2018-04-03 11:19:08

:JCDI.0.2010-04-005【正文快照】:1引言90/65nm下芯片的后端设计变得更加复杂,随着模式(mode)和角落(corner)的增多,如何快速取得各种情况下的时序收敛成为设计的重要

2010-05-28 13:41:58

to dynamically switch between the SLOW and the FAST advertising based on the energy available on the temporary

2018-12-13 14:55:06

在用 ADE XL仿真出现一个error ERRO ID:5010在用 ADE XLall 跑all Corner 的时候,第一个Corner总是会报错。不知道怎么回事,outputlog里面又没有显示有错,

2021-06-25 06:04:09

1. FPGA时序的基本概念FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是

2019-07-09 09:14:48

请问如何使用ocean进行corner仿真并用波形查看器查看结果?

2021-06-24 07:50:23

时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 , FPGAs,and structured ASICs that fi t into nearly every corner ofthe digital electronics market. Combined with Altera’sin

2010-06-30 18:00:09 0

0 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1476

1476 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2017-02-11 19:08:29 4953

4953

fpga时序收敛

2017-03-01 13:13:34 23

23 如今的集成电路(Integrated Circuit,IC)设计往往要求芯片包含多个工作模式,并且在不同工艺角(corner)下能正常工作。工艺角和工作模式的增加,无疑使时序收敛面临极大挑战。本文

2017-10-20 15:21:11 3

3 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 3842

3842 提出了由于FPGA容量的攀升和配置时间的加长,采用常规设计会导致系统功能失效的观点。通过详细描述Xilinx FPGA各种配置方式及其在电路设计中的优缺点,深入分析了FPGA上电时的配置步骤和工作

2017-11-22 07:18:34 8500

8500

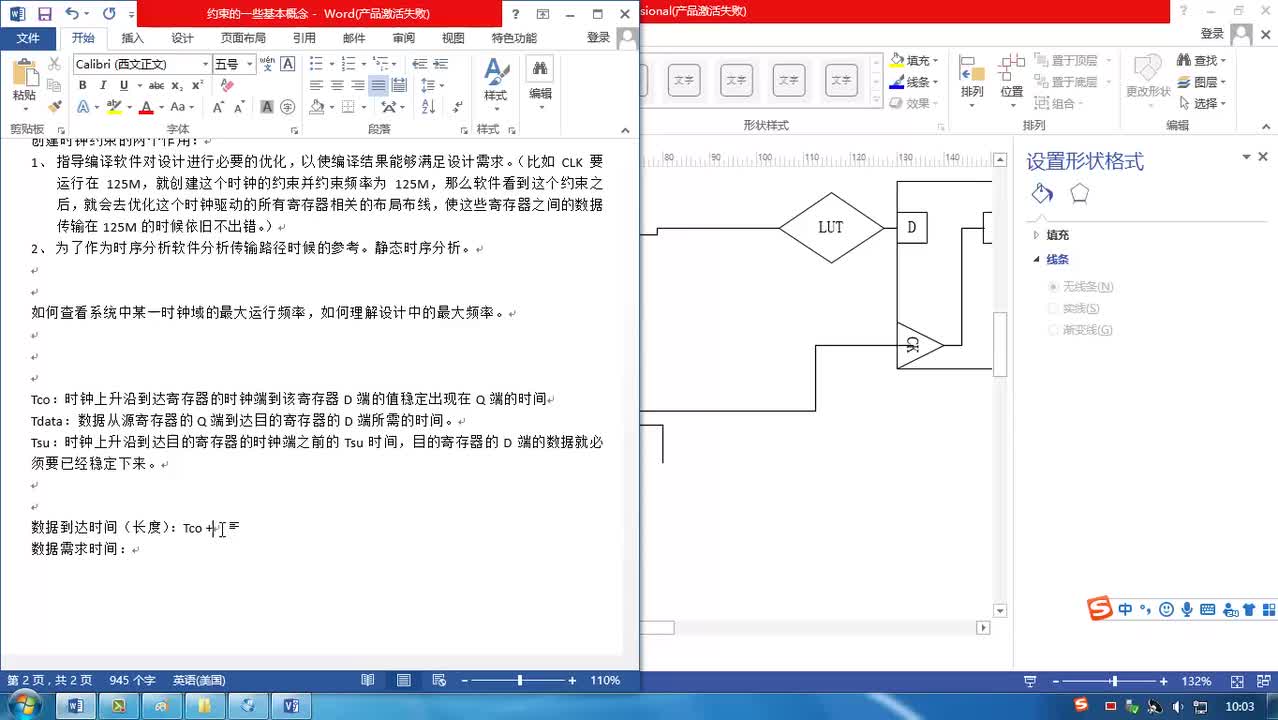

FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4865

4865

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38:00 7943

7943

“10月是我们在Dark Corner最喜欢的季节,我们很高兴能通过这些激动人心的电影来扩展我们的生活,同时继续与世界各地的其他虚拟现实媒体和LBE场馆建立新的合作关系,”Dark Corner的CEO盖伊谢尔默丁在一份官方声明中说。

2018-10-30 09:15:46 846

846 FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:01:00 2671

2671

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 67

67 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 22

22 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种很简单的解读办法,可以看透它的本质,而且不需要再记复杂的公式了。

2021-01-12 17:48:08 19

19 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 17

17 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 19

19 电子发烧友网为你提供时序分析是FPGA如何设计?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-15 08:51:20 14

14 上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 3757

3757

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为

2022-09-27 14:45:13 4033

4033 电子发烧友网报道(文/梁浩斌)Corner case在自动驾驶中是指行驶过程中可能出现,但发生频率极低的小概率事件。尽管平时很少会遇到,但对于自动驾驶系统来说,遇到无法做出决策的corner

2022-10-19 07:20:02 1900

1900 芯片工作过程中,由于负载发生变化,导致芯片电源网络的供电电压和电流发生变化,可能会出现芯片供电电压低于timingsignoff corner的最小电压的情况,影响芯片的时序。

2022-11-09 21:02:32 1156

1156 首先使用Harris Corner特征检测器和sift描述符检测图像中的特征,并在其他图像中找到最佳匹配特征; 然后使用RANSAC 对齐照片(确定它们的重叠和相对位置),最后将生成的图像拼接到一个无缝的全景图中。

2023-03-01 11:41:03 1936

1936

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,终于找到了一种很简单的解读办法,可以看透它

2023-03-14 19:10:03 1476

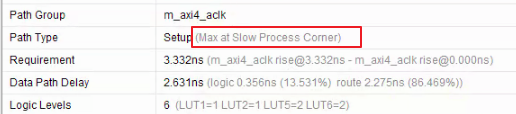

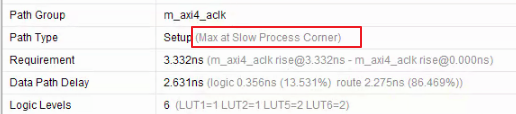

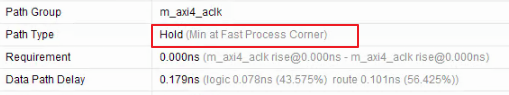

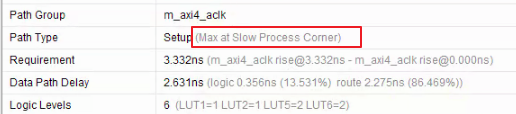

1476 在做STA Signoff时,对于Setup来说选择Slow Corner,也就是慢工艺(SS)、低压(Low Voltage)、高温(High Temperature);

2023-04-07 09:37:05 7197

7197 FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 2404

2404 在FPGA的时序分析页面,我们经常会看到`Max at Slow Process Corner`和`Min at Fast Process Corner`,具体是什么含义呢?

2023-05-05 15:50:10 3021

3021

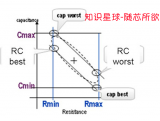

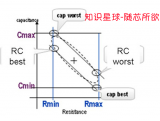

90nm后更新的工艺,考虑到互连线coupling的影响,出现了RCworst, RCbest corner.

2023-06-11 15:32:53 9867

9867

UltraEM可以使用Corner Sweep来仿真工艺变化对器件结构造成的影响,具体包含三种仿真模式:MonteCarlo仿真、Perturbation仿真与Corner仿真。

2023-06-19 10:25:53 2021

2021

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 1276

1276

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

今天我们要介绍的时序分析基本概念是MMMC分析(MCMM)。全称是multi-mode, multi-corner, 多模式多端角分析模式。这是在先进工艺下必须要使用的一种时序分析模式。

2023-07-04 15:40:13 3999

3999

FPGA高级时序综合教程

2023-08-07 16:07:55 9

9 为不同的corner: TT:Typical N Typical P FF:Fast N Fast P SS:Slow N Slow P FS:Fast N Slow P SF:Slow N Fast P 第一个

2023-11-01 15:57:42 9249

9249

今天想聊一聊STA相关的RC corner的问题。我先简单介绍一些什么是signoff的corner,然后重点聊一聊RC corner。

2023-12-05 14:11:12 3183

3183 建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2024-08-06 11:40:18 2365

2365

电子发烧友网站提供《FPGA电源时序控制.pdf》资料免费下载

2024-08-26 09:25:41 1

1 本文聚焦IBIS(I/O Buffer Information Specification)模型中的Corner(Typ/Min/Max)参数处理,系统分析Corner的定义规则及其对信号完整性

2025-04-23 16:10:37 1109

1109

电子发烧友App

电子发烧友App

评论