1.时序分析工具

时序分析工具用来检查同步电路设计是否满足给定的时序约束(包括建立时间Setup约束、保持时间Hold约束等),分为静态时序分析(Static Timing Analysis, DTA)两种方法。

静态时序分析是一种针对大规模门级电路进行时序验证的有效方法。它不需要测试向量,根据单元库中的时序模型和电路网表的拓扑结构,利用统计线网负载模型或SDF(Standard Delay Format,标准延时格式)文件中的电阻电容反标值计算时序路径延迟,检查每一个触发器的建立和保持时间是否满足设计要求。它的优点是覆盖率高,速度快;缺点是不能分析异步逻辑电路和模拟电路。

静态时序分析用工艺角(Corner)来反映不同的工艺/电压/温度等环境下电路的工作条件。工艺角下的单元库中定义了单元的时序模型(包括时序延迟值和时序约束值)。理论上时序收敛要保证芯片在各个工作场景(Scenario)下都没有时序违例,而实际操作中会选取某一个或几个特殊的工艺角去检查。

(1)单一模式:采用同一个工艺角条件,分析整个电路中时序路径的建立时间和保持时间。

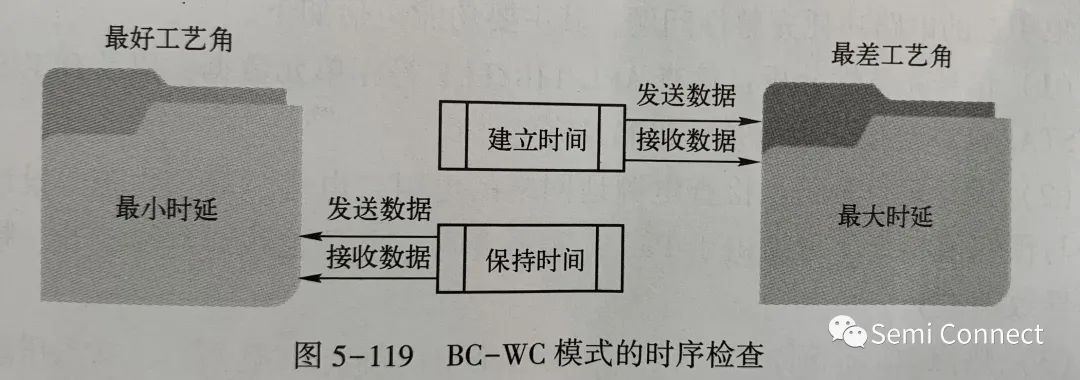

(2)BC- WC(Best-Case/Worst-Case)模式:用最好条件分析时序路径的保持时间,用最差条件分析时序路径的建立时间。BC- WC模式的时序检查如图5-119所示。

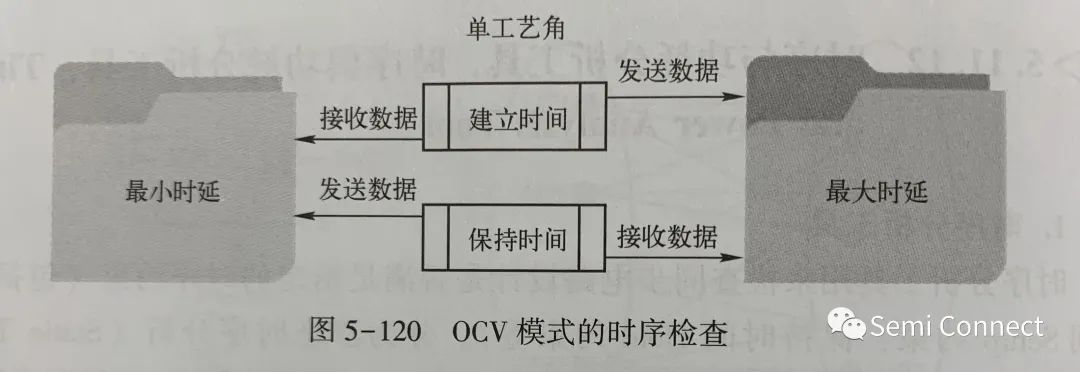

(3)OCV(On-Chip Variation)模式:利用放大及缩小倍数,分析建立时间时,令数据路径传输慢一些,时钟路径传输快一些;分析保持时间时,令数据路径传输快一些,时钟路径传输慢一些。OCV模式的时序检查如图5-120所示。

在28nm及更先进工艺条件下,新出现的AOCV(Advanced OCV)方法对OCV进行了扩展和延伸。它消除了OCV的不利因素,根据时序路径的不同逻辑层次深度和物理距离,查表得到每个单元具体的时延值。

为了应对芯片内部及芯片之间出现的系统性和随机性变化,时序分析工具又引入了统计静态时序分析(Statistical Static Timing Analysis,SSTA)方法。该方法利用概率分布函数,计算每个节点上每个信号的到达时间以减少不必要的时序过度修正。SSTA方法的难点在于概率函数难以计算,而且庞大的统计数据也造成了内存需求量增大,运行时间增长。

在16nm工艺条件以下的SoC设计以及物联网(IoT)超低电压设计中,以工艺角时延为基础的STA计算已经不再准确,而需要采用基于晶体管级仿真的动态时序分析方法。该方法采用并行化处理和特殊加速技术,针对关键时序路径进行高精度快速仿真,以获得时序路径准确的时序信息,帮助时序收敛。

2.功耗分析工具

功耗分析工具用于对电路中的温度、翻转频率、负载、电流、电压、功耗等进行统计报告,分析IR压降(IR-Drop)和电迁移(Electro Migration,EM)等现象引起的电路功耗完整性问题,其主要功能包括如下。

(1)信号完整性分析:检查APL/LIB/LEF等库单元数据,以及DEF/SPEF/IPF/STA/VCD等设计数据是否正确且完整。

(2)设计弱点分析:检查电源地网络的电阻、电容、峰值电流等设计指标是否与预期值相符(可能由于Pad分布不合理、电源地线布线不优化、频率过高等导致偏差)。

(3)热点(Hot Spot)分析:检查电路中的静态电阻电流、动态压降、功耗、电迁移等相关项是否满足签核标准,如有违反则定位问题所在区域并追溯其原因。

审核编辑 :李倩

-

触发器

+关注

关注

14文章

2065浏览量

63544 -

时序

+关注

关注

5文章

411浏览量

38999

原文标题:可编程逻辑电路设计—时序与功耗分析工具

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

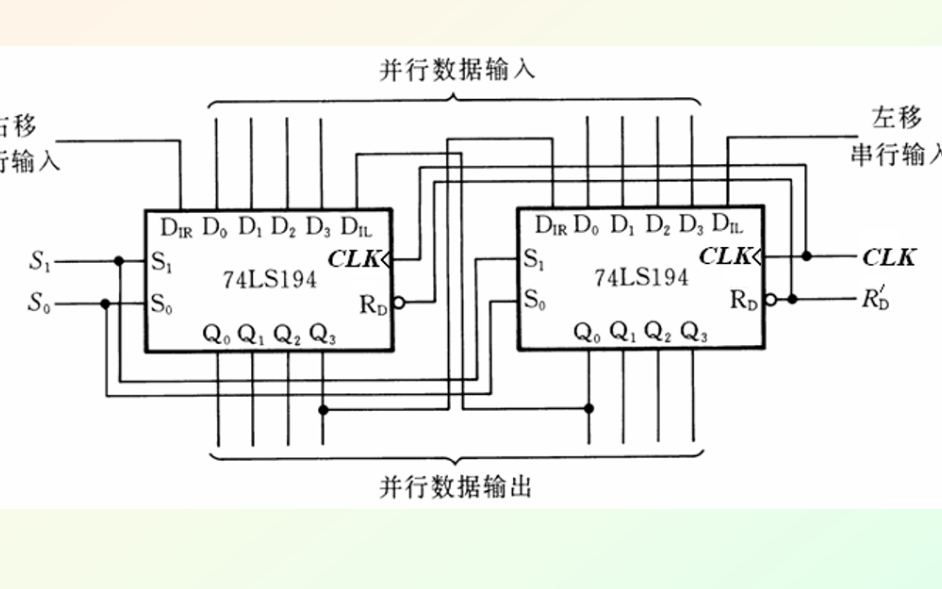

数字电路基础教程之时序逻辑电路的详细资料概述

数字电路教程之时序逻辑电路课件的详细资料免费下载

模拟电路教程之时序逻辑电路的课件资料免费下载

可编程逻辑电路设计之时序与功耗分析工具

可编程逻辑电路设计之时序与功耗分析工具

评论