1. 应用背景

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为FPGA设计的主要验证手段之一,不需要设计者编写测试向量,由软件自动完成分析,验证时间大大缩短,测试覆盖率可达100%。

静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。

进行静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。

2. 理论分析

2.1 静态时序分析的理论基础知识

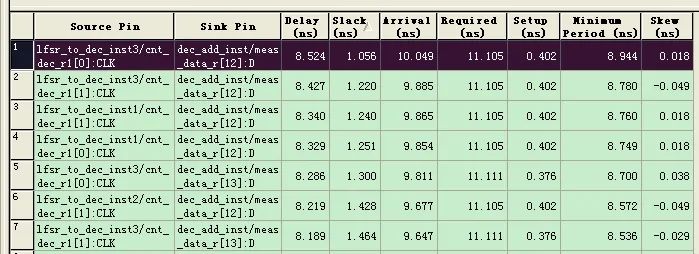

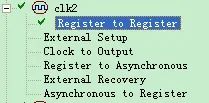

在进行正确的时序分析前,我们必须具备基本的静态时序的基本知识点,不然看着编译器给出的时序分析报告犹如天书。如图3.1所示,为libero软件给出的寄存器到寄存器模型的时序分析报告的截取,接下来我们会弄清楚每个栏目的数据变量的含义,以及计算方法。

图3.1 libero静态时序分析报告

2.1.1 固定参数launch edge、latch edge、Tsu、Th、Tco概念

1. launch edge

时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。

2. latch edge

时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。

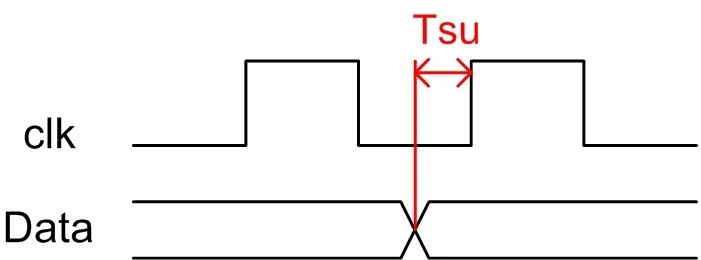

3. Clock Setup Time (Tsu)

建立时间(Tsu):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。如图3.2所示:

图3.2 建立时间图解

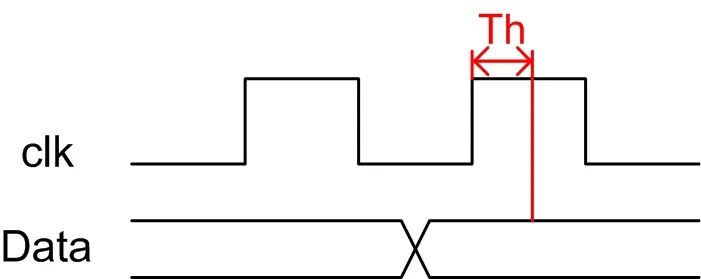

4. Clock Hold Time (Th)

保持时间(Th):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。保持时间示意图如图3.3所示:

图3.3 保持时间图解

5. Clock-to-Output Delay(tco)

数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

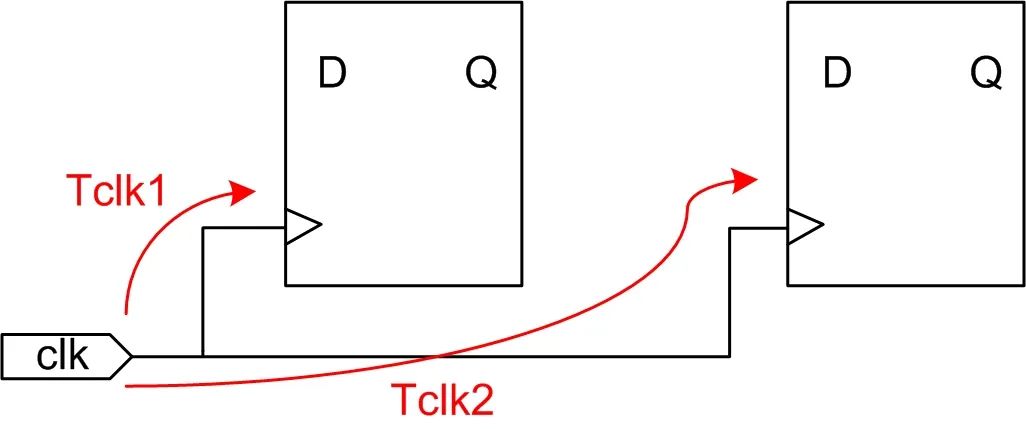

2.1.2 Clock skew

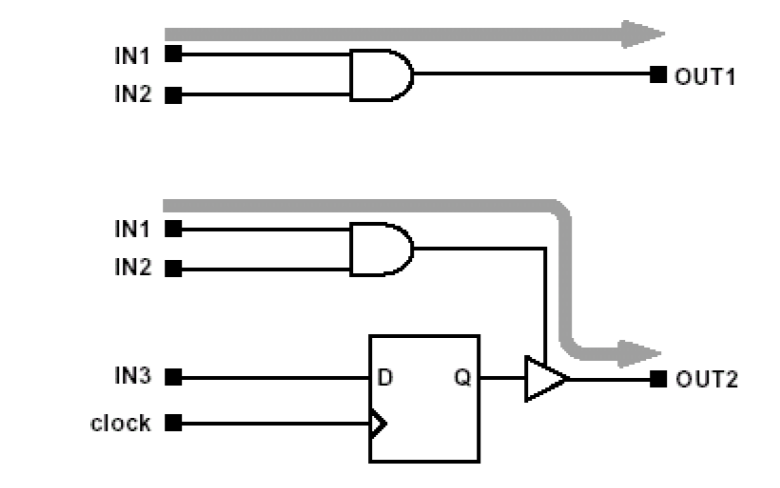

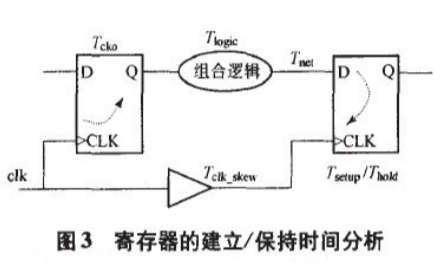

时钟偏斜(clock skew):是指一个时钟源到达两个不同寄存器时钟端的时间偏移,如图3.4所示:

图3.4 时钟偏斜

时钟偏斜计算公式如下:

Tskew = Tclk2 - Tclk1(公式3-1)

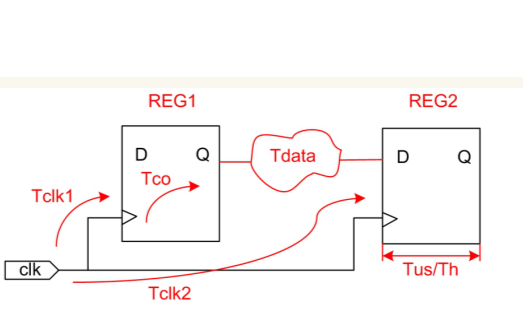

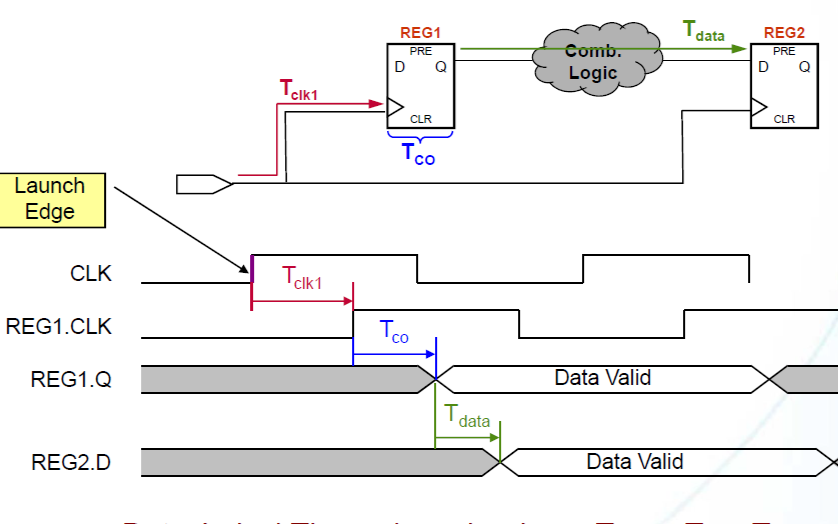

2.1.3 Data Arrival Time

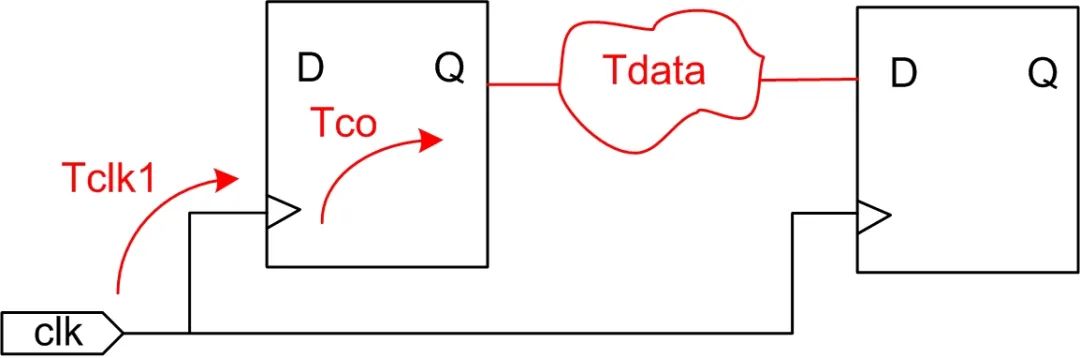

数据到达时间(Data Arrival Time):输入数据在有效时钟沿后到达所需要的时间。主要分为三部分:时钟到达寄存器时间(Tclk1),寄存器输出延时(Tco)和数据传输延时(Tdata),如图3.5所示

图3.5 数据到达时间

数据到达时间计算公式如下:

Data Arrival Time = Launch edge + Tclk1 +Tco + Tdata(公式3-2)

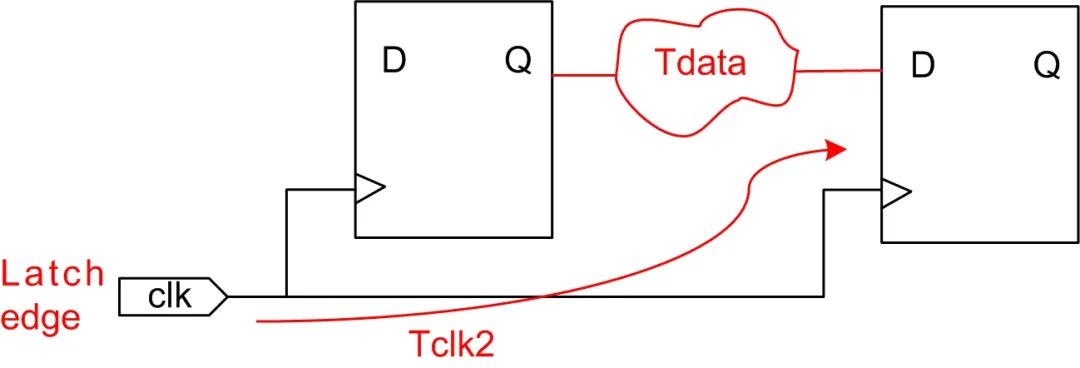

2.1.4 Clock Arrival Time

时钟到达时间(Clock Arrival Time):时钟从latch边沿到达锁存寄存器时钟输入端所消耗的时间为时钟到达时间,如图3.6所示

图3.6 时钟到达时间

时钟到达时间计算公式如下:

Clock Arrival Time = Lacth edge + Tclk2(公式3-3)

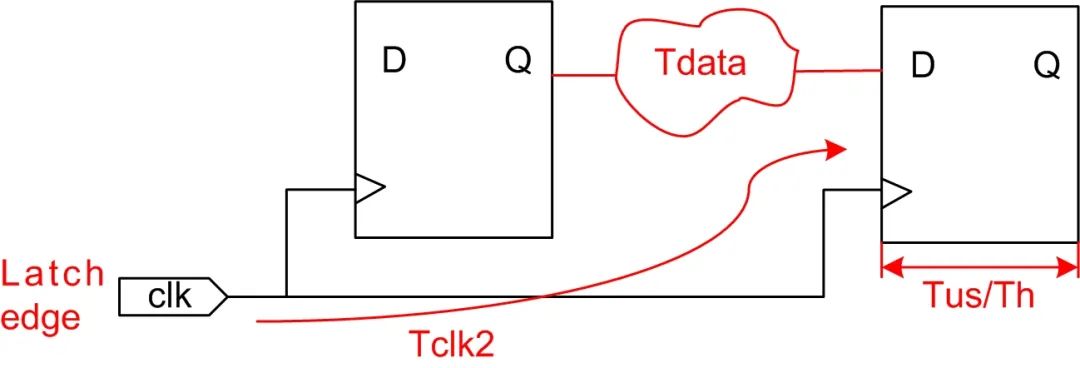

2.1.5 Data Required Time(setup/hold)

数据需求时间(Data Required Time):在时钟锁存的建立时间和保持时间之间数据必须稳定,从源时钟起点达到这种稳定状态需要的时间即为数据需求时间。如图3.7所示:

图3.7 数据需求时间

(建立)数据需求时间计算公式如下:

Data Required Time = Clock Arrival Time - Tsu(公式3-4)

(保持)数据需求时间计算公式如下:

Data Required Time = Clock Arrival Time + Th (公式3-5)

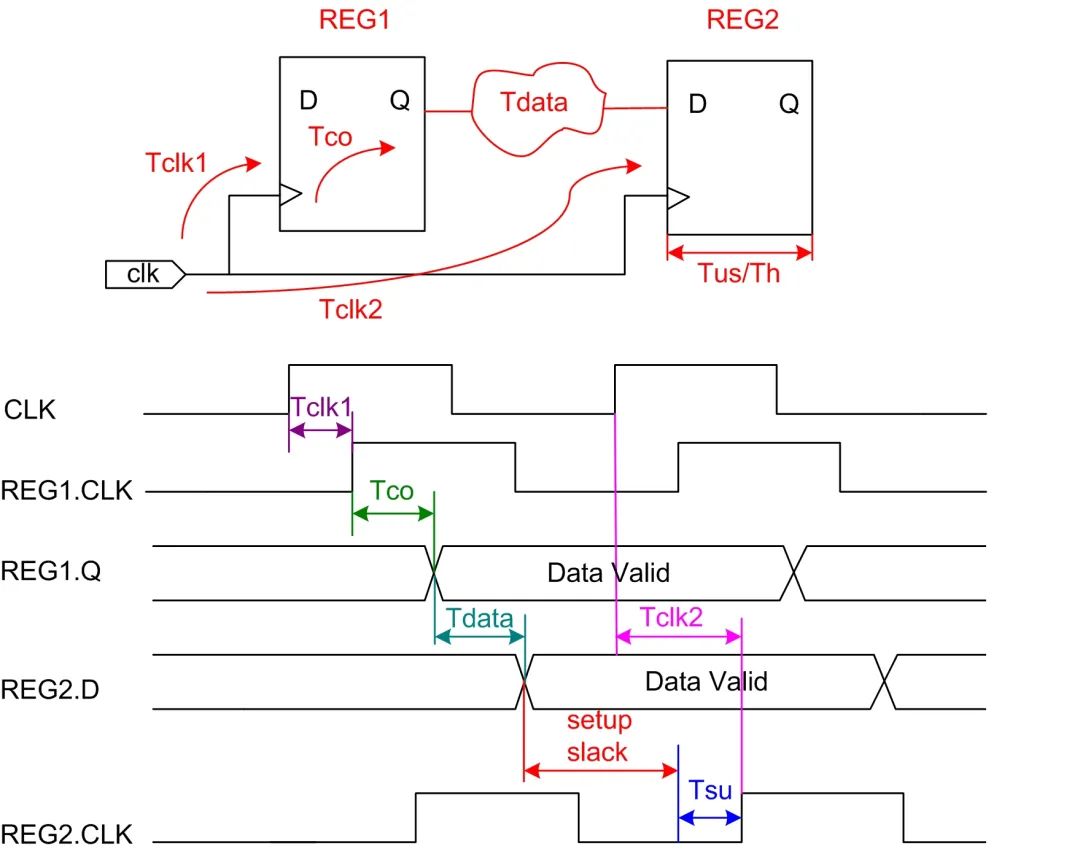

2.1.6 Setup slack

建立时间余量(setup slack):当数据需求时间大于数据到达时间时,就说时间有余量,Slack是表示设计是否满足时序的一个称谓。

图3.8 建立时间余量

如图3.8所示,建立时间余量的计算公式如下:

Setup slack = Data Required Time - Data Arrival Time(公式3-6)

由公式可知,正的slack表示数据需求时间大于数据到达时间,满足时序(时序的余量),负的slack表示数据需求时间小于数据到达时间,不满足时序(时序的欠缺量)。

2.1.7 时钟最小周期

时钟最小周期:系统时钟能运行的最高频率。

1. 当数据需求时间大于数据到达时间时,时钟具有余量;

2. 当数据需求时间小于数据到达时间时,不满足时序要求,寄存器经历亚稳态或者不能正确获得数据;

3. 当数据需求时间等于数据到达时间时,这是最小时钟运行频率,刚好满足时序。

从以上三点可以得出最小时钟周期为数据到达时间等于数据需求时间,的运算公式如下:

Data Required Time = Data Arrival Time(公式3-7)

由上式推出如下公式:

Tmin + Latch edge + Tclk2 - Tsu = Launch edge + Tclk1 + Tco + Tdata

最终推出最小时钟周期为:

Tmin = Tco + Tdata + Tsu -Tskew(公式3-8)

3. 应用分析

3.1 设置时钟主频约束

所有的静态时序分析都是在有约束的情况下编译器才给出分析报告,所以进行时序分析的第一步就是设置约束。

Libero软件设置时钟约束的途径三种,单时钟约束,多时钟约束和在Designer里面进行约束。

3.1.1 单时钟约束

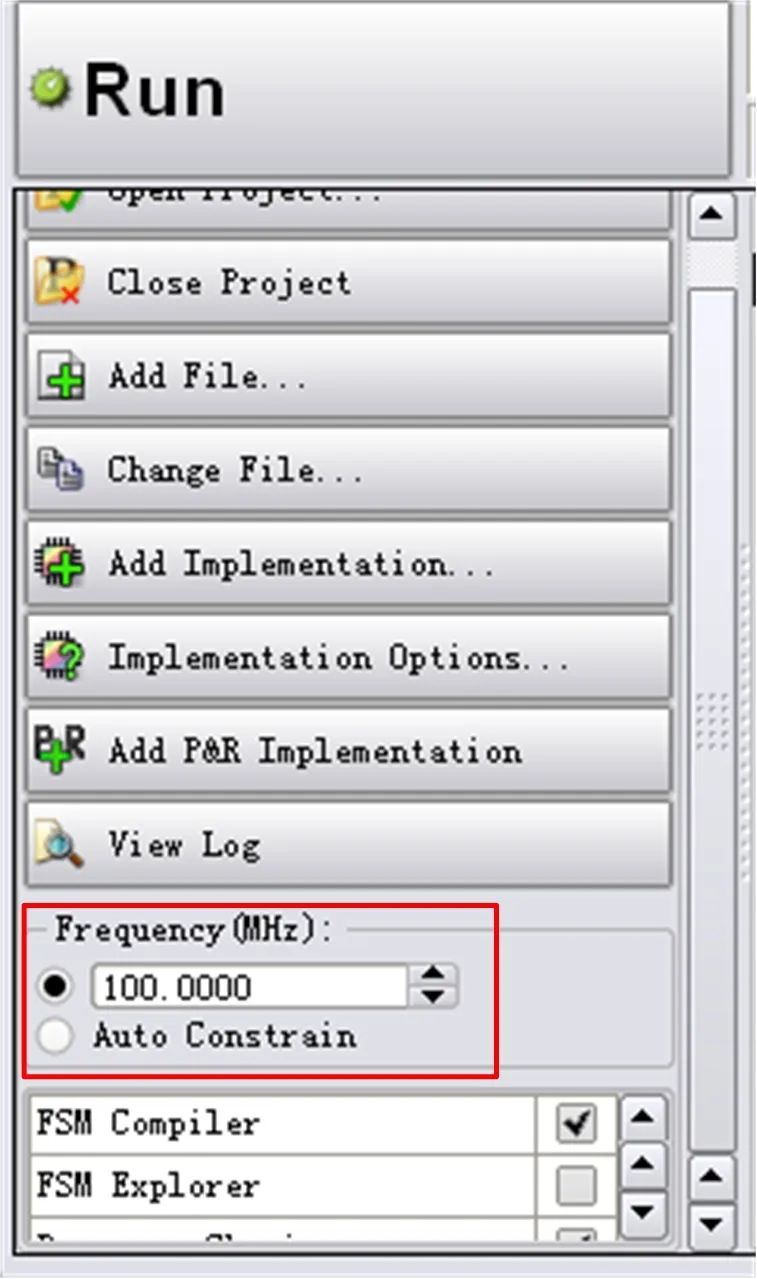

有时我们系统所有模块都采用同一个时钟,这种方式最为简单,直接在Synplify主界面上有个设置时钟约束的,如图4.1中红框所示:

图4.1 单时钟设置

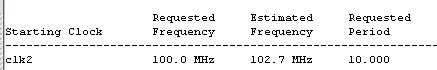

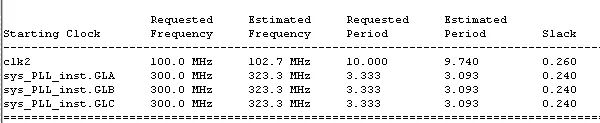

设置完成后,编译,通过Synplify时钟报告看初步时钟运行频率能否达到要求,时钟报告如图4.2所示,设定100Mhz,能运行102.7Mhz,满足时序。

图4.2 时序报告

3.2 多时钟约束

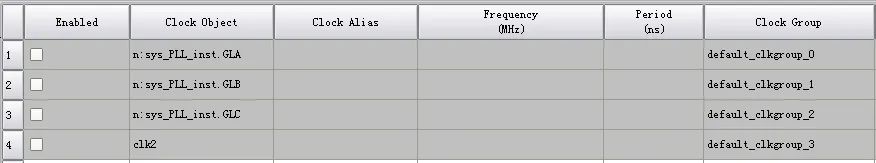

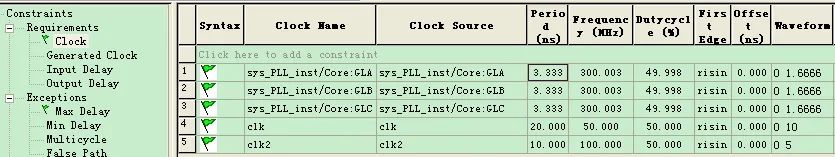

当系统内部模块采用了多个时钟时,那就需要进行多时钟约束了。首先需要打开设置界面,在Synplify中选择:File->New->Constraint File建立SDC文件,选择时钟约束如图4.3所示:

图4.3 多时钟约束

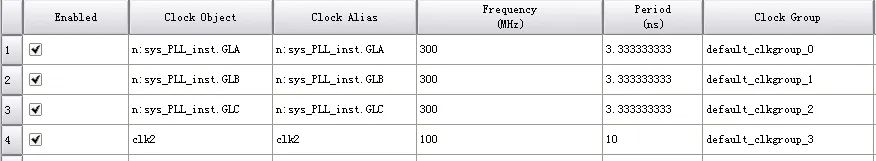

对时钟进行如下约束后保存SDC文件,约束如图4.4所示

图4.4 多时钟约束完成

3.3 Designer SmartTime时钟约束

时钟约束除了在Synplify中可以约束外,还可以在Designer SmartTime中设置时钟约束,打开Designer Constraint,选择Clock进行针对每个使用时钟的设置,如图4.5所示:

图4.5 Designer时序约束

4.4 时序报告分析

3.4.1 Synplify时序报告

当约束了时序后,需要观察时序报告,看时钟能否达到我们需要的时钟,首先观察Synplify综合报告。以多时钟约束为例子,从Synplify得到的时序报告如图4.6所示:

图4.6 多时钟约束时序报告

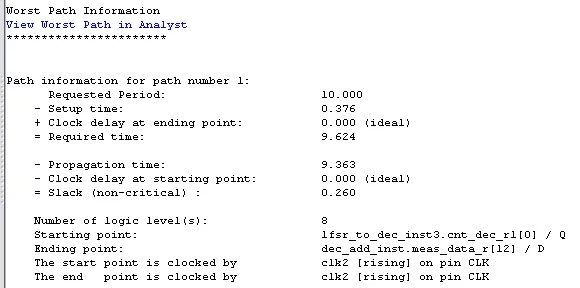

由上图可知时序都满足约束,未出现违规,可以在下面的报告中查看最差路径,如图4.7所示是clk2的最差路径。

图4.7 最差路径

3.4.2 Designer SmartTime时序分析报告

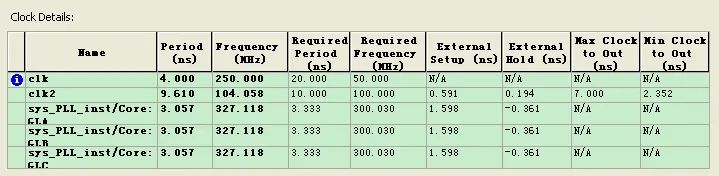

当设计经过Synplify综合给出网表文件后,还需要Designer进行布局布线,通过布局布线优化后的时序会有变化,因此,还需要分析布局布线后的时序,打开Designer->Timing Analyzer查阅整体时序分析报告如图4.8所示:

图4.8 布局布线后时序报告

由Synplify综合后的报告和Designer进行布局布线后的报告可以看出,布局布线后优化了一些时序,特别是clk2时钟,通过布局布线后优化到了184Mhz,完全满足时序。

3.4.3 详细时序报告图

通过Synplify综合后的和Designer进行布局布线都只是看到了一个大体的时序报告,当我们需要分析时序时候必须观察仔细的时序报告,在SmartTime中提供这种报告功能,以clk2分析为例,在Timing Analyzer找到如下区域。

图4.9 时序报告选择

如图4.9所示,选择寄存器到寄存器进行分析时钟主频。

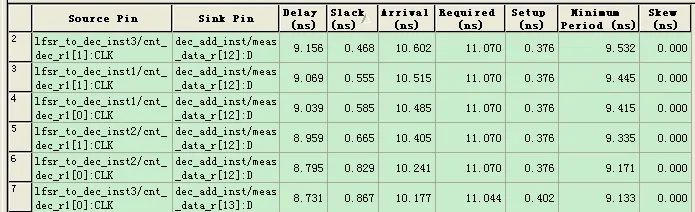

图4.10 寄存器到寄存器分析

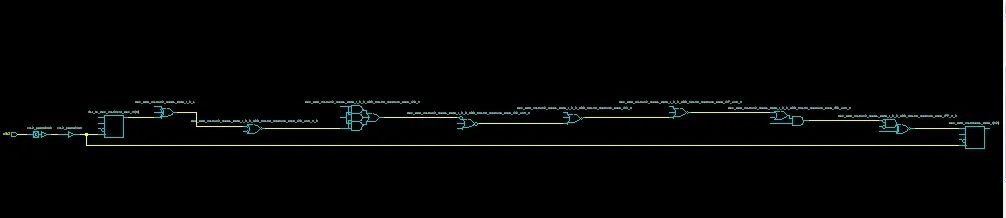

如图4.10所示,时序报告中给出了数据延时,时序余量,数据到达时间,数据需求时间,数据建立时间,以及最小周期和时钟偏斜等信息,有了上一节的时序分析基础知识,我们完全能看懂这些数据代表的意义,这样对我们时序分析就知己知彼,进一步双击其中一条路径,还会给出这条路径的硬件电路图,如图4.11所示,有了这些详细的时序报告,对设计进行调整更加清晰。

图4.11 硬件路径

审核编辑:汤梓红

-

FPGA

+关注

关注

1655文章

22283浏览量

630241 -

STA

+关注

关注

0文章

52浏览量

19527 -

静态时序分析

+关注

关注

0文章

29浏览量

9771

原文标题:FPGA静态时序分析模型——寄存器到寄存器

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA quartus ii里的静态时序分析

使用pt对fpga进行静态时序分析需要哪些文件

静态时序分析在高速 FPGA设计中的应用

FPGA进行静态时序分析

FPGA静态时序分析详解

FPGA静态时序分析详解

评论