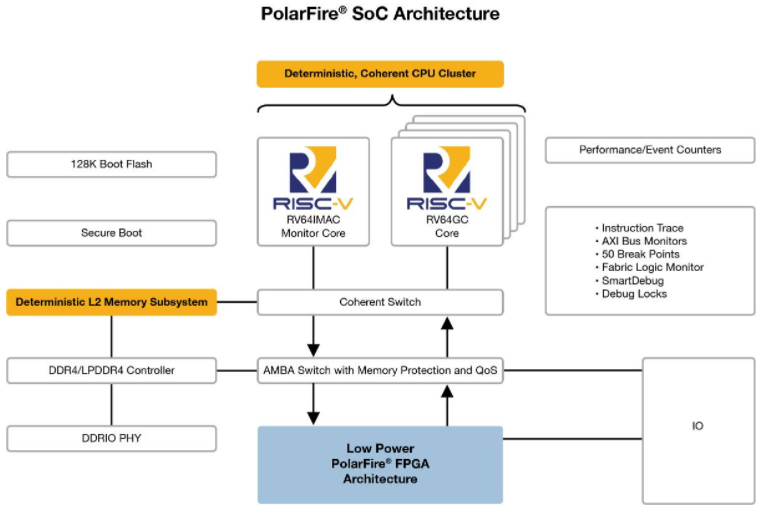

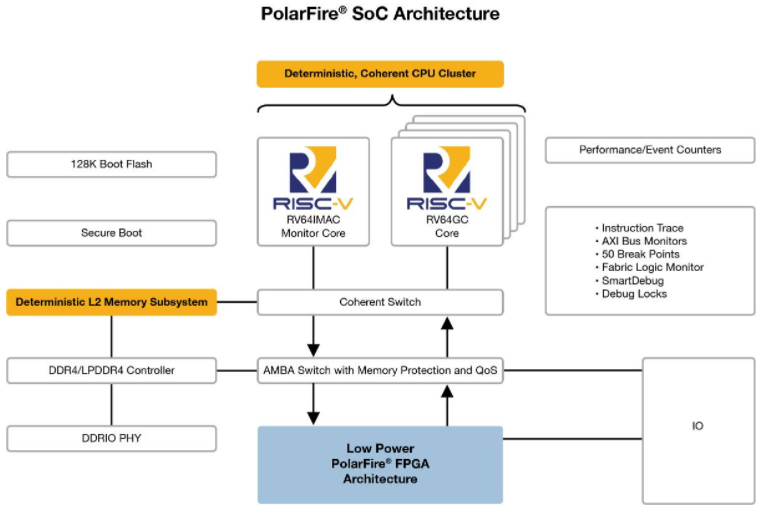

Microchip Technology Inc.(美国微芯科技公司)启动了PolarFire®片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-11 16:55:15 1608

1608 的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

2020-10-14 15:17:19 4185

4185

直接使用C、C++或 System C 来对 Xilinx 系列的 FPGA 进行编程,从而提高抽象的层级,大大减少了使用传统 RTL描述进行 FPGA 开发所需的时间。

2025-04-16 10:43:12 1432

1432

Microchip 今日推出经优化的耐辐射RT PolarFire FPGA,为新兴的高性能太空应用市场带来具备上述功能的新产品。

2019-10-23 17:04:10 1286

1286 Microsemi PolarFire FPGA视频和成像套件配备带有板载PolarFire FPGA的PolarFire视频与成像板以及一个双摄像头传感器板。

2019-11-08 11:23:33 1424

1424 Microchip开发系统高级总监Rodger Richey表示:“目前,许多MCU产品的功能安全工具成本非常高,Microchip推出的功能安全产品的价格仅为某些竞争性解决方案的三分之一,而且提供卓越的全球技术支持,助力客户加快产品上市并进一步简化开发流程。”

2020-01-21 00:27:00 4723

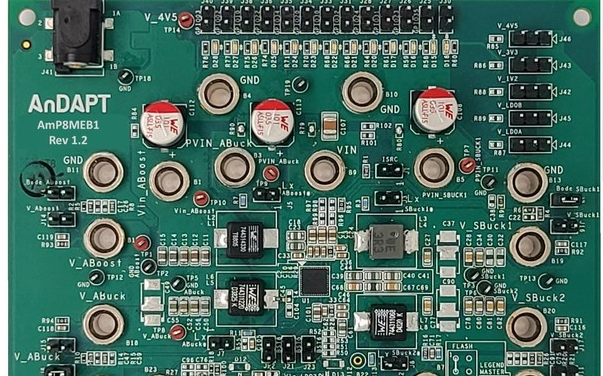

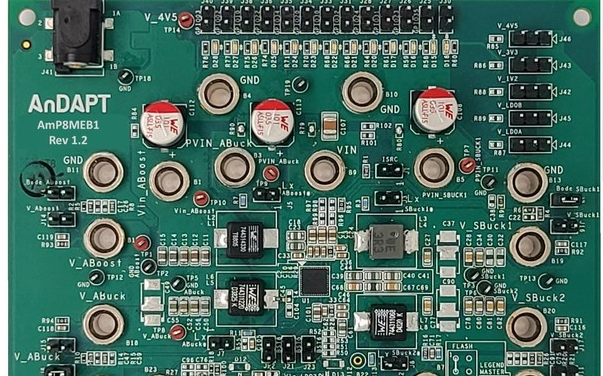

4723 AnDAPT现在支持使用集成、灵活和可编程的AmP电源管理IC为Microchip PolarFire FPGA供电。

2022-01-19 10:46:27 2559

2559

合集关键字 :Mi-V峰会;Microchip;Polarfire SOC FPGA;Mercury+ MP1; RISC-V 今年, Enclustra 发布了其首款基于 Microchip

2022-08-15 15:20:25 1181

1181

的高级语言(如C++和C++)的准入,这一点让众多软件工程师甘之如饴。与硬件描述语言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程师掌握的工具。当然,它也有局限性:语言限制,就像非可合成

2021-07-10 08:00:00

`为客户提供完美的硅芯片解决方案是MICROCHIP坚持不懈的目标。但我们不只局限于提供硅芯片,还需要编程器、编译器、参考设计、函数库、应用笔记和评估板等支持工具,以助您最高效地完成评估和产品开发

2011-03-09 14:59:00

的设计工具和资源,以帮助开发人员采用和改进 RISC-V 应用程序设计。这些工具可与各种硬件套件结合使用——用于 PolarFire FPGA 的 PolarFire 评估套件和Icicle 套件

2021-09-07 17:59:56

、基于 RISC-V 的 PolarFire® SoC FPGA 打造,汇集了众多的 Mi-V 合作伙伴,助力加速不同行业的客户设计部署和商业应用。 设计人员现在可以开始开发和评估实时操作系统(RTOS

2020-09-25 11:39:42

Microchip提供了一系列高度集成的开发工具,可以简化应用程序的开发过程。这些工具分为核心开发工具和附属工具。基本开发工具主要有:•MPLAB®集成开发环境

2011-03-08 16:50:21

目前有一个算法库 用的c++ 用ccs在dsp上可以调试

现在希望把库放在8168的dsp上 需要将c++转换成c 有个工具

mmCC C++-to-C Translator、

不知道论坛里有没有 或者大家谁有

如果找不到mmcc

那么 8168上dsp用c调用c++库 有没有可行性

2018-06-21 13:14:22

MYC-CZU3EG/4EV/5EV-V2核心板及开发板

在MYIR 的 ZU3EG 开发平台上提供了一种高效的解决方案。利用 FPGA 独特的灵活性和低功耗优势,助力未来 AIoT 设备的普及和智能升级。

2024-12-06 17:18:02

模拟过程完成没有0错误,但在合成期间显示错误。我无法找到错误。我在合成期间在HLS工具中收到这样的错误“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

TI CC2541开发套件

2023-03-25 01:27:25

智能化设计平台,为用户提供了一个接触和操作底层算法的便捷途径。

用户无需进行复杂的代码编写,可以一键套用工程模版,也可以通过图形化界面自定义控制算法,就能够轻松在实验室有限的环境中制作实物电路,快速开发

2025-08-14 11:30:35

HiHope 满天星智能家居开发套件

2023-03-28 13:07:10

润和满天星系列Pegasus智能小车开发套件,基于海思Hi3861V100芯片,支持OpenHarmony轻量系统,实现巡线、避障功能通过寻迹模块获取路面轨道数据,运用寻迹算法使得智能小车可以按照固定轨道运行

2023-03-28 13:07:10

加利福尼亚州,圣何塞— 2014年9月3日– S2C公司今日宣布TAI Player Pro 5.1版本正式发布。此次最新版本将帮助用户加速FPGA原型开发、提高工程师的生产力,以及实现最高的原型

2019-07-02 06:23:44

/C++的编程技巧者优先, 对图像信号处理、识别、编解码等算法有较好的基础;4、有良好的英文阅读能力; 5、具有良好的团队合作精神和刻苦钻研精神,责任心强,能承受一定的工作压力;6、有智能交通行业产品DSP开发经验者优先。工作地点:武汉有意向者请窗我:QQ:1940783351

2013-07-16 11:07:23

的高级语言(如C++和C++)的准入,这一点让众多软件工程师甘之如饴。与硬件描述语言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程师掌握的工具。当然,它也有局限性:语言限制,就像非可合成

2021-07-06 08:00:00

/C++进行设计,然后由Vivado HLS编译器将C代码综合成HDL描述,最后再进行逻辑综合得到网表,这个网表最终会被映射到具体的FPGA器件上。就像C语言或者其他高级语言针对不同的处理器架构有着

2020-10-10 16:44:42

拼接算法试用计划:申请理由本人从事图像处理,图像编码算法有十年开发经验,熟悉xilinx FPGA的编程,曾设计过ISP算法,由于有监控场景需要宽幅图像,想借助发烧友论坛和米尔MYD-C7Z020平台

2019-10-30 17:03:31

库文件,甚至可以引进HDL程序,并进行仿真,最终生成网表文件,放到FPGA中执行。软件算法工程师不需要特别的培训,利用他们熟悉的C语言就可以直接进行硬件开发,减轻了硬件开发的瓶颈和压力。随着算法描述

2015-01-13 16:34:40

针对目标FPGA优化的RTL代码。尽管英特尔的HLS工具在现场的使用率比Xilinx的Vivado HLS少得多,但随着HLS编译器为英特尔One API软件开发平台的“ FPGA”分支提供动力,我们

2024-03-23 16:48:53

优化 FPGA HLS 设计

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

介绍

高级设计能够以简洁的方式捕获设计,从而

2024-08-16 19:56:07

,我们一直在使用Vivado给我们提供的IP或者使用硬件描述语言制作 IP 。今天我们将讲解如何使用HLS-高级综合语言来创建属于我们自己的IP。我们将使用的工具称为Vitis HLS,此后称为 HLS

2022-09-09 16:45:27

将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架对Xilinx可编程逻辑器件进行开发,可加速算法开发的进程,缩短产品上市时间。HLS基本开发流程如下:(1) HLS工程新建/工程

2021-02-19 18:36:48

。

Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx

2023-08-24 14:40:42

。Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx

2023-01-01 23:52:54

(High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加速算法开发的进程,缩短

2023-01-01 23:46:20

(High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加速算法开发的进程,缩短

2023-08-24 14:54:01

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 09:38:32

和生成比特流以对FPGA进行编程4 - 将比特流导入并阻塞到SDK中,基于此生成板级支持包(BSP)并与Zedboard连接。顺便说一下,SDK的目标是成为我在Vivado HLS中的测试平台吗?即在计算机中观察Zedboard产生的结果是否为例外情况。

2020-03-24 08:37:03

。Vivado HLS作为该套件的一个组件,能帮助设计人员将采用C/C++语言开发的算法编译为RTL,以便在FPGA逻辑中运行。Vivado HLS工具非常适用于嵌入式视觉设计。在此流程中,您用C/C++

2014-04-21 15:49:33

您好,我目前正在尝试使用Vivado HLS在FPGA上合成加密算法。我根据需要拆分了C ++代码并包含了一个测试平台,但是当我尝试模拟代码时,我得到一个错误,说找不到测试平台。我附上了错误图片和项目档案,希望有人能帮我找到解决方案。谢谢!LBlock_fpga.zip 48 KB

2020-05-15 09:26:33

进行编译的。本文仅验证了采用高级语言开发FPGA的可行性,还有很多优化工作待完善,仅以此文为大家提供一个新的视角,为软件开发人员利用FPGA进行算法加速做前期调研,欢迎感兴趣的同事共同交流。

2017-09-25 10:06:29

客户能够在小至 11 × 11 毫米的封装尺寸上实施解决方案。Microchip 的 PolarFire SoC FPGA Icicle 工具包非常适合智能嵌入式成像、物联网、工业自动化、国防、汽车

2021-03-09 19:48:43

Visual C++ 6.0 高级编程,免费下载:全面介绍了Visual C++ 6.0的中高级编程技术,其内容主要有:内存管理、高级图形处理、使用Internet、创建多线程程序、创建ActiveX和DLL、使用

2009-07-12 15:25:07 0

0 Intel Agilex® F系列FPGA开发套件Intel Agilex® F系列FPGA开发套件设计用于使用兼容PCI-SIG的开发板开发和测试PCIe 4.0设计。该开发套件还可通过硬核处理器

2024-02-27 11:51:58

MIDI合成算法及其FPGA实现.

2012-04-16 13:57:38 44

44 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 进行编写解析算法,把G 代码作为一个对象,用类机制实现其解析功能,并使用GCC 作为其编译器,提高编译效率。可直接应用嵌入式,脱离PC+运动控制卡的限制。通过实验的测试,以ARM 开发板为验证实验平台,以arm-none-eabi-gcc 为编译工具,验证C++解

2016-07-21 16:36:32 0

0 FPGA学习资料教程之Xilinx-FPGA高级开发工具,感兴趣的可以看看。

2016-09-01 15:27:27 0

0 众所周知,HLS是Xilinx于几年前推出的一个高级综合工具,可以直接把C/C++代码,转换成可综合的verilog/VHDL代码。听起来很高级,是不是?。但看新鲜的人多,愿意吃螃蟹的人却很少。这里

2017-02-08 05:07:20 2467

2467

HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

2019-10-12 17:34:00 2937

2937

提供支持。SDAccel允许开发人员用 OpenCL™、C和C++语言描述他们的算法,并直接编译到赛灵思FPGA加速板。托管的赛灵思SDAccel™ 开发环境不仅会加速FPGA开发进

2017-02-08 16:06:08 494

494 高层次综合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA设计工具,它能让用户通过编写C/C++等高级语言代码实现RTL级的硬件功能。随着这款工具

2018-07-14 06:42:00 8006

8006 Android C++高级编程----使用NDK

2017-03-19 11:23:45 3

3 测试用的大量采样数据,完成对硬件系统原型的评估。对于I/Q压缩算法等类似高数据吞吐量的应用,采用Vivado HLS工具进行测试评估更加的方便。

2017-11-17 02:25:41 1856

1856

者对算法FPGA的实现难度。其中包括:

使用VivadoHLS开发效率比手写RTL实现快5-10倍,而实现的FPGA资源效率与手写RTL接近

由于C/C++仿真验证比传统FPGA RTL要快100倍,Vivado HLS实现可以大大缩短用户的代码开发时间和仿真验证时间,从而大幅提高生产效率。

2017-11-17 17:47:43 4363

4363

如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado® 设计套件高层次综合(HLS) 工具是创建高性能加速器的极好资源。通过向C 语言高级算法描述中添加一些编译指示,就可以在赛灵思FPGA 上快速实现高吞吐量的处理引擎。

2017-11-17 18:12:01 2315

2315 Vivado HLS配合C语言等高级语言能帮助您在FPGA上快速实现算法。 高层次综合(HLS)是指自动综合最初用C、C++或SystemC语言描述的数字设计。工程师之所以对高层次综合如此感兴趣,不仅是因为它能让工程师在较高的抽象层面上工作,而且还因为它能方便地生成多种设计解决方案。

2019-10-06 10:44:00 1849

1849

、边缘模糊等级和脉冲噪声等指标评估基于该算法图像处理效果。与传统时域算法作对比,对比结果表明该算法在处理效果和运算速度上的优异性。基于Zedboard开发板,运用Vivado HLS高级综合工具将算法的C程序综合成硬件IP,并搭建了包含ARM处理器和VGA等

2017-12-12 14:07:38 2

2 本文介绍了PolarFire FPGA主要特性,低功耗特性,可靠特性和安全特性,框图,以及PolarFire FPGA评估板硬件特性,框图,电路图和元件表以及PCB元件布局图。

2018-06-17 18:06:00 6952

6952

应用大比拼开擂 基于vivado HLS的帧差图像实现 基于FPGA的实时移动目标的追踪 类似嵌入式 C/C++/OpenCL 应用开发的体验 SDSoC 开发环境可为异构 Zynq SoC 及 MPSoC 部署

2018-05-21 14:16:00 2572

2572 HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。

2018-06-04 01:43:00 7738

7738

子系统以及完整的 Vivado 实现工具套件,使主流用户能够方便地采用生产力最高、最先进的C 语言和 IP设计流程。结合最新 UltraFast 高级生产力设计方法指南,相比采用传统方法而言,用户可将生产力提升 10-15 倍。全新HLx 版本将作为 Vivado 设计套件的免费升级版提供。

2018-08-17 11:43:00 4072

4072 美高森美公司(Microsemi ) 宣布提供低成本IGLOO 2 FPGA评测工具套件,为客户提供PCI Express (PCIe)兼容外形尺寸评测平台。这款功能齐全的工具套件可让设计人员快速评测美高森美最近发布的IGLOO2 FPGA器件的集成度、低成本、安全性、即时性和高可靠性特性。

2018-09-18 16:49:00 1914

1914 关键词:Actel , Fusion , 高级 , 工具 , 套件 爱特 (Actel) 正式付运Fusion高级开发工具套件,协助设计人员开发系统和功率管理应用。该工具套件带有Actel

2018-10-24 20:44:01 1031

1031 了解如何使用GUI界面创建Vivado HLS项目,编译和执行C,C ++或SystemC算法,将C设计合成到RTL实现,查看报告并了解输出文件。

2018-11-20 06:09:00 4500

4500 使用Spartan-6 FPGA消费类视频套件加速DTV设计中高级视频算法的开发。

与消费者部门主管Harry Raftopoulos近距离观看套件。

2018-11-28 06:15:00 2397

2397 尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Vivado HLS的调试环境的,但是C 描述的算法却是不可以的。

2019-07-29 11:07:16 6103

6103

Xilinx 战略应用高级工程师。专注于 C/C++ 高层次综合,拥有多年利用 Xilinx FPGA 实现数字信号处理算法的经验,对 Xilinx FPGA 的架构、开发工具和设计理念有深入的理解。

2019-08-01 15:30:49 2416

2416 接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写

2019-07-31 09:45:17 7434

7434

Microchip启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-16 15:16:21 1053

1053 Microchip启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-26 15:39:03 1460

1460 ,Microchip Technology Inc.(美国微芯科技公司)宣布推出业界首款基于 RISC-V 的SoC FPGA开发工具包。这款名为Icicle 的开发工具包专为业界领先的低功耗、低成本

2020-09-24 09:37:29 4146

4146 2019年,Microchip Technology Inc.(美国微芯科技公司)发布了用于CryptoAuthentication系列的Trust Platform(可信平台),这是业界

2021-05-14 10:21:27 2244

2244 算法都是由开发人员使用C++语言原生开发的,而他们对底层FPGA硬件知之甚少或一无所知。为了支持这一重要的开发群体,Microchip Technology Inc.(美国微芯科技公司)推出了名为SmartHLS的HLS设计工作流程,成为其PolarFire FPGA系列产品的新成员。

2021-09-07 11:50:27 7309

7309 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 3450

3450 由于它是一个开放标准,为 PolarFire 设备开发的代码可以扩展和缩减 Microchip FPGA SoC 产品组合以及其他 RISC-V RV64GC 目标,而无需从头开始。

2022-06-01 10:18:56 2348

2348

在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 8680

8680 出于这个原因,Microchip 继续在其 PolarFire FPGA SoC 系列中进行创新——推出的具有 25K 逻辑元件和硬化四核 RISC-V CPU 的 MPFS025 SoC。

2022-07-10 15:42:15 1538

1538

HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 2261

2261

Vitis HLS 工具能够将 C++ 和 OpenCL 功能部署到器件的逻辑结构和 RAM/DSP 块上。在 GitHub 上提供 Vitis HLS 前端为研究人员、开发人员和编译器爱好者开启了无限可能的新世界,使他们可以利用 Vitis HLS 技术并根据其应用的特定需求进行修改。

2022-08-03 09:53:58 1602

1602 1、HLS简介 HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境中来

2022-12-02 12:30:02 7407

7407 推理解决方案的快速开发平台 》的在线研讨会。 VectorBlox平台是一款软件开发工具包(SDK),可实现基于PolarFire FPGA的机器学习(ML)推理。这款SDK有多种工具,无需对FPGA

2022-12-12 20:25:08 1322

1322 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 6467

6467 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 1730

1730

。 这些新工具进一步扩大了Microchip FPGA全面的工具和服务工具包,支持成熟的PolarFire系列器

2023-06-08 08:05:02 1234

1234 。 这些新工具进一步扩大了Microchip FPGA全面的工具和服务工具包,支持成熟的PolarFire系列器件

2023-06-15 09:05:01 873

873 该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的时间内对测试图像进行去噪,同时消耗不到 25% 的可用 PL 资源。特征如下:

2023-07-03 09:06:43 1551

1551

安全当前已成为各垂直市场所有设计的当务之急。今天,有进一步证据向系统架构师和设计人员证明,使用Microchip Technology Inc.(美国微芯科技公司)的PolarFire FPGA

2023-09-05 11:50:01 1330

1330 Microchip推出针对智能边缘设计的定制PolarFire FPGA和SoC解决方案堆栈,以加快开发速度,同时推动FPGA的采用。 为了加快智能边缘设计,Microchip Technology

2023-10-26 18:09:50 2340

2340 。XilinxVivadoHLS(High-LevelSynthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架对Xilinx可编程逻辑器件进行开发,可

2023-01-03 15:47:38 7

7 很多人都比较反感用C/C++开发(HLS)FPGA,大家第一拒绝的理由就是耗费资源太多。但是HLS也有自己的优点,除了快速构建算法外,还有一个就是接口的生成,尤其对于AXI类接口,按照标准语法就可以很方便地生成相关接口。

2024-07-16 18:01:03 1940

1940

电子发烧友网站提供《使用航天级电源元件为Microchip RT PolarFire FPGA供电.pdf》资料免费下载

2024-09-02 10:56:54 0

0 和灵感。 以下是本周新品情报,请及时查收: 嵌入式系统快速开发 Microchip Technology PolarFire SoC Discovery套件 贸泽电子即日起

2024-10-17 14:36:35 1408

1408

Microchip Technology推出了PolarFire® FPGA以太网传感器桥,以帮助开发人员创建与NVIDIA Holoscan传感器处理平台兼容的人工智能(AI)驱动的传感器处理系统

2024-11-19 09:29:16 1724

1724 为了帮助开发人员构建人工智能(AI)驱动的传感器处理系统,Microchip Technology Inc.(微芯科技公司)发布了支持NVIDIA Holoscan 传感器处理平台的PolarFire FPGA 以太网传感器桥接器。

2024-11-25 16:43:16 1457

1457 在 2025 国际嵌入式展(Embedded World 2025)上,全球 FPGA 创新技术领导者 Altera 发布了专为嵌入式开发者打造的最新可编程解决方案,以进一步突破智能边缘领域的创新

2025-03-12 09:47:29 2400

2400 Microchip PolarFire SoC FPGA通过 AEC-Q100汽车级认证 Microchip

2025-03-31 19:26:56 2181

2181 当前市场中,物料清单(BOM)成本持续攀升,开发者需在性能和预算间实现优化。鉴于中端FPGA市场很大一部分无需集成串行收发器,Microchip Technology Inc.(微芯科技公司)正式发布PolarFire Core现场可编程门阵列(FPGA)和片上系统(SoC)。

2025-05-23 14:02:15 1369

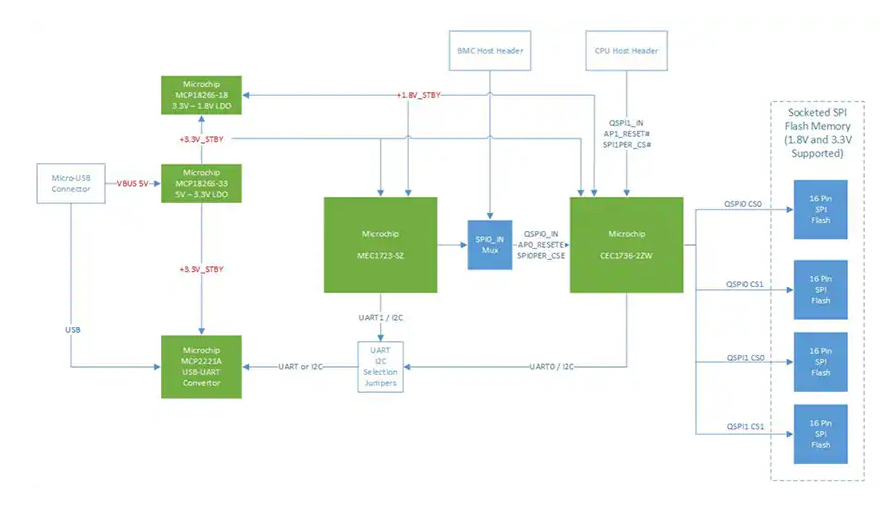

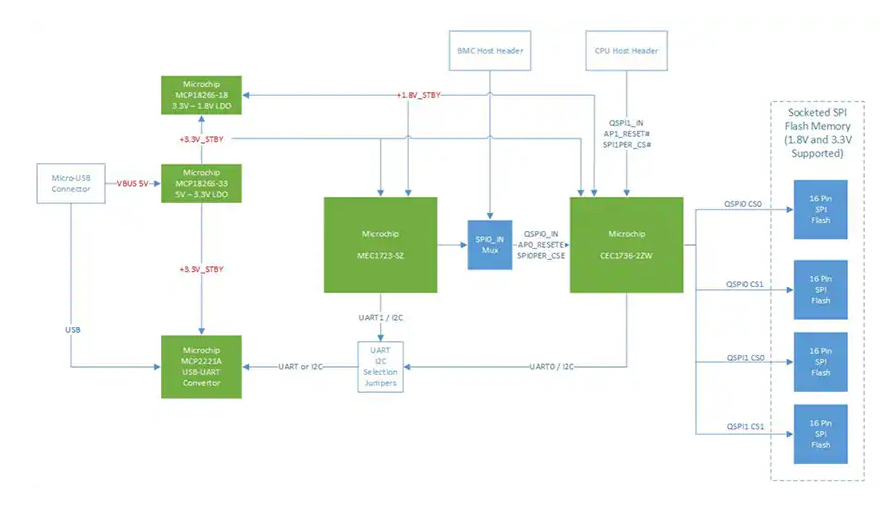

1369 Microchip Technology CEC173x评估套件 (EV42J24A) 是用于CEC173x可信扩展板系列平台信任根控制器的评估和开发套件。该板与TPDS(信任平台设计套件)工具配合

2025-09-29 14:55:33 638

638

电子发烧友App

电子发烧友App

评论