所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。典型的锁存器逻辑电路是 D 触发器电路。 PS:锁存信号(即对LE赋高电平时Data端的输入信号)。锁存,就是把信号暂存以维持某种电平状态。

2017-10-30 14:35:53 63605

63605

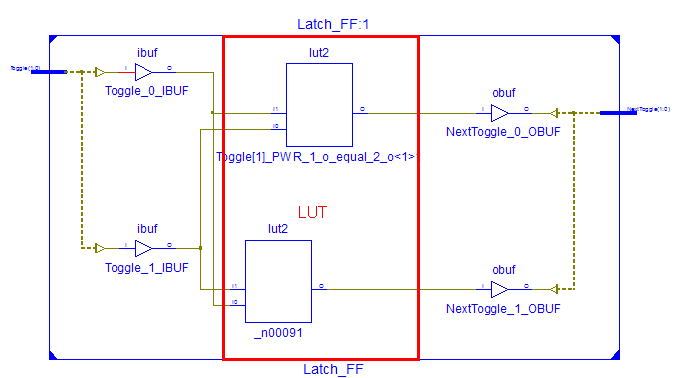

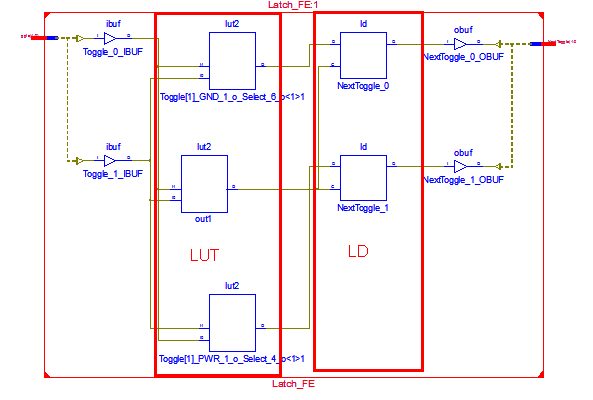

文章都对锁存器有个误解,我们后面会详细说明。 这篇文章,我们包含如下内容: ①锁存器、触发器和寄存器的原理和区别,为什么锁存器不好? ② 什么样的代码会产生锁存器? ③ 为什么锁存器依然存在于FPGA中? 锁存器、触发器和寄存器的原理和区别,为什么锁存器

2020-11-16 11:42:00 9314

9314

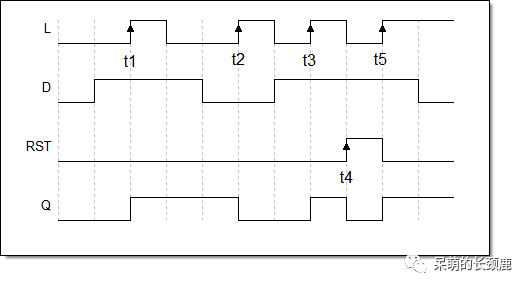

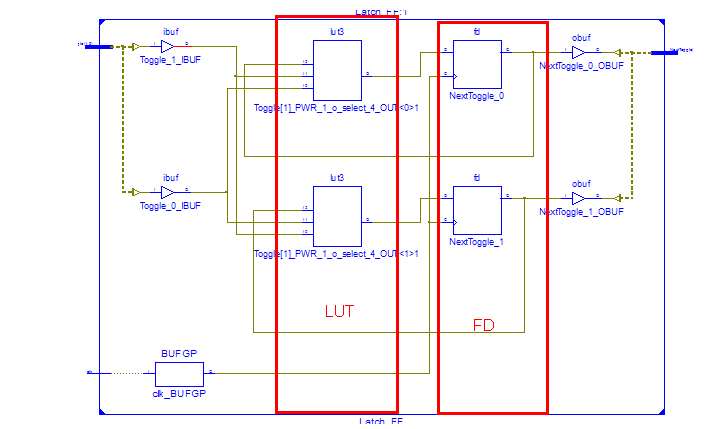

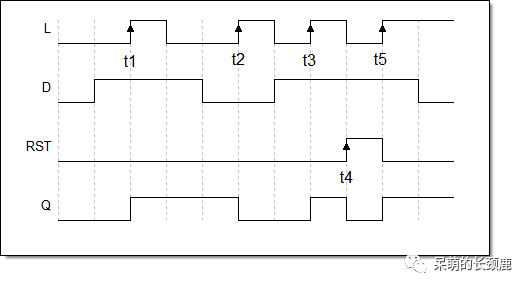

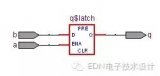

本案例主要通过两个基础的锁存器(Latch)和触发器(Flip-Flop)来阐述下两者之间的区别,从时序图和源代码可以了解。

2023-12-04 15:50:06 2757

2757

Chapter5 锁存器与触发器5.1 基本双稳态电路一、双稳态电路具有0 、1 两种逻辑状态, 一旦进入其中一种状态,就能长期保持不变的单元电路,称为双稳态存储电路,简称双稳态电路。1. 最基本

2021-07-30 06:43:29

触发器:能够存储一位二值信号的基本单元电路统称为“触发器”。锁存器:一位触发器只能传送或存储一位数据,而在实际工作中往往希望一次传送或存储多位数据。为此可把多个触发器的时钟输入端CP连接起来,用一个

2018-09-11 08:14:45

的数据和运算结果,它被广泛的用于各类数字系统和计算机中。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1

2011-10-09 16:19:46

锁存器的工作原理是什么?锁存器的动态特性及其应用有哪些?触发器的工作原理是什么?触发器的电路结构是如何构成的?

2021-11-03 06:48:50

锁存器和触发器1.什么情况要用到锁存器?状态不能保持?现在的单片机状态都是可以保持的吧2.看到很多产品用施密特触发器作为门极驱动器(栅极驱动器),是隔离的作用还是其他?这种触发器和专用的门极驱动器有哪些异同

2022-03-10 17:52:14

的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2019-04-23 03:35:28

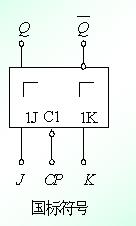

操作与具有相同“置位”和“复位”输入的先前SR触发器完全相同。这次的区别是,即使S和R都为逻辑“ 1” ,“ JK触发器”也没有SR锁存器的无效或禁止的输入状态。该JK触发器基本上是一个门控SR触发器

2021-02-01 09:15:31

在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把n个触发器

2018-10-27 22:38:21

2020.3.26_学习笔记两个D触发器 最近发现一个问题,代码中会特地的新建一个D触发器用来锁存信号,让很多人都比较疑惑,明明一个D触发器就可以检测输入是上升沿和下降沿。两个触发器的目的主要

2021-07-30 06:44:48

根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。触发器是一种能够保存1位二进制数的单元电路,是计算机中记忆装置的基本单元,由它可以组成

2019-12-25 17:09:20

未在延时链上传递时,锁存结果是确定的。但是信号在演示链上传播时,锁存结果却出现了不定态。有的时候写其他的程序时,用D触发器锁存组合逻辑的结果,在时序仿真中就会有不定态,这该怎么解决?

2021-09-26 20:41:21

逻辑可构成时序逻辑电路,简称时序电路。现在讨论实现存储功能的两种逻辑单元电路,即锁存器和触发器。双稳态:电子电路中。其双稳态电路的特点是:在没有外来触发信号的作用下,电路始终处于原来的稳定状态。在外

2016-05-21 06:50:08

封装中,其中一个这样的IC器件就是74LS373八角D型透明闩锁。74LS373的八个单独的数据锁存器或双稳态是“透明” D型触发器,这意味着当时钟(CLK)输入为逻辑电平“ 1”时为高电平(但也可以

2021-02-03 08:00:00

电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。 工程中的寄存器一般按计算机中字节

2018-07-03 11:50:27

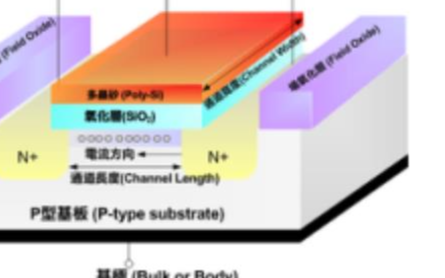

晶体管,门电路,锁存器,触发器的理解

2021-01-12 07:55:02

预放大锁存比较器是什么工作原理?运放锁存器的电路结构分析如何使用Spectre预放大锁存比较器进行仿真?

2021-04-08 06:56:02

基于PLD芯片的时序逻辑设计与实现:原理图输入设计直观、便捷、操作灵活;1-1、原理图设计方法简介QuartusII已包含了数字电路的基本逻辑元件库(各类逻辑门及触发器),宏

2009-10-29 22:03:10 0

0 1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 0

0 一、基本要求1、理解R-S触发器、J-K触发器和D触发器的逻辑功能;2、掌握触发器构成的时序电路的分析,并了解其设计方法;3、理解计数器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是

2006-04-16 17:31:53 1422

1422

CD4013 双D触发器 *CD4027 双JK触发器 *CD4042 四锁存D型触发器 *CD4043

2006-04-17 21:18:32 4131

4131 T触发器,什么是T触发器

在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的电路,即当T=0时

2009-09-30 18:26:07 30888

30888

锁存器,锁存器是什么意思

锁存器定义一位钟控D触发器只能传送或存储一位二进制数据,而在实际工作中往往是一次传送或存

2010-03-09 09:44:12 12791

12791 触发器的分类, 触发器的电路

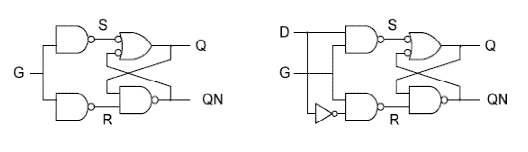

双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是触发器的原始形式。基本

2010-03-09 09:59:59 1866

1866 一种单锁存器CMOS三值D型边沿触发器设计

2017-01-17 19:54:24 25

25 触发器的功能:

① 完成比约束更复杂的数据约束:触发器可以实现比约束更为复杂的数据约束

② 检查所做的SQL是否允许:触发器可以检查SQL所做的操作是否被允许。例如:在产品库存表里,如果

2017-08-19 12:05:00 42622

42622 锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2017-11-02 09:24:41 95604

95604

本文主要介绍了电压比较器工作原理、电压比较器功能作用与施密特触发器作用。最后介绍了施密特触发器能否代替电压比较器以及它们之间的区别。

2018-01-16 11:59:07 22432

22432

锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。

2018-01-31 14:48:13 30802

30802

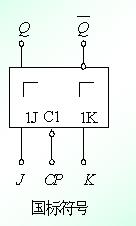

K触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2018-02-08 14:36:43 53841

53841

本文首先介绍了锁存器Latch结构和锁存器latch的优缺点,其次介绍了触发器Flip-flop的结构与优缺点,最后介绍了锁存器Latch和触发器Flip-flop两者之间的区别。

2018-04-18 14:10:10 133648

133648

在各种复杂的数字电路中不但需要对二值信号进行数值运算和逻辑运算,还经常需要将运算结果保存下来。为此,需要使用具有记忆功能的基本逻辑单元。能够存储1位二值信号的基本单元电路统称为触发器。

2018-07-20 08:00:00 0

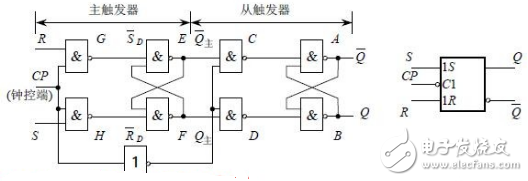

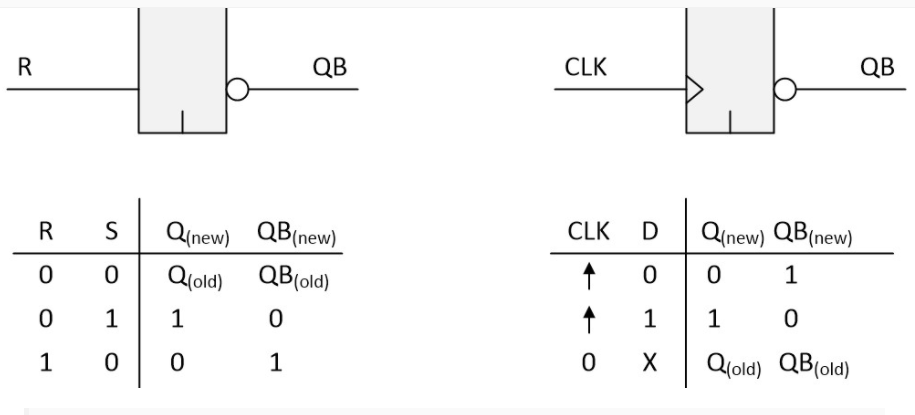

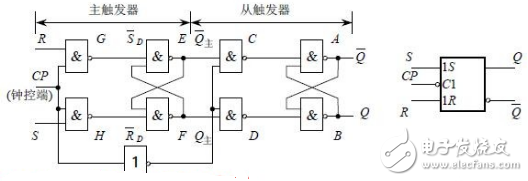

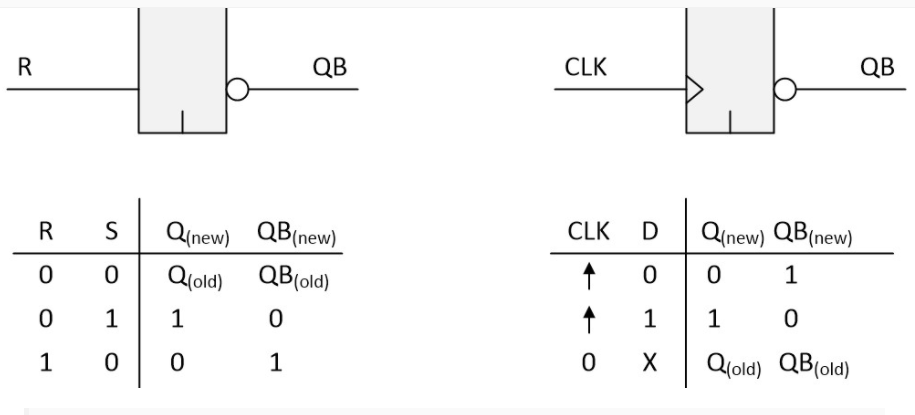

0 本文档的主要内容详细介绍的是数字电路教程之触发器课件的详细资料说明主要内容包括了:一 SR锁存器,二 电平触发的触发器,三 脉冲触发的触发器,四 边沿触发的触发器,五 触发器的逻辑功能及其描述方法

2018-12-28 08:00:00 17

17 触发器按逻辑功能分类有D触发器、JK触发器、T触发器和SR触发器。它们的功能可用特性表、特性方程和状态图来描述。触发器的电路结构与逻辑功能没有必然联系。例如JK触发器既有主从结构也有维持阻塞或利用传输延迟结构。每一种逻辑功能的触发器都可以通过增加门电路和适当的外部连线转换为其它功能的触发器。

2019-04-12 14:04:18 9585

9585

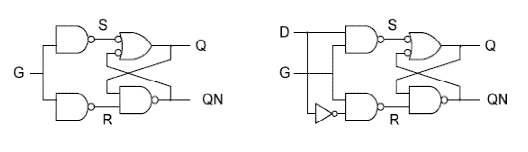

D型触发器是一个改进的置位复位触发器,增加了一个反相器,由此可见以防止S和R输入处于相同的逻辑电平,此状态将强制两个输出都处于逻辑“1”,超越反馈锁存动作,无论哪个输入先进入逻辑电平“1”都将失去控制,而另一个仍处于逻辑“0”的输入控制锁存器的结果状态。

2019-06-26 15:36:28 19351

19351

数字时序电路中通常用到的触发器有三种:电平触发器、脉冲触发器和边沿触发器。

2019-07-05 14:38:54 17268

17268

CP=1时,门。。打开,门。。被封锁,从触发器保持原来状态不变,D信号进入主触发器。但是要特别注意,这时主触发器只跟随而不锁存,即。。跟随D变化,D怎么变。。也随之怎么变。

2019-07-15 08:57:32 56238

56238

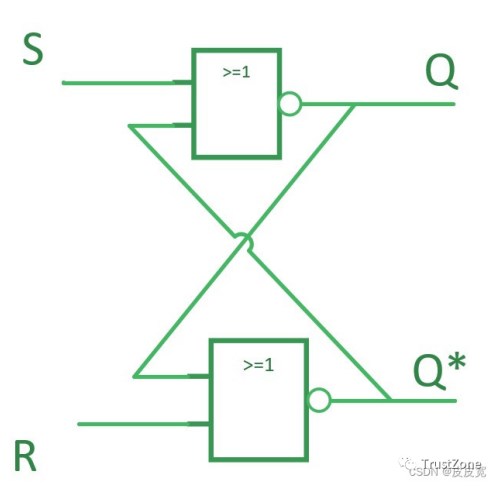

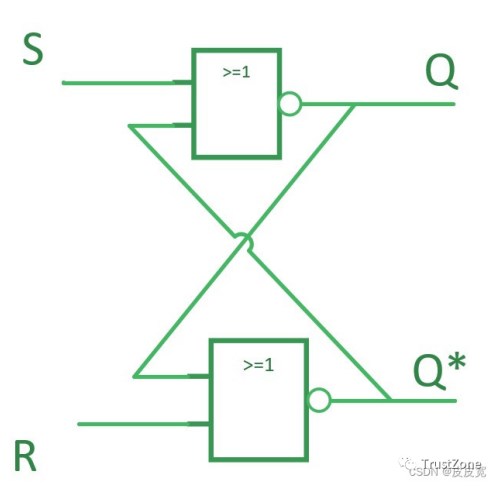

锁存器(有时也称为S/R锁存器)是最小的存储器块。它们可以使用两个NOR逻辑门(S和R为高电平有效)或两个NAND门(输入为低电平有效)构建,并用于构建更复杂的锁存器和触发器。

2019-07-30 11:23:28 7316

7316

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 96918

96918

,锁存器有两个输入,一个是有效信号EN,一个是输入数据信号DATA_IN,有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 2)触发器 触发器(Flip-Flop,简写为FF)也叫双稳态门,又称双稳态触发器,是一种可以在两种

2020-11-29 11:02:11 26376

26376 你有没有遇到过这样奇怪的事:你一直以为自己知道某件事,但当你试着向别人解释它时,你才发现自己的论述中存在漏洞和逻辑上的差异?这就是我最近所遇到的情况,当时有人问我锁存器和触发器之间的区别,以及

2021-01-05 16:03:53 5876

5876

首先应该明确锁存器和触发器也是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合电路的特性。 组合电路就是一个真值表,一个函数,一组输入对应

2021-08-12 10:26:12 5766

5766 这是一个系列文章,从最简单的门电路介绍,从基础的锁存器、触发器、编码器、译码器等一系列数字逻辑电路开始,最终构造一个简易版的CPU实物

2021-11-06 09:20:58 16

16 1:锁存器、触发器、寄存器的关联与区别 首先应该明确锁存器和触发器是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合逻辑电路的特性。 锁存

2022-12-19 12:25:01 14654

14654 主要内容: ·双稳态器件 ·锁存器常见结构 ·锁存器的应用 ·触发器 ·触发器的建立时间和保持时间 1、双稳态器件 ** 双稳态器件**是指稳定状态有两种,一种是0,一种是1的器件;双稳态器件

2023-01-28 09:28:00 6203

6203

你有没有遇到过这样奇怪的事:你一直以为自己知道某件事,但当你试着向别人解释它时,你才发现自己的论述中存在漏洞和逻辑上的差异?这就是我最近所遇到的情况,当时有人问我锁存器和触发器之间的区别,以及为什么它们都与寄存器有关。

2023-01-30 15:21:15 3771

3771 锁存器(latch):是电平触发的存储单元,数据存储的动作(状态转换)取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2023-01-31 14:57:40 2446

2446 锁存器(Latch)是数字逻辑电路中很重要的一种基本电路,常见的锁存器包括三个端口:数据输入口、数据输出口、使能端。当使能端为高电平时,输入口的数据直接送到输出口,此时输入输出口可以看成是直接

2023-02-09 21:05:05 3073

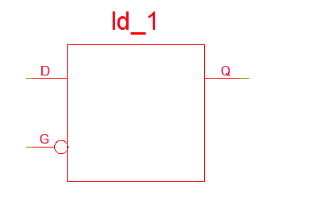

3073 锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

2023-03-23 14:48:54 4270

4270

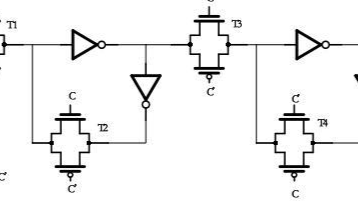

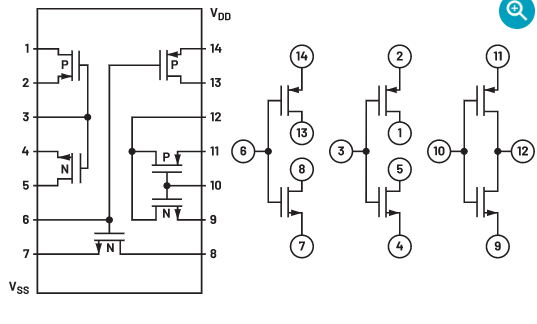

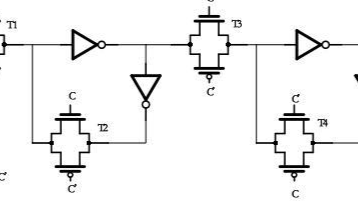

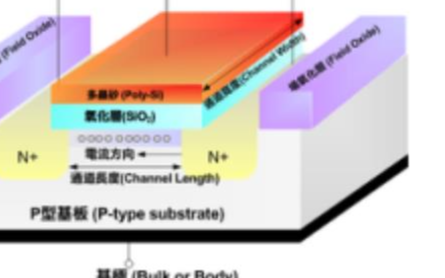

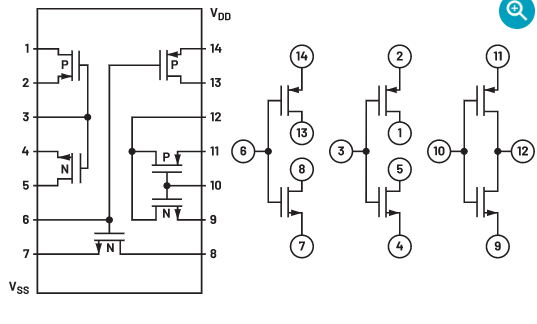

本实验活动的目标是进一步强化上一个实验活动 “ADALM2000实验:使用CD4007阵列构建CMOS逻辑功能” 中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而言,您将了解如何使用CMOS传输门和CMOS反相器来构建D型触发器或锁存器。

2023-05-29 14:16:27 2594

2594

简单的说触发器实现边沿出发是通过两级锁存器实现的,比如上升沿触发其实是,前一级是低电平锁存,后一级是高电平锁存。

2023-06-28 11:18:32 3213

3213

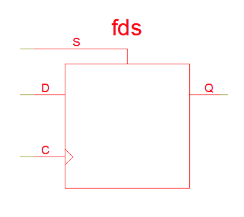

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 51321

51321

RS触发器是一种常见的数字逻辑门电路元件,它由两个相互反馈的逻辑门组成。RS触发器的逻辑功能可以描述为存储器元件或双稳态开关。

2023-08-07 16:17:32 18971

18971 请简述锁存器与触发器的概念,并分析二者的区别。

2023-08-15 09:24:10 7536

7536

在传统的异步 RS 触发器中,当输入的 R 和 S 同时为 1 时,会引发互锁问题,输出结果是不确定的。为了避免这个问题,常常使用带有使能控制的同步触发器,如带有时钟信号的 D 触发器或 JK 触发器。这些触发器在时钟边沿上才会响应输入信号,解决了异步 RS 触发器的互锁问题。

2023-08-28 15:44:35 6262

6262 RS触发器是由两个交叉连通的反相器(NOT门)和两个逻辑门组成的,通常是由两个与门(AND门)和一个非门(NOT门)构成。而双稳态触发器(也称为D触发器)是由一对互补输出的锁存器构成,通常是由两个与非门(NAND门)和一个非门(NOT门)构成。

2023-09-26 16:11:50 2683

2683 在数字电路中,RS触发器(也称为RS锁存器)是一种基本的双稳态触发器,它可以通过特定的输入信号来实现置位(Set)和复位(Reset)操作。

2023-09-28 16:31:07 11269

11269 D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 6026

6026

RS触发器是数字电路中最简单的一种触发器,其由两个互相反向的电平触发器组成。RS触发器的逻辑功能非常重要,它可以用于存储1位二进制数据,并能够实现各种逻辑运算和数字记忆功能。下面将详细介绍RS触发器

2023-11-17 16:01:56 7552

7552 触发器和锁存器是数字逻辑电路中两种重要的元件,它们在不同的应用场景中发挥着关键作用。虽然触发器和锁存器在一些方面有相似之处,但它们在功能和应用方面也存在一些明显的区别。下面将详细介绍触发器和锁存器

2023-12-25 14:50:46 2755

2755 逻辑表达式是描述逻辑关系的符号表示,可以用于定义和描述各种电路和逻辑操作。在逻辑电路中,RS触发器是一种基本的存储器元件,也被称为锁存器。 RS触发器是由两个与门组成的,其输出互相连接,形成一个反馈

2024-01-12 14:09:48 4550

4550 数字IC设计里,常会出现锁存器,D触发器和寄存器,很多人(比如我)老傻傻分不清,搞不懂他们的区别是什么。

2024-02-17 15:04:00 3911

3911

RS触发器与SR触发器都是基本的数字逻辑电路元件,常用于存储、控制和时序电路中。

2024-01-29 14:15:08 8676

8676 D触发器是一种常见的数字逻辑电路,它在数字系统和计算机中扮演着重要的角色。本文将详细探讨D触发器的逻辑功能、工作原理以及RD(Reset-D)触发器和SD(Set-D)触发器的作用。 首先,我们先来

2024-02-06 13:52:14 52523

52523 的触发器,其输入信号作用于触发器,触发器将根据输入信号进行状态切换。本文将详细介绍如何使用JK触发器构成T触发器,并介绍T触发器的逻辑功能。 一、JK触发器的逻辑功能 JK触发器具有四种基本的逻辑功能,分别是保持、复位、设置和反转。 保持:

2024-02-06 14:11:11 12517

12517 在数字电路和计算机系统中,锁存器、触发器和寄存器都是关键的存储元件,它们在功能、结构和使用场景上存在一定的差异。本文将对这三者进行详细的介绍和比较,以便更好地理解它们之间的区别。

2024-05-23 15:28:16 4329

4329 在数字电路设计中,触发器和时序逻辑电路是构建复杂数字系统不可或缺的基础元素。触发器(Flip-Flop)作为基本的存储单元,能够存储一位二进制信息,并在特定的时钟信号控制下更新其状态。而时序逻辑

2024-07-18 17:43:41 4403

4403 在数字电子学中,锁存器(Latch)和触发器(Flip-Flop)是两种基本的存储元件,它们在数字系统中扮演着至关重要的角色。它们的主要功能是存储和保持数据状态,以供后续处理。然而,它们在实现方式

2024-07-23 10:16:31 1093

1093 锁存器(Latch)是一种存储电路,用于存储一位二进制信息。锁存器在数字电路设计中非常常见,它可以用来保持数据状态、实现同步等功能。锁存器的工作原理和触发方式是数字电路设计的基础之一。 1. 锁存器

2024-07-23 10:17:50 1387

1387 在数字电路中,锁存器和触发器是两种非常重要的存储元件,它们在逻辑功能上有着明显的区别。锁存器和触发器都是用于存储二进制信息的基本元件,但它们在结构、工作原理、应用场景等方面都存在差异。 一、锁存器

2024-07-23 10:19:20 1891

1891 锁存器(Latch)是一种存储单元,用于存储一位二进制信息。在数字电路中,锁存器是一种基本的存储元件,广泛应用于寄存器、计数器、触发器等电路中。锁存器的原态和新态是描述锁存器状态变化的两个重要概念

2024-07-23 10:21:06 1532

1532 锁存器和触发器是数字电路中的基本组件,它们在实现数字逻辑功能中起着至关重要的作用。虽然它们在功能上有很多相似之处,但它们之间还是存在一些主要区别的。本文将探讨锁存器和触发器的主要区别。 1. 定义

2024-07-23 10:24:34 3030

3030 锁存器(Latch)是一种在数字电路中广泛使用的存储元件,它能够存储一位二进制信息。锁存器电路的触发方式有很多种,包括同步触发、边沿触发、电平触发等。 一、锁存器的基本概念 锁存器是一种具有记忆功能

2024-07-23 11:31:06 1262

1262 、锁存器的组成 锁存器主要由以下几部分组成: 输入端 :接收外部信号,用于控制锁存器的状态。 存储单元 :用于存储数字信号的状态,通常由触发器(Flip-Flop)构成。 输出端 :输出锁存器存储的状态,可以是高电平、低电平或不确定状态

2024-07-23 11:32:56 5355

5355 边沿触发器(Edge-triggered flip-flop)是一种数字电路元件,它在数字逻辑设计中扮演着重要的角色。边沿触发器在接收到输入信号的上升沿或下降沿时,会改变其输出状态。 1. 边沿

2024-08-11 09:09:36 1662

1662 主从触发器,也被称为主从同步触发器或主从锁存器触发器,是一种在数字电路设计中广泛使用的触发器类型。它主要用于防止亚稳态现象,提高电路的稳定性和可靠性。 主从触发器的工作原理 主从触发器由两个触发器

2024-08-11 09:18:04 1732

1732 在数字电路设计中,触发器是一种非常重要的基本逻辑元件,用于存储一位二进制信息。触发器的种类繁多,但主要分为两大类:主从触发器(Master-Slave Flip-Flop)和边沿触发器

2024-08-11 09:35:02 4850

4850 主从触发器(又称为脉冲触发器)和边沿触发器在波形上的比较主要体现在它们的触发方式和输出响应上。以下是对两者波形比较的具体分析: 一、触发方式 主从触发器 : 主从触发器由主触发器和从触发器组成,它们

2024-08-11 09:47:39 2951

2951 边沿触发器是数字电路中的一种重要元件,其触发方式基于时钟脉冲(CP)的特定跳变(上升沿或下降沿)来接收和处理输入数据。这种触发器在数字逻辑设计中扮演着关键角色,因其独特的触发机制和优越的性能特点而被广泛应用于各种数字系统中。

2024-08-12 14:26:06 4205

4205 在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的有JK触发器、D触发器和T触发器等。 一、触发器的基本概念 1.1 触发器的定义 触发器

2024-08-22 10:33:51 3765

3765 引言 数字电路是现代电子技术的基础,广泛应用于计算机、通信、控制等领域。触发器是数字电路中的一种基本逻辑元件,具有存储和传递信息的功能。 触发器的基本概念 触发器是一种具有记忆功能的数字电路元件

2024-08-22 10:37:33 5059

5059 可以分为多种类型,如SR触发器、JK触发器、D触发器等。其中,JK触发器因其具有两个稳态的特性,被广泛应用于数字电路设计中。 JK触发器的基本概念 2.1 触发器的定义 触发器是一种具有记忆功能的数字逻辑电路,可以存储一位二进制信息。

2024-08-22 10:39:18 2766

2766 锁存器(latch)是数字电路中的一种基本存储单元,用于存储和保持一个或多个位的状态。锁存器在数字逻辑设计中扮演着重要的角色,它们可以用于实现各种功能,如数据存储、信号同步、状态保持等。 锁存器

2024-08-28 09:09:00 2433

2433 SR锁存器和RS触发器在数字电路领域都扮演着重要的角色,但它们在操作方式、功能特性以及应用场景上存在着显著的差异。 一、定义与基本结构 SR锁存器 (Set-Reset Latch)是一种

2024-08-28 09:31:53 3454

3454 D触发器和D锁存器是数字电路中常用的两种存储元件,它们在功能和应用上有一定的区别。 定义和功能 D触发器(Data Flip-Flop)是一种具有两个稳定状态的双稳态电路,它可以存储一位二进制信息

2024-08-28 09:34:17 3723

3723 将JK触发器变成T触发器,主要涉及到对JK触发器的输入端口进行适当的连接和配置,以实现T触发器的逻辑功能。以下是将JK触发器转换为T触发器的具体步骤: 步骤一:理解JK触发器和T触发器的逻辑功能

2024-08-28 09:41:19 6044

6044 锁存器与触发器的状态图并不完全相同 ,这主要是由于它们的工作原理和触发机制存在差异。 锁存器 锁存器(Latch)是电平触发的存储单元,其数据存储的动作取决于输入时钟(或使能)信号的电平值。当锁存器

2024-08-28 10:20:14 992

992 门控RS锁存器和触发器是数字电路中常见的两种存储元件,它们在功能和结构上存在一些区别。 定义和功能 门控RS锁存器(Gated RS Latch)是一种具有两个稳定状态的存储元件,可以实现对输入信号

2024-08-28 10:22:22 1728

1728 在Verilog HDL中实现锁存器(Latch)通常涉及对硬件描述语言的基本理解,特别是关于信号如何根据控制信号的变化而保持或更新其值。锁存器与触发器(Flip-Flop)的主要区别在于,锁存器

2024-08-30 10:45:03 2394

2394

电子发烧友App

电子发烧友App

评论