锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

应用场合:数据有效迟后于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器。

触发器(flip-flop)---对脉冲边沿敏感,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变。当时钟信号C上升沿时刻(或者下降沿时刻),输入D被赋值到输出Q,其他情况保持锁存。触发器是边沿触发的存储器。

应用场合:时钟有效迟后于数据有效。这意味着数据信号先建立,时钟信号后建立。在CP上升沿时刻打入到寄存器。

比较:

1)、latch和flip-flop都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关;

2)、latch由电平触发,异步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。触发器由时钟沿触发,同步控制。所以说,触发器是一个同步版锁存器;

3)、FPGA主要有触发器和查找表组成,没有标准的latch单元,一个latch需要更多资源才能实现;

4)、一般的设计规则是:在绝大多数设计中避免产生latch。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch;

5)、if语句或者case语句不全很容易产生latch。在RTL描述中,如果一个信号在一个条件的分支中被赋值,而不是在所有分支中被赋值,则该信号的前一个值就要被保留。

同步情况下(敏感列表时时钟边沿)用触发器实现,保留到下一个时钟边沿为止,异步情况下(即敏感列表中是电平而非时钟的边沿)需要由锁存器来实现,保留到下一个已列出的分支情况的电平有效为止。

2、锁存器的有与无

推导出锁存器的一般规则是:

1)、如果在电平触发的always语句所有可能的执行过程(如if/case语句)中变量没有全部被赋值,就会产生锁存器;

2)、如果在边沿触发的always语句所有的可执行过程中变量没有被全部复制,会产生触发器;

3)、如果在always语句中变量在if/case的所有分支中都被赋值则综合成组合逻辑;

always @ (Toggle)

case (Toggle) //synthesis full_case

2'b01: NextToggle = 2'b10;

2'b10: NextToggle = 2'b01;

endcase

always @ (Toggle)

case (Toggle)

2'b01: NextToggle = 2'b10;

2'b10: NextToggle = 2'b01;

endcase

第一种写法用编译命令synthesis full_case把case语句补全,效果和default语句或将case列举出所有情况类似。

此时没有锁存器,只用两个2输入的LUT完成2输入2输出的逻辑功能,纯粹的组合逻辑。

第二种写法没有将case的所有情况列举出,就产生了锁存器LD。

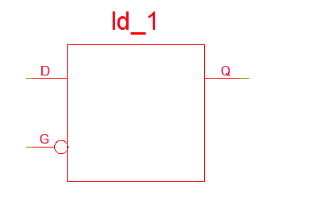

查看Xilinx的库手册,LD是透明锁存器,当G使能的时候,Q输出D的值;当G不使能的时候,Q保持上一状态的值。

以下改用的时钟的上调沿触发,生成了两个D触发器,当时钟上调沿来临时用输入端D更新输出端Q的数据。

always @ (posedge clk)

case (Toggle)

2'b01: NextToggle = 2'b10;

2'b10: NextToggle = 2'b01;

endcase

这说明边沿触发的always块中,即使if...else或者case没写全也不会出现锁存器。

-

存储器

+关注

关注

39文章

7714浏览量

170839 -

电平

+关注

关注

5文章

370浏览量

41247 -

锁存器

+关注

关注

8文章

952浏览量

43837 -

触发器

+关注

关注

14文章

2050浏览量

63039

发布评论请先 登录

数字逻辑设计中锁存器和触发器的定义和比较

锁存器和触发器的定义和比较

锁存器和触发器的定义和比较

评论