内容简介

本案例主要通过两个基础的锁存器(Latch)和触发器(Flip-Flop)来阐述下两者之间的区别,从时序图和源代码可以了解。

锁存器

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。简单而言,锁存器的输入有数据信号和使能信号,当处于使能状态时,输出随着输入变化而变化,当不处于使能状态时,输入信号怎么变化都不会影响输出。

触发器

触发器是对脉冲边沿敏感的器件,它的变化只会在时钟的上升沿或者下降沿到来的瞬间改变。

通过简单的锁存器时序和触发器时序来感受下有什么区别吧

1

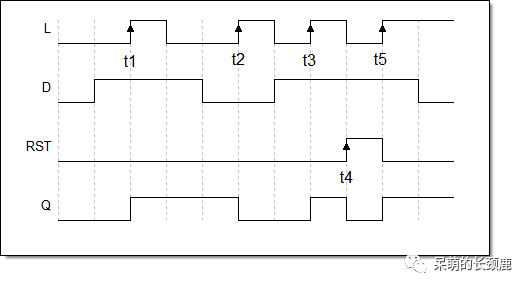

锁存器时序图

**锁存器LTCH—— **输入:L , D ,RST 输出:Q

LTCH信号解读

只有L为高电平,输出Q才会跟随输入D并进行锁存,t1到t3之间,输入D信号虽然发生变化,输出Q并未随之改变,锁存上一次D的信号;当复位RST为高电平,Q输出低电平,由于RST在t4为高电平后下降沿变为低电平,而在t5时L为高电平对输出Q产生作用,输出Q变为高电平。

2

触发器时序图

**触发器FF_RSE—— **输入:CR , SR ,RST 输出:Q

FF_RSE信号解读

SR上升沿时,置位输出Q;CR上升沿时,复位输出Q;当复位RST为高电平,输出Q为低电平,由于RST在t4为高电平,虽然SR在t5后为高电平但对输出Q不产生作用,RST变为低电平后,SR已不是上升沿,仍旧对输出Q不产生作用。

源代码

锁存器LTCH代码:

FUNCTION_BLOCK "LTCH"

TITLE = 'LTCH'

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

D : Bool;

L : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q : Bool;

END_VAR

BEGIN

IF #RST THEN

#Q := FALSE;

ELSIF #L THEN

#Q := #D;

END_IF;

END_FUNCTION_BLOCK

触发器FF_RSE源代码:

FUNCTION_BLOCK "FF_RSE"

TITLE = 'FF_RSE'

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

CS : Bool;

CR : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q : Bool;

END_VAR

VAR

es : Bool;

er : Bool;

END_VAR

BEGIN

IF #RST THEN

#Q := FALSE;

ELSIF #CR AND NOT #er THEN

#Q := FALSE;

ELSIF #CS AND NOT #es THEN

#Q := TRUE;

END_IF;

#es := #CS;

#er := #CR;

END_FUNCTION_BLOCK

-

数据存储

+关注

关注

5文章

1014浏览量

52528 -

锁存器

+关注

关注

8文章

952浏览量

43826 -

触发器

+关注

关注

14文章

2050浏览量

63033 -

RST

+关注

关注

0文章

31浏览量

7771

发布评论请先 登录

触发器与锁存器的区别在哪?

触发器与锁存器的区别在哪?

评论