首先应该明确锁存器和触发器也是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合电路的特性。

组合电路就是一个真值表,一个函数,一组输入对应一组输出,当前什么输入就根据函数得到什么输出,实时跟踪变化,这样也就容易有冒险、竞争之类的问题产生毛刺。

锁存器:电平敏感

always @ (enable)

??if (enable) ?q 《= d;

那就是说,在enable有效的时间内,q完全跟踪d的值,比如在这个时间内d变化了,q跟着变化,当enable失效的时候,q存储d最后的值。

触发器:我们把输出只在时钟某个时刻变化的玩意儿叫触发器。边沿敏感

always @ (posedge enable)

??if (enable) q 《= d;

这个便是一个d触发器。只在enable(一般大家都叫它clock)的上升沿q采样d,而且在每个时钟的上升沿都会采样。

在fpga中一般避免用latch,因为在FPGA中触发器资源丰富,不用白不用,latch由于是电平触发的,相对触发器来说容 易产生毛刺,电路不稳定.

latch的优点是完成同一个功能所需要的门较触发器要少,所以在asic中用的较多

那最后再说寄存器,寄存器这个玩意儿是一个概念层次的东西,1个寄存器就是能存1bit数据的东西。既可以用触发器实现也可以用锁存器实现。以触发器为例,由于触发器每个时钟上升沿都会采样,所以触发器会有一个反馈逻辑,当load有效的时候才会采样d,否则保持不变。

always @ (posedge clk or negedge rst_n)

if (!rst_n)

q 《= 0;

else if (load)

q 《= d;

这便就是一个寄存器了。

1. 寄存器

在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

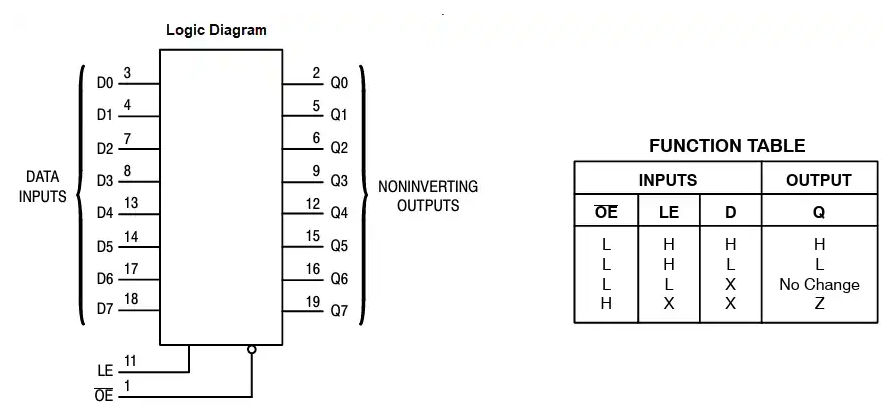

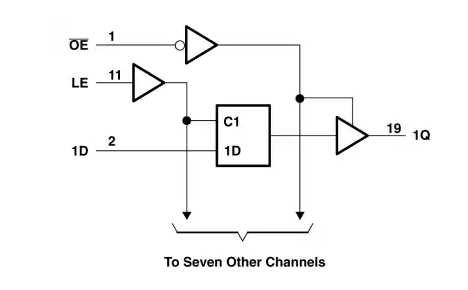

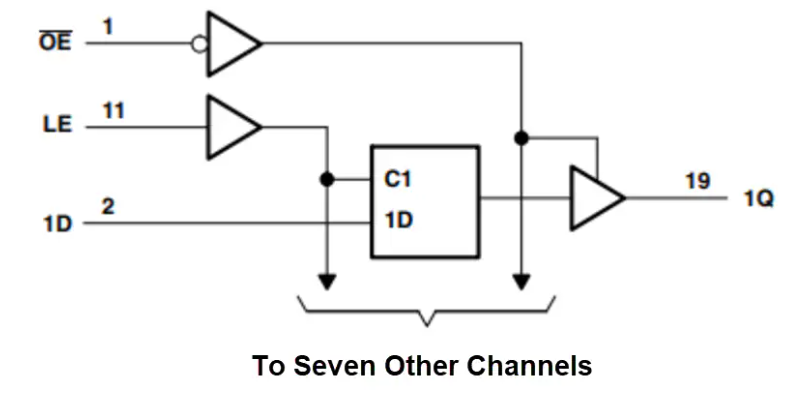

2 .锁存器

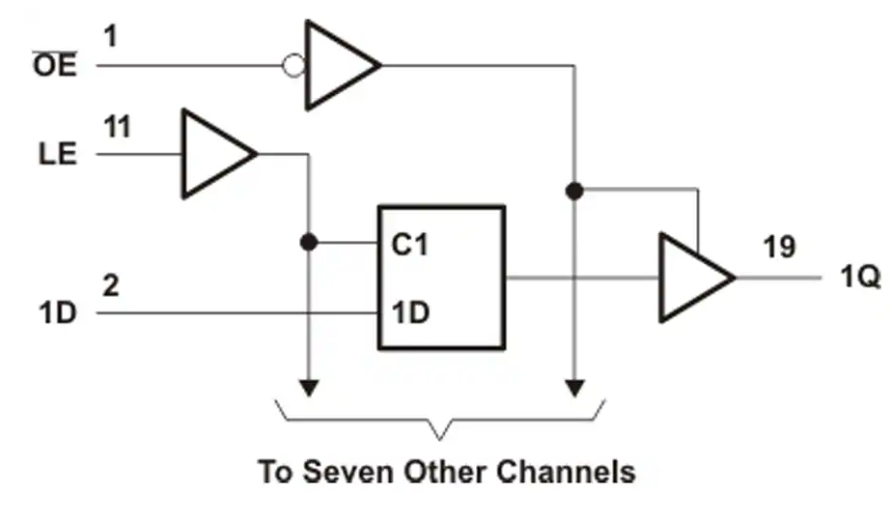

由若干个钟控D触发器构成的一次能存储多位二进制代码的时序逻辑电路。数据有效迟后于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器。

3. 锁存器与寄存器的区别:

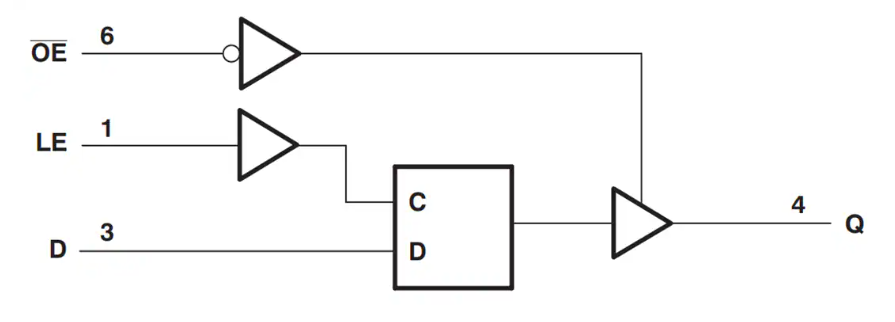

(1)寄存器是同步时钟控制,而锁存器是电位信号控制。锁存器一般由电平信号控制,属于电平敏感型。寄存器一般由时钟信号信号控制,属于边沿敏感型。

(2)寄存器的输出端平时不随输入端的变化而变化,只有在时钟有效时才将输入端的数据送输出端(打入寄存器),而锁存器的输出端平时总随输入端变化而变化,只有当锁存器信号到达时,才将输出端的状态锁存起来,使其不再随输入端的变化而变化

可见,寄存器和锁存器具有不同的应用场合,取决于控制方式以及控制信号 和数据之间的时间关系:若数据有效一定滞后于控制信号有效,则只能使用锁存器;数据提前于控制信号而到达并且要求同步操作,则可用寄存器来存放数据。

编辑:jq

-

寄存器

+关注

关注

31文章

5588浏览量

129046 -

锁存器

+关注

关注

8文章

952浏览量

43833 -

触发器

+关注

关注

14文章

2050浏览量

63037

原文标题:锁存器与寄存器的区别

文章出处:【微信号:hoperun300339,微信公众号:润和软件】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

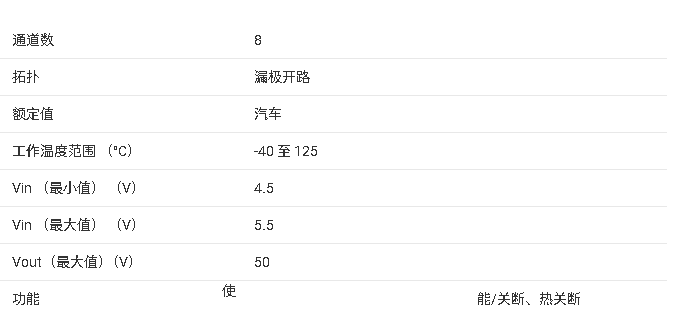

MC74VHCT373A高速CMOS八路D型锁存器技术解析

SN74AC573 Octal D型透明锁存器技术解析与应用指南

Texas Instruments SN74LVC1G373单D型锁存器数据手册

Texas Instruments SN74LV8T573-EP八路透明D型锁存器数据手册

一文读懂Allegro先进磁性开关和锁存器

使用寄存器点亮LED灯

第四章 什么是寄存器

纳祥科技74HC595D,一款应用于LED广告显示屏的低功耗3态8位移位寄存器

锁存器与寄存器有哪些区别

锁存器与寄存器有哪些区别

评论