扫描二维码获取

更多精彩

FPGA设计论坛

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站):

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂):

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

更多资料下载欢迎注册http://www.fpgaw.com

扫码加微信回复加群

邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:关于FPGA中锁存器的生成:if语句和case语句的完整性影响

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22494浏览量

638991

原文标题:关于FPGA中锁存器的生成:if语句和case语句的完整性影响

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

IDT信号完整性产品:解决高速信号传输难题

IDT信号完整性产品:解决高速信号传输难题 在当今的电子设备中,随着计算、存储和通信应用中信号速度的不断提高,系统设计师面临着越来越大的信号完整性挑战。高速信号在传输过程中,由于发射

SI合集002|信号完整性测量应用简介,快速掌握关键点

一、信号完整性定义信号完整性(SignalIntegrity,简称SI)是衡量信号从驱动端经传输线抵达接收端后,波形完整程度的关键指标,反映了信号在电路中能否以正确的时序、持续时间和电

Cadence工具如何解决芯粒设计中的信号完整性挑战

在芯粒设计中,维持良好的信号完整性是最关键的考量因素之一。随着芯片制造商不断突破性能与微型化的极限,确保组件间信号的纯净性与可靠性面临着前所未有的巨大挑战。对于需要应对信号

人工智能行业如何使用for循环语句进行循环

: 支持range()函数生成数字序列 可结合else语句使用 Java中的for循环: 传统结构:for(初始化; 条件; 增量) 增强for循环:for(类型 变量 : 集合) 主要用于数组和集合

基础篇3:掌握Python中的条件语句与循环

在Python编程语言中,条件语句和循环是构成复杂逻辑和数据处理的基石。本篇基础教程将帮助您深入了解Python中的条件语句和循环结构,让您能够更好地控制程序流程。

条件语句

条件

发表于 07-03 16:13

了解信号完整性的基本原理

,设计人员必须注意电路板布局并使用适当的导线和连接器,从而最大限度地减少反射、噪声和串扰。此外,还必须了解传输线、阻抗、回波损耗和共振等基本原理。 本文将介绍讨论信号完整性时使用的一些术语,以及设计人员需要考虑的问题,然后介绍 [Amphenol] 优异的电缆和

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

。与会者提出了关于信号完整性和电源完整性设计的问题,这些问题反映了一些新兴的工程挑战。Scott、Rich和Istvan在回答中强调了严格分析、细节工具表征以及深入理解基本原理的重要

发表于 05-14 14:52

•1242次阅读

电源完整性基础知识

先说一下,信号完整性为什么写电源完整性?SI 只是针对高速信号的部分,这样的理解没有问题。如果提高认知,将SI 以大类来看,SI&PI&EMI 三者

发表于 05-13 14:41

信号完整性测试基础知识

在当今快速发展的数字时代,高速传输已成为电子设备的基本要求。随着数据传输速率的不断提升,信号完整性(Signal Integrity,简称SI)问题变得越来越重要。信号完整性是高速互连系统设计的基石

电源完整性分析及其应用

引言

电源完整性这一概念是以信号完整性为基础的,两者的出现都源自电路开关速度的提高。当高速信号的翻转时间和系统的时钟周期可以相比时,具有分布参数的信号传输线、电源和地就和低速系统中的情况完全不同了

发表于 04-23 15:39

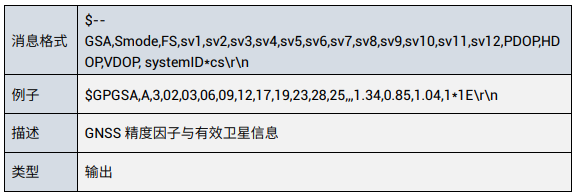

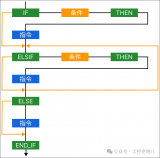

关于FPGA中锁存器的生成:if语句和case语句的完整性影响

关于FPGA中锁存器的生成:if语句和case语句的完整性影响

评论