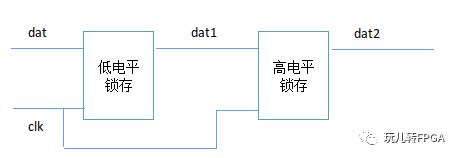

简单的说触发器实现边沿出发是通过两级锁存器实现的,比如上升沿触发其实是,前一级是低电平锁存,后一级是高电平锁存。

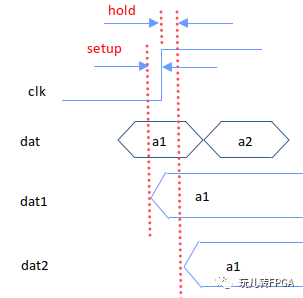

参考上图,clk为0时,dat1 <= dat;clk为1时,dat1不变,也就是被锁存了,同时dat2 <= dat1。下图反映了整个过程。

参考上图,低电平锁存的时间叫做setup时间,高电平锁存的时间是hold时间,如果是下降沿触发则是倒过来。总之,前一级的锁存就是setup时间,作用是让数据从输入锁存到中间级,后一级是hold时间,作用是你让数据从中间级输出。setup和hold过程都需要时间,所以如果其中任何一个不满足时序那都会输出出错,这也是为什么要检查时序的原因之一。

触发器的原理讲了,但是锁存器是如何实现的呢?

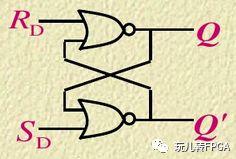

下图是RS锁存器的电路结构和真值表,其中SR同时为1的状态是不允许出现的。Q是当前状态,Q*是下一个状态,也就是次态。

从真值表可以看出,SR状态其中有一个为1且,互反的时候Q 是可以直接操作的Q =S;两个都为0的时候Q*=Q,也就是保持。

如果用RS实现对输入数据锁存怎么操作呢?

1.输入数据D=1,则令S=1,R=0,这时Q* = 1

2.令S=0,R=0,则D无论为多少,Q*依然不会改变

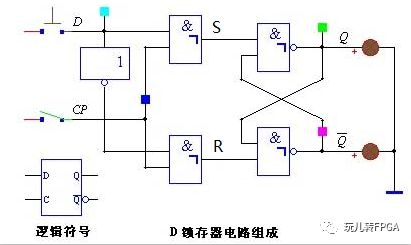

以上2步也就帮你实现了电平锁存,具体电路如下,被称为D锁存器的电路:

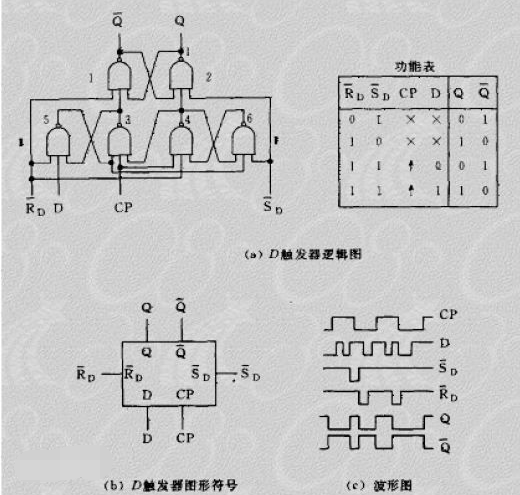

CP就是输入时钟,D也就是输入数据,与非门保证R和S不会同时为1。当CP = 1 时,输出端的状态随输入端的状态而改变。S = D,所以Q* = D ,存入新的数据;当CP = 0 时,无论 D 如何变化,输出端的状态保持不变。Q * = Q n,存入的数据不变。为了触发器可靠的工作,要求 D 输入信号先于CP = 1 的信号,称为建立时间 t set。

此电路为高电平锁存,在CP前面加个反相器就成了低电平锁存器,两个级联就可以实现边沿触发功能。

-

反相器

+关注

关注

6文章

329浏览量

44946 -

锁存器

+关注

关注

8文章

952浏览量

43835 -

触发器

+关注

关注

14文章

2050浏览量

63037 -

状态机

+关注

关注

2文章

497浏览量

28844 -

CLK

+关注

关注

0文章

132浏览量

17932

发布评论请先 登录

CMOS触发器在CP边沿的工作特性研究

什么是边沿触发器_边沿D触发器介绍

常用边沿触发器电路结构和工作原理

脉冲和边沿触发器区别

触发器实现边沿出发是如何实现的?

触发器实现边沿出发是如何实现的?

评论