在同步电路设计中,边沿检测是必不可少的!

2012-03-01 09:59:04 5376

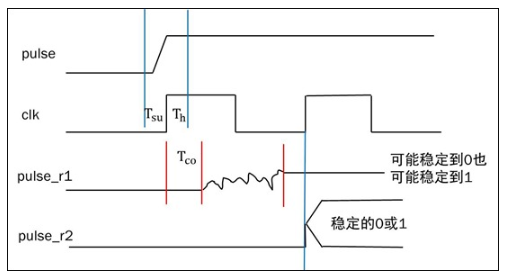

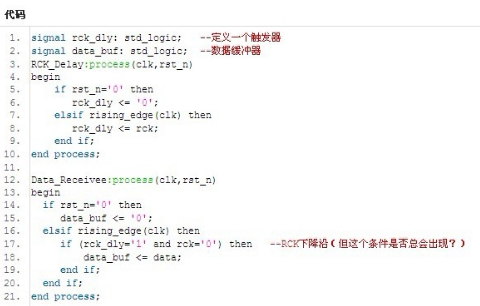

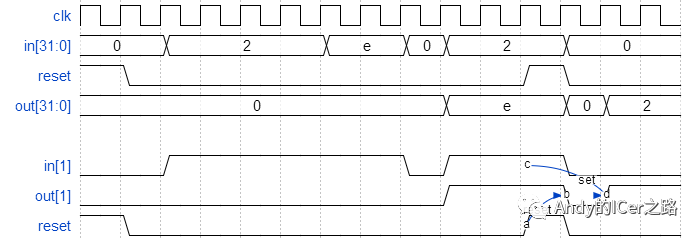

5376 在同步电路设计中,边沿检测是必不可少的!后一种方法所耗的资源要比前一种方法多(一个触发器),但是就可以大大提高可靠性,这绝对是物有所值!!

2012-02-01 10:53:05 1066

1066

在同步电路设计中,边沿检测是必不可少的!

2017-08-16 15:19:32 2166

2166

如何检测过流信号,并在电路中实现逻辑控制。

2019-05-24 07:29:00 6212

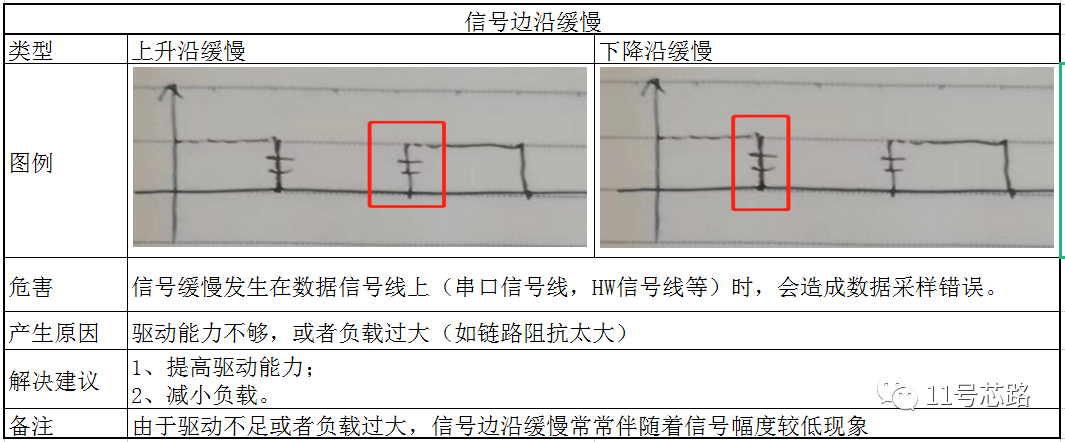

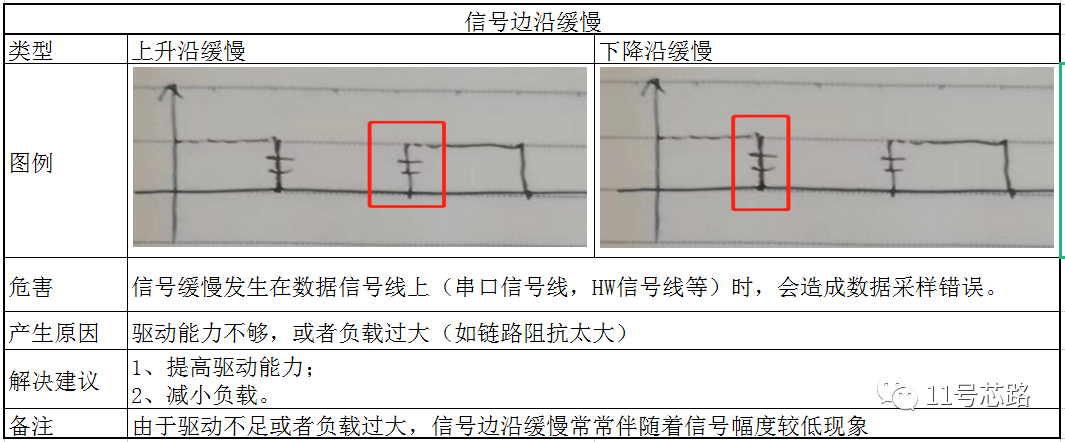

6212 随着市场更高的需求,现在的设计者不得不考虑提高时钟频率,缩短信号的上升边沿。

2023-10-02 16:35:00 1781

1781

异步电路原理是什么?有哪些优劣势?通过英特尔的Loihi芯片实现异步电路?

2021-06-21 07:17:56

边沿检测设计报告

2017-09-26 15:38:19

FPGA_100天之旅_边沿检测

2017-09-28 13:37:44

Labview的TCP控件为同步超时模式实现的,在一对多场景明显不够用,效率低,看了官方例程也没有异步TCP的说明,该如何实现异步TCP呢?

2022-04-25 17:08:00

常见的串行通信接口有哪些呢?STM32串口异步通信的过程该怎样去完成呢?

2021-12-08 06:36:24

STM32定时器怎样通过ETR模式进行边沿检测并计数呢?如何去实现?

2021-11-24 06:51:27

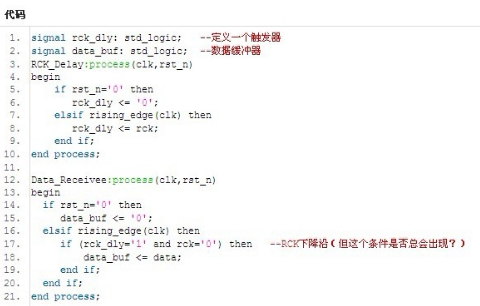

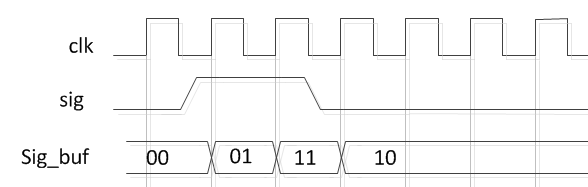

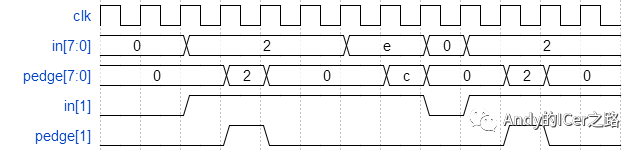

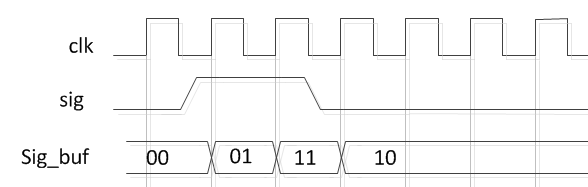

`fpga应用篇(二):边沿检测上一篇介绍了阻塞赋值与非阻塞赋值,这次我们利用非阻塞赋值产生一个简单的应用即边沿检测,边沿检测一般用来产生使能信号。程序如下:综合后电路:clk为主时钟分频之后得到

2017-04-06 21:28:08

verilog怎么将一个边沿触发信号的上升沿作为控制变量呢?

2023-05-10 10:38:09

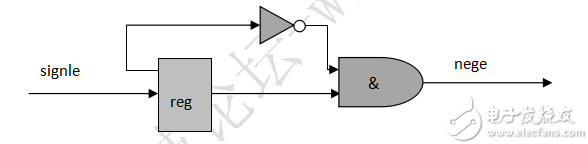

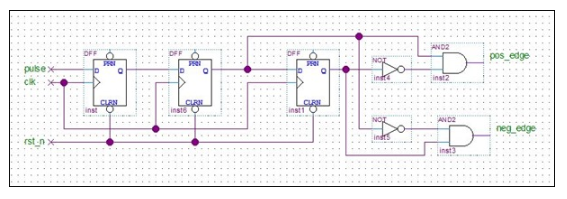

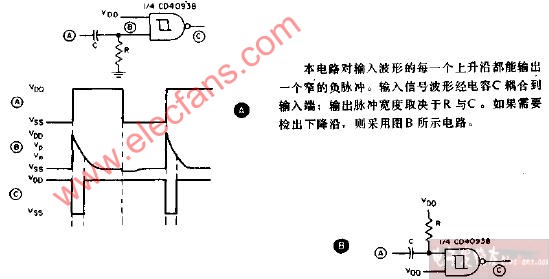

低到高的跳变。本节,梦翼师兄和大家一起学习一个经典的边沿检测电路,通过该电路,我们可以在信号出现跳变沿的时候产生尖峰脉冲,从而驱动其他电路模块进行相应的动作。电路原理分析我们来分析一下这个电路结构

2019-12-04 10:24:31

什么是同步逻辑和异步逻辑,同步电路和异步电路的区别是什么?

2021-06-18 08:52:44

入图,有没有大神分析一下,是怎实现边沿检测的,它各个时期的电平状态是什么

2016-04-13 14:36:25

程序边沿检测下降沿并统计数量(数量到达2后重新计数,并发送动作信号),但是最终发现检测结果不准确,有时候能检测到,有时候检测不到。万分感谢您的解答和建议!下面是verilog代码[code]//边沿检测initial numinitial led

2021-08-21 12:58:00

设计一个脉搏检测前置放大电路,主要是信号调理电路这一块,目前用了AD620作为一级放大电路,还有一个运放LM324的有源低通滤波电路环节,二级放大电路该怎么设计呢,或者说我目前这个电路还存在什么问题

2016-05-16 19:24:58

的差别,而不会有什么波形上的不同。但是检测结果却显示的很不正常,如下图所示,上面是原始信号,下面是检测到的信号,电阻是线性元件,不可能有滤波的功能啊,但是波形却为什么变成了这样呢?反复检查了电路,并无异常。另,检测电路接地要接mcu上的GND还是接电源上的地呢?二者有什么区别吗?跪求解释。

2019-01-16 08:24:53

在FPGA上实现时钟信号的多路同步输出该怎么做呢?好像要用到FPGA内部的PLL,将时钟信号分成多路输送到其他板块,求高手解答该怎么做输入时钟由一个50M的晶振提供

2023-03-21 14:51:29

的寄存器的输出端都是由同一个时钟端驱动出来的,所有的寄存器在同一个步调上进行更新。同步电路中的信号,我们称之为同步信号。如果在设计中,寄存器的时钟端连接在不同的时钟上,那么称之为异步电路设计。 在异步电路中

2023-02-28 16:38:14

我看到网上关于边沿检测的讲解,有个地方不理解,t0时刻和t1时刻分别是怎样的时刻,trigger在时钟上升沿经过触发器输出的信号和经过非门的信号是什么样的关系?我的理解是trigger分别输出后是两个电平相反的信号,为什么相与之后就可以检测是否为上升沿或者下降沿?谢谢。

2023-05-10 14:52:22

如何准确测量CAN节点的信号边沿参数?

2021-05-08 06:27:36

驱动实现GPIO的脉冲信号检测原理是什么?如何利用驱动去实现GPIO的脉冲信号检测呢?

2022-03-04 08:48:48

新手求问:最近在做一个测试系统,我用了DAQ助手采集电压信号来测量压力又用了边沿计数功能来测量转角(通过转角能求得体积参数),这里出现了一个问题:边沿计数功能测试只能采样(按要求),得不到采样率,该

2015-06-02 21:18:23

请教大神:同时能检测有源信号(如24V脉冲信号)和无源脉冲信号,接收端为5V单片机IO,我知道有源信号用光耦隔离后再接收,无源信号可以直接接收,但是怎样能用一个电路实现两种信号都可以接收呢?就是不管有源无源都可以接收。

2022-05-11 16:18:27

示波器输入负载而言还是对于该信号源输出阻抗而言?2.怎么实现高低阻抗不匹配的检测呢,我看部分信号源可以设置输出50欧和高阻态,那么如果后级示波器输入阻抗不匹配怎么检测呢?需要设计什么硬件电路检测电流

2024-05-23 11:45:07

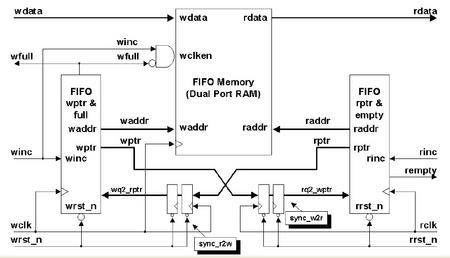

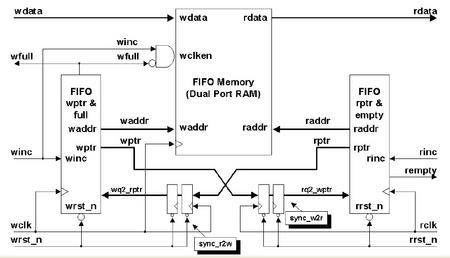

本文讨论了在ASIC设计中数据在不同时钟之间传递数据所产生的亚稳态问题,并提出了一种新的异步FIFO的设计方法,并用VHDL语言进行描述,利用Altera公司的Cyclone系列的EP1C6进行硬件实现,该电路软件仿真和硬件实现已经通过验证,并应用到各种电路中。

2021-04-29 06:54:00

打开开关的时候,功耗就上来了,无法进入低功耗模式,如何让我们的蓝牙模块监测到高低电平之后,进入低功耗模式?群里问了下,说需要让该io口支持双边沿触发,即,上升沿和下降沿同时触发检测,请问,方向是否是正确的?其二,如果正确,如果设置双边沿触发?

2019-11-07 15:55:30

的数据进行计数;停止位不参与,起始位加上数据位共9bit。该计数器的计数周期为9。本工程使用了检测信号下降沿的方法,信号下降沿的检测方法:检查uart_rx的下降沿,就要用到FPGA里的边沿检测技术

2019-11-29 10:08:59

本人想做黑白块的边沿检测,但是为了达到检测的高精度,普通光电对管与光电传感器的区别在哪里?因为原理相同,也不知道到底性能差别在哪里?有没有大神可以一起讨论一下?

2015-05-31 09:47:10

本文提出了一种简易通用异步串行信号检测装置的设计方法。介绍了AVR 系列单片机Atmega128 和USB2.0 接口芯片的功能特性,并实现异步串行信号检测装置。阐述了通过USB2.0 接口控制单

2009-09-12 16:26:22 23

23 本文主要研究了用FPGA 芯片内部的EBRSRAM 来实现异步FIFO 设计方案,重点阐述了异步FIFO 的标志信号——空/满状态的设计思路,并且用VHDL 语言实现,最后进行了仿真验证。

2010-01-13 17:11:58 40

40 摘要:提出了1种基于CPLD、EPLD或FPGA等可编程逻辑器件的异步串行通信接口电路的设计方法。该方法简单快捷。易于实现。而且可以作为异步串行通信接口的标准模块插入到用户的各

2010-04-30 09:58:41 46

46

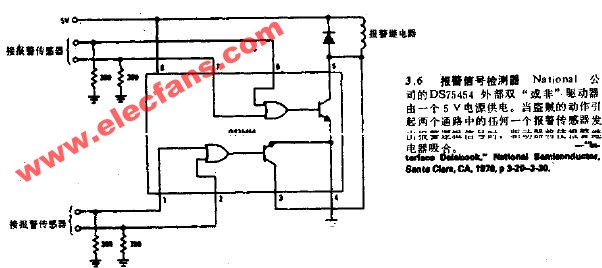

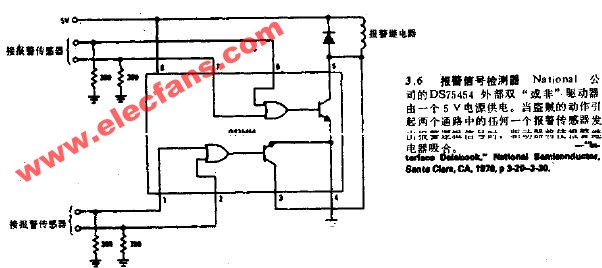

报警信号检测器电路

2009-01-11 22:36:18 822

822

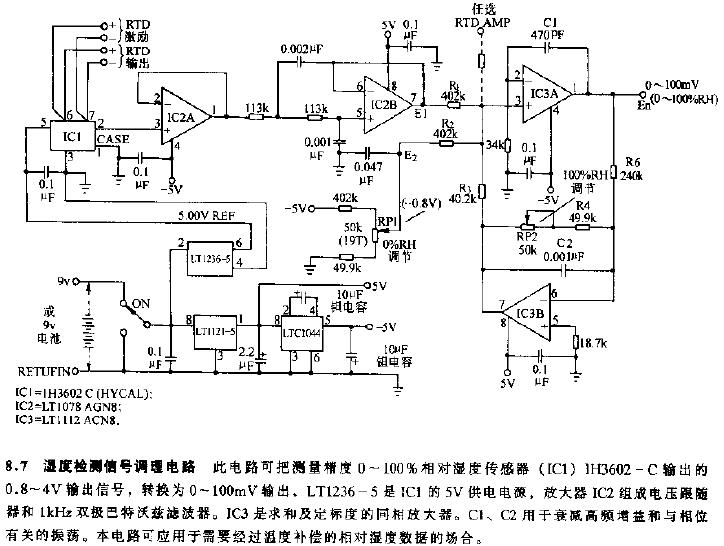

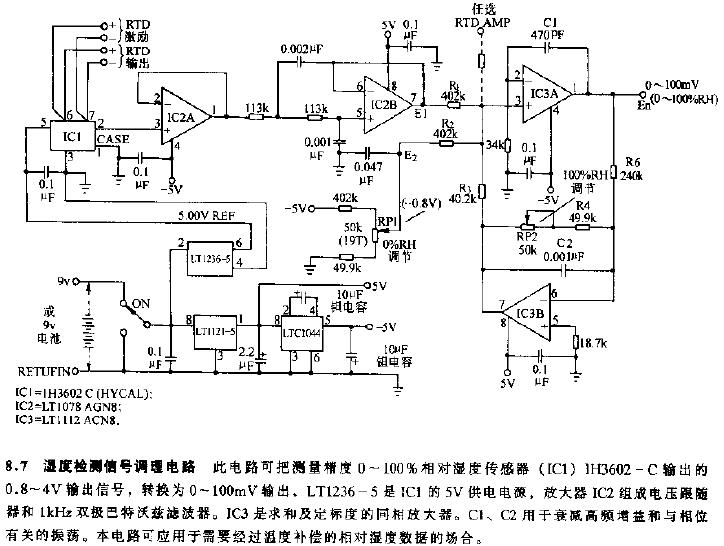

温度检测信号调理电路

2009-02-15 13:35:03 1576

1576

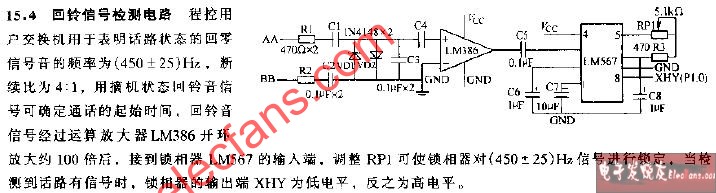

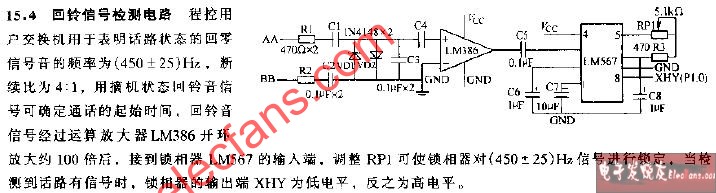

回铃信号检测电路

2009-02-28 11:45:54 839

839

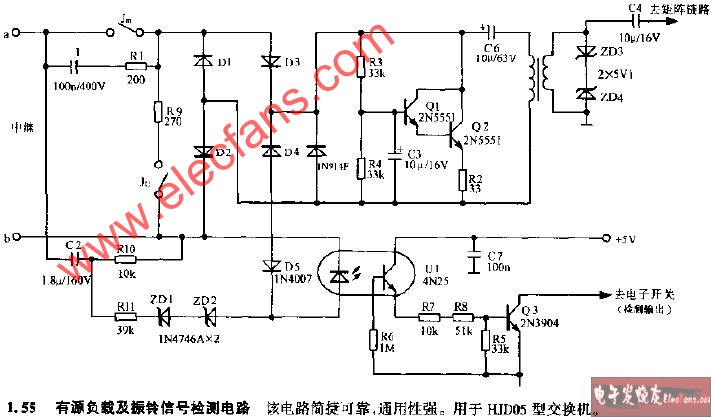

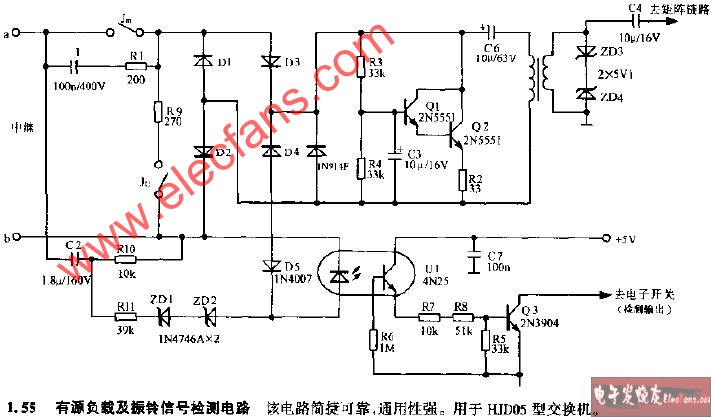

有源负载及振铃信号检测电路

2009-03-04 21:25:02 1360

1360

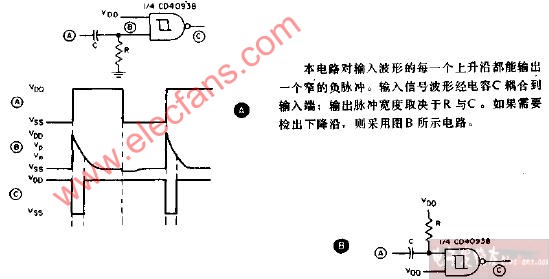

脉冲边沿检出器电路图

2009-03-28 09:20:16 767

767

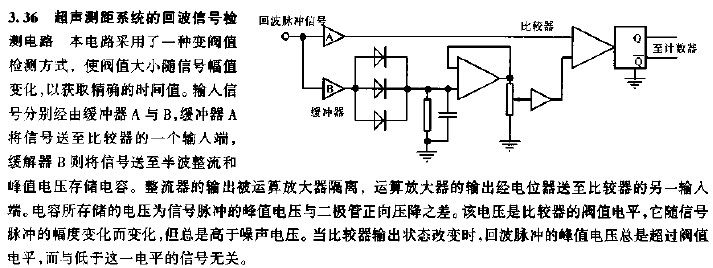

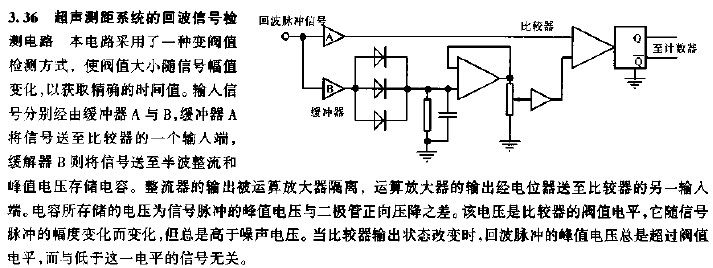

超声测距系统的回波信号检测电路

2009-04-22 19:33:13 1031

1031

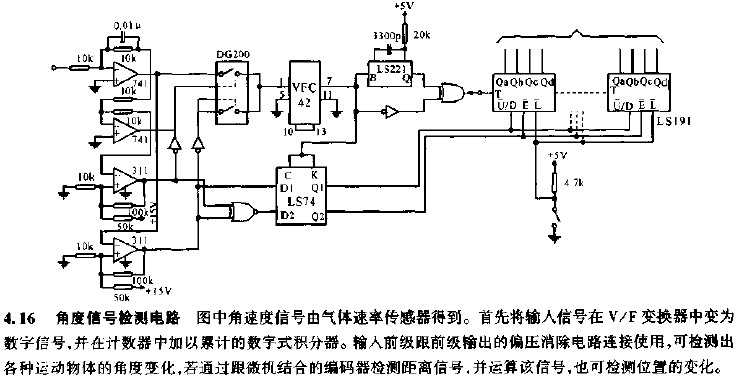

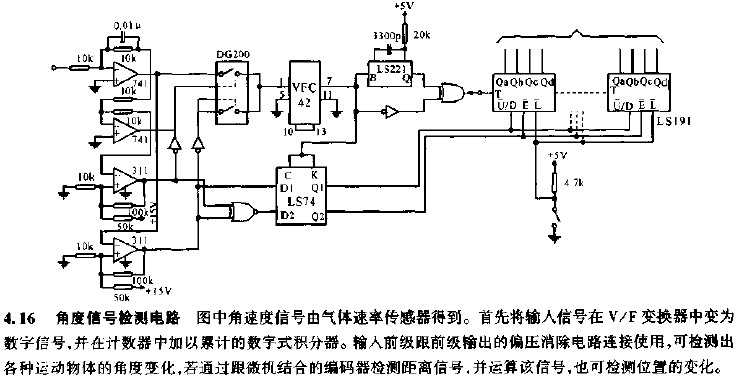

角度信号检测电路

2009-04-24 21:50:05 837

837

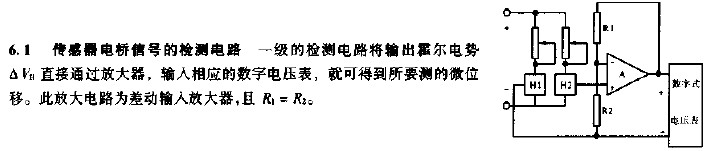

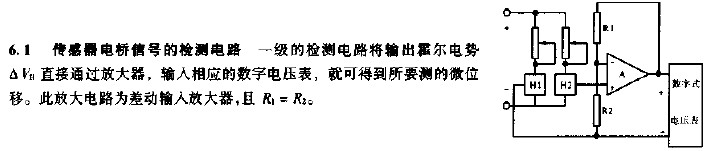

传感器电桥信号的检测电路

2009-04-26 15:58:38 996

996

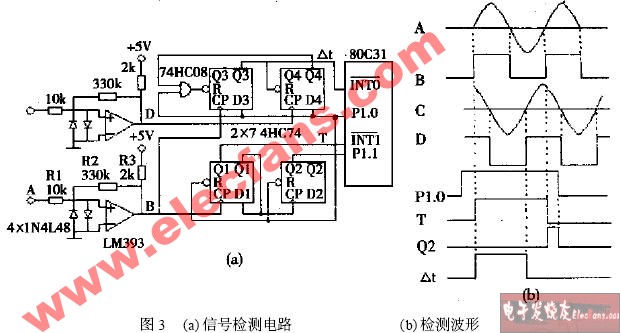

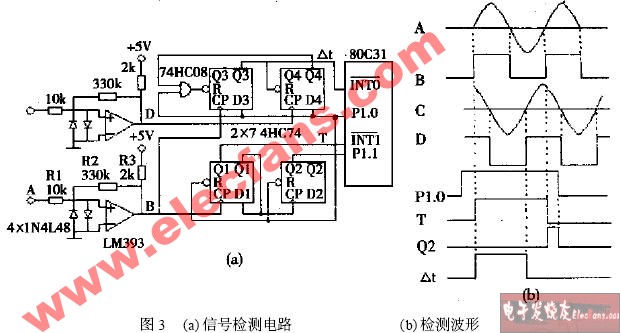

信号检测电路如图3 (a) ,波形如图3 (b) 所示:

2009-06-06 17:58:26 2182

2182

边沿检测与提取程序

2018-01-29 14:56:31 0

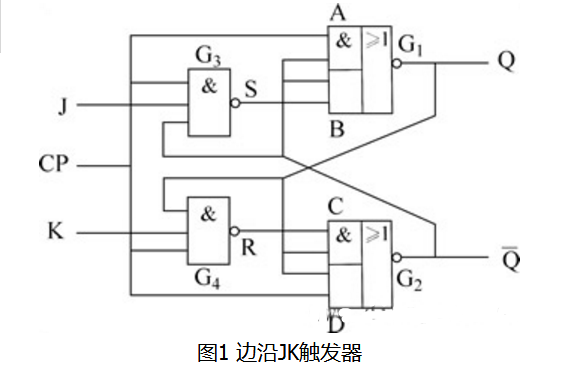

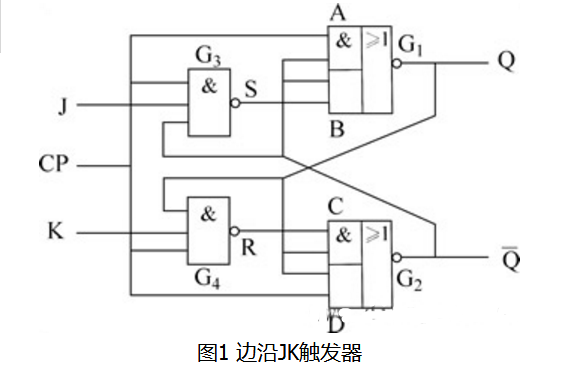

0 边沿触发器只在时钟脉冲CP上升沿或下降沿时刻接收输入信号,电路状态才发生翻转,从而提高了触发器工作的可靠性和抗干扰能力,它没有空翻现象。边沿触发器主要有维持阻塞D触发器、边沿JK触发器、CMOS边沿触发器等。

2018-01-31 09:17:11 33188

33188

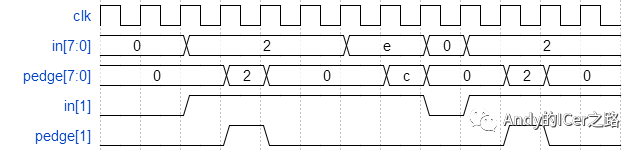

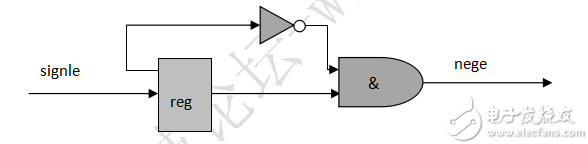

本文记录一下关于用移位寄存器实现边沿检测的技巧。要学会硬件思维式的“模块式”读写代码,那么请多看别人的代码,并用ISE或者VIVADO综合出来看看。 边沿检测 边沿检测,顾名思义,就是检查信号的边沿

2018-04-15 10:26:01 3667

3667 方便我们学习,边沿检测。 这个电路的意思就是,输入一个信号后我们经过一个寄存器,然 后把这个寄存器的输出,和下次输出的值取反后相与,那么我们就可 以这么想,如果一个高平的值经过这个寄存器后延迟一个上升沿后输 出也为高

2018-06-13 11:20:07 6134

6134

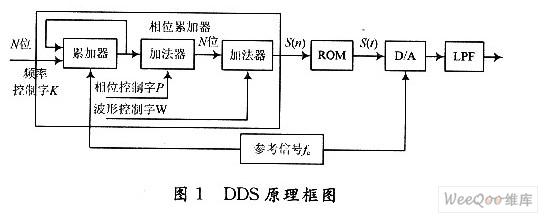

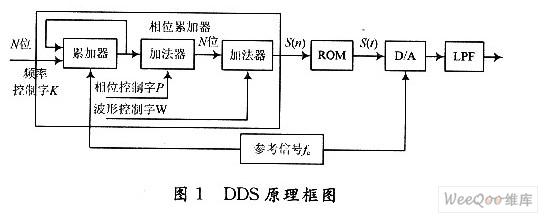

某型导弹测试设备电路板检测仪主要完成该测试设备的电路板的故障检测。该检测系统要求激励信号产生电路体积小,配置灵活,且精度高、转换速度快。基于FPGA的DDS信号发生器较传统信号发生器能够更好地满足检测仪要求。

2019-01-10 09:15:00 5327

5327

一般而言,处理跨时钟域的方法有这么几种(大家在网上也都能找到资料,这些资料大都来自几篇经典的论文,中文方面的资料大都是翻译过着理解这几篇论文而来):少量的数据用边沿检测电路,或者脉冲检测电路,或者电平检测电路,或者两级触发器;比较多的数据时用异步FIFO。

2018-09-10 10:06:00 13063

13063

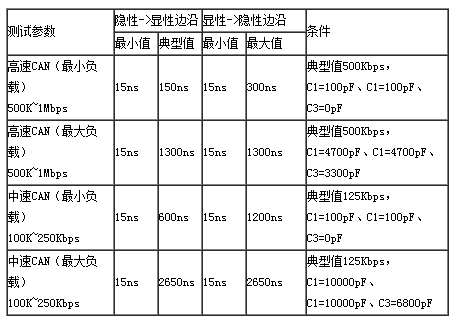

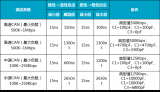

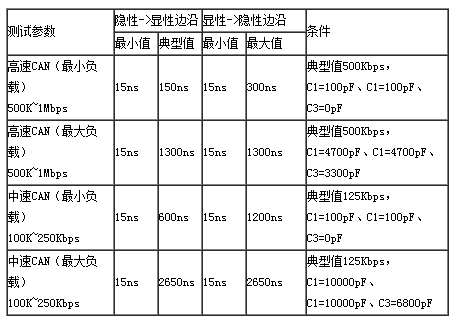

边沿时间分为上升沿时间、下降沿时间。下降沿时间是按照电压(20%~80%电压区间,有些按照10%~90%电压区间测量边沿时间,文中以20%~80%电压区间测量边沿时间)。表中给出时间范围,如果超出

2018-09-22 08:51:00 21393

21393

首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边沿(上升沿或下降沿)进行

2018-12-06 11:53:10 64392

64392

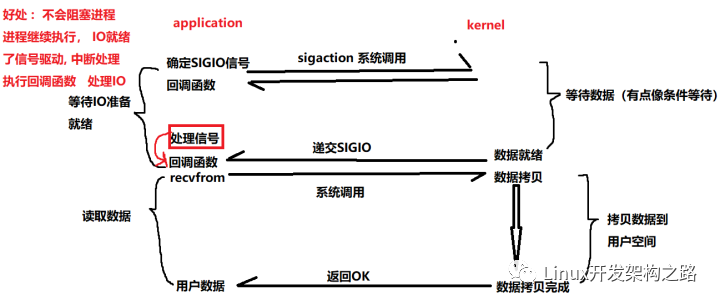

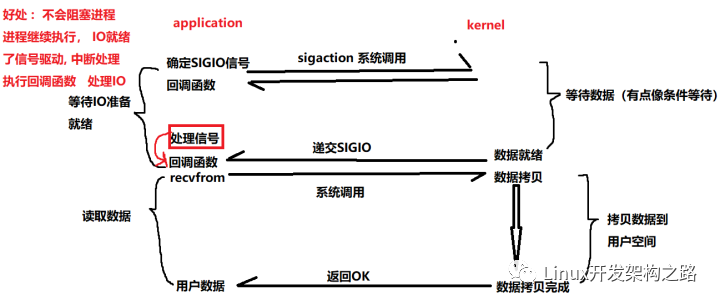

程序的二进制代码在内存中都有着确定的执行流程,为什么收到异步信号以后,程序会被“中断”,然后跳转到这个handle函数里面去运行呢?内核怎么有能力让程序做这样的跳转呢,总不可能临时修改程序的可执行代码吧?

2019-04-15 14:58:11 1337

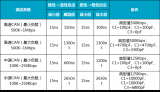

1337 CAN总线设计规范对于CAN节点的信号边沿各项参数都有着严格的规定,如果不符合规范,则在现场组网后容易出现不正常的工作状态,各节点间出现通信故障。具体要求如表 1所示,为测试标准“GMW3122信号边沿标准”。

2019-05-17 15:18:10 1616

1616

边沿检测电路(edge detection circuit)是个常用的基本电路。所谓边沿检测就是对前一个clock状态和目前clock状态的比较,如果是由0变为1,能够检测到上升沿,则称为上升沿检测

2019-11-19 07:09:00 11728

11728 异步电路 1. 电路的核心逻辑是组合电路,比如异步的FIFO/RAM读写信号、地址译码信号等电路; 2. 电路的输出不依赖于某一个时钟,也就说不是由时钟信号驱动触发器产生的; 3. 异步电路非常容易

2020-12-05 11:53:41 12647

12647 )都可以分解成4个状态:①高电平 ②低电平 ③上升沿 ④下降沿。 图1:开关信号 在PLC编程里,上升沿指令和下降沿指令可以直接调用;那么对于单片机的C语言编程,又如何实现边沿信号的判断呢?因为早期做过PLC编程的缘故,受PLC编程思路的影响

2021-05-03 10:14:00 5180

5180

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34:56 3146

3146 面这个电路我觉得肯定是第一时间想到的,直接对输入信号分压,单片机检测高低电平就好了,另外防止过冲或者地漂移加上钳位设计;

2022-08-02 17:42:09 9175

9175

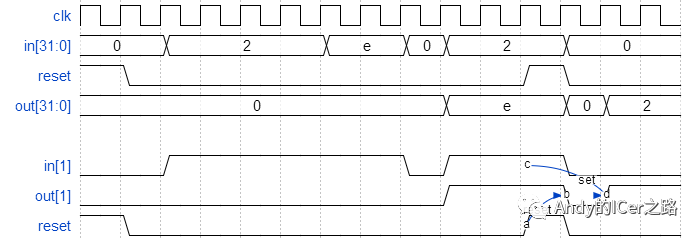

所谓边沿检测,就是检测输入信号即上升沿或者下降沿的检测。 边沿检测的电路很好实现:上一时刻为低电平,而当前时刻为高电平,此时就为上升沿;上一时刻为高电平,而当前时刻为低电平,此时就为上升沿。 通过

2022-11-26 10:20:09 2681

2681 , 那么究竟速率多高才能称为高速电路呢,平时我们应该如何区分高速和低速呢? 大家可能会认为信号周期频率 FCLOCK 高的才属于高速设计 其实我们在设计时考虑的最高频率往往取决于信号的有效频率( 亦称转折频率 ) Fknee 如上图信

2023-03-26 02:30:05 1973

1973 边沿检测指令有扫描操作数的信号下降沿指令和扫描操作数的信号上升沿指令。

2023-04-10 09:38:27 2587

2587 边沿检测指令有扫描操作数的信号下降沿指令和扫描操作数的信号上升沿指令。

2023-04-12 09:23:26 10916

10916 本文将从Verilog和边沿检测的基本概念入手,介绍Verilog边沿检测的原理和应用代码示例。

2023-05-12 17:05:56 5473

5473

对于8位向量中的每个位,检测输入信号何时从一个时钟周期的0变为下一个时钟周期的1(类似于上升沿检测)。应在从0到1的跳变发生后的周期内设置输出位。

2023-06-05 16:24:02 1395

1395

在设计双边沿采样电路(Dual-edge triggered flip-flop)之前,先从单边沿采样电路设计(Edge capture register)开始。

2023-06-05 16:27:30 2355

2355

1、什么是边沿检测 边沿检测用于检测信号的上升沿或下降沿,通常用于使能信号的捕捉等场景。 2、采用1级触发器的边沿检测电路设计(以下降沿为例) 2.1、设计方法 设计波形图如下所示: 各信号说明如下

2023-06-17 14:26:40 3847

3847

简单的说触发器实现边沿出发是通过两级锁存器实现的,比如上升沿触发其实是,前一级是低电平锁存,后一级是高电平锁存。

2023-06-28 11:18:32 3213

3213

边沿检测大致分为:上升沿检测,下降沿检测和,双沿检测。原理都是通过比输入信号快很多的时钟去采集信号,当出现两个连续的采集值不等的时候就是边沿产生处。

2023-06-28 15:19:12 4359

4359

。如果该指令检测到 RLO 从“0”变为“1”,则说明出现了一个信号上升沿。 每次执行指令时,都会查询信号上升沿。检测到信号上升沿时,该指令输出 Q 将立即返回程序代码长度的信号状态“1”。在其它任何情况下,该输出返回的信号状态均为“0”。 说明 修改边沿

2023-06-28 16:20:11 1491

1491

同步电路与异步电路有何区别 同步电路和异步电路是数字电路中两种类型的电路,两种电路在功能、结构、时序要求等方面都存在差异。同步电路和异步电路分别适用于不同类型的应用场景,因此在设计数字电路时要根据

2023-08-27 16:57:02 12401

12401 对于多位的异步信号如何进行同步呢? 异步信号(Asynchronous Signals)是指系统中发生的事件或者信号,它们的发生时间不可预测、不可控制,与其他的进程、线程以及系统中的各种资源之间

2023-09-12 11:18:09 2192

2192 高频信号为什么容易衰减?为什么高频信号不能直接通过电阻的分压来实现信号的衰减呢? 随着科技的不断发展,生活中越来越少有人不了解“高频信号”的概念。高频信号是指频率比较高、波长比较短的电磁波信号,往往

2023-10-20 15:02:24 4220

4220 反电势过零检测电路如何选择电阻呢? 反电势过零检测电路主要是用于控制电器开关的电路,实现准确的开关控制。在该电路中,电阻的选择是非常重要的,直接关系到检测电路的可靠性和稳定性。下面就来详细阐述反电势

2023-10-26 18:19:08 1511

1511 一. 谈信号驱动IO (对比异步IO来看) 信号驱动IO 对比 异步 IO进行理解 信号驱动IO: 内核将数据准备好的时候, 使用SIGIO信号通知应用程序进行IO操作 通知应用程序处理IO

2023-11-08 15:32:41 1915

1915

什么是同步逻辑和异步逻辑?同步电路与异步电路有何区别? 同步逻辑和异步逻辑是计算机科学中的两种不同的逻辑设计方法。它们分别用于描述数字电路中信号的传输和处理方式。同步逻辑是指电路中的各个组件在一个

2023-11-17 14:16:03 3516

3516 部分是独立运行的,没有明确定义的时钟信号来同步它们的操作。相反,每个部分在满足特定的条件下单独启动和运行,通过相互之间的通信来完成所需的协作。异步电路通常采用握手协议来确保数据的正确传输,即在发送方发送数据

2023-12-07 10:53:42 5316

5316 不良影响。本文将详细介绍异步信号与同步电路交互问题的背景、常见的问题及其解决方法。 一、背景 在现代电子系统中,通信和交互已经成为不可或缺的一部分。为了实现设备之间的信息传递和控制,我们常常会使用各种不同的信号

2023-12-07 10:53:45 1525

1525 同步复位和异步复位到底孰优孰劣呢? 同步复位和异步复位是两种不同的复位方式,它们各自有优势和劣势,下面将详细介绍这两种复位方式。 同步复位是指在时钟的边沿(上升沿或下降沿)发生时对系统进行复位。这种

2024-01-16 16:25:52 2718

2718 什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号是一个

2024-01-25 15:40:52 15221

15221 脉冲触发器和边沿触发器是数字电路中常用的存储器元件。它们都是根据输入信号的变化状态进行触发,并且可以实现特定的功能。然而,它们在触发方式、触发条件和触发时机等方面存在一些差异。本文将详细介绍脉冲

2024-02-06 13:45:50 6967

6967 FPGA(现场可编程门阵列)在处理异步信号时,需要特别关注信号的同步化、稳定性以及潜在的亚稳态问题。由于异步信号可能来自不同的时钟域或外部设备,其到达时间和频率可能不受FPGA内部时钟控制,因此处理起来相对复杂。以下是对FPGA异步信号处理方法的详细探讨。

2024-07-17 11:10:40 2415

2415 统一的时钟信号进行工作,各个部分的输出与输入之间存在固定的时序关系。同步电路通常用于数据传输、存储器、处理器等高速电子系统中。 异步电路(Asynchronous Circuit)是指电路中的各个部分不依赖于统一的时钟信号,而是根据输入信号的变化来控制输出信号

2024-07-22 17:37:00 1227

1227 边沿触发器在数字信号处理器(DSP)中的应用是广泛而重要的。作为数字电路中的关键元件,边沿触发器以其独特的触发机制和稳定的性能,在DSP中扮演着至关重要的角色。以下将详细介绍边沿触发器在DSP中的应用,包括其工作原理、优势、具体应用实例以及未来发展趋势。

2024-07-27 14:51:58 1728

1728 边沿触发器(Edge-Triggered Flip-Flop)是一种数字逻辑电路,其状态变化由输入信号的边沿控制,即由输入信号从低电平变为高电平或从高电平变为低电平的瞬间触发。边沿触发器广泛应用

2024-08-09 17:29:06 1766

1766 边沿触发器是一种数字逻辑电路,其动作特点主要体现在以下几个方面: 触发方式:边沿触发器的动作是由输入信号的边沿变化引起的。当输入信号从低电平变为高电平或从高电平变为低电平时,触发器的状态会发生改变

2024-08-09 18:17:38 2022

2022 作为双稳态电路的一种,其输出状态Q在时钟信号的上升沿或下降沿(具体取决于触发器的设计)到来时,会根据输入信号D的状态进行翻转或保持不变,从而实现对信号的存储和传输功能。 在数字电子系统中,边沿式D触发器被广泛应用于各种

2024-08-22 10:15:40 2377

2377 边沿JK触发器是一种数字逻辑电路,广泛应用于数字电路设计中。它具有多种功能,包括同步操作、存储数据、实现时序逻辑等。以下是对边沿JK触发器功能的分析: 同步操作 边沿JK触发器是一种同步触发器,它在

2024-08-28 09:50:12 2291

2291

电子发烧友App

电子发烧友App

评论