大家在电子行业工作的工程师们,所做的产品多种多样,所设计的电路模块也多种多样,那么有某些产品他的电路组成模块就会设计到我们的高速电路,大家可能如果之前没有接触高速电路的话,可能对“高速”没有概念,那么究竟速率多高才能称为高速电路呢,平时我们应该如何区分高速和低速呢?

大家可能会认为信号周期频率 FCLOCK 高的才属于高速设计

其实我们在设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率) Fknee

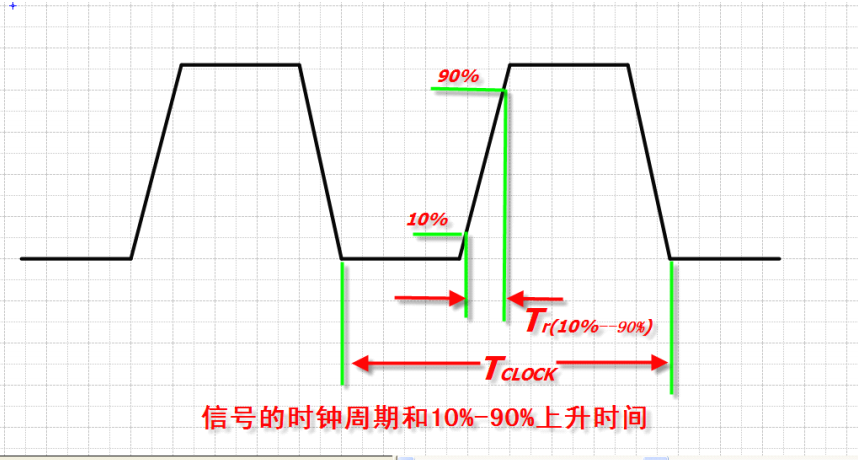

如上图信号周期频率与有效(转折)频率定义为:

FCLOCK = 1/Tclock

Fknee = 0.5/Tr(10%−90%) (实际中多数信号而言)

一般而言,在信号传输路径的长度(即信号线的长度)小于信号的有效波长的 1/6 时, 可以认为在该传输路径上,各点的电平状态近似相同。由信号波长与频率的关系 λ = c / F , 我们可以按下面的步骤进行高速低速的区分;1 获得信号的有效频率 Fknee 和走线长度 L; 2 利用 Fknee 计算出信号的有效波长 λknee;3 判断 L 与 1/6λknee的关系,若 L>1/6λknee,则信号为高速信号;反之,则为低速信号。

总之,我们通常认为数字逻辑电路的频率达到或者超过50MHz,而且工作在这个频率之上的电路已经占到了整个电子系统相当的分量,例如三分之一,就称为高速电路。而实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿引发了信号传输的各种问题。所以,当信号所在的传输路径长度大于1/6倍传输信号的波长时,信号被认为是高速信号;当信号沿着传输线传播时,发生了严重的趋肤效应和电离损耗时,认为是高速信号。因此,通常约定如果电路板上信号的传播延迟大于一半数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应,这样的电路就是高速电路。

声明:-

pcb

+关注

关注

4418文章

23990浏览量

426584

原文标题:平时我们所说的高速电路该怎么区分呢?

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电机如何区分级数

怎么区分快充和普通充电器?从倍思氮化镓快充看核心差异

超高速单电源比较器AD8611/AD8612:开启高速电路设计新境界

系统调用和API有什么区别呢?

隔离地过孔要放哪里,才能最有效减少高速信号过孔串扰?

如何从电容值去区分电容的类型及使用范围

【「高速数字设计(基础篇)」阅读体验】 + 书籍评测第一篇

【书籍评测活动NO.66】玩转高速电路:基于ANSYS HFSS的无源仿真实例

不是8万也不是13万,高速风筒为什么偏偏是11万转速呢?--【其利天下】

这4个高速风筒方案,哪个容易被淘汰?

平时我们所说的高速电路该怎么区分呢?

平时我们所说的高速电路该怎么区分呢?

评论