点击上方蓝字关注我们

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中摄像头系统的快速启动时间要求就是很好的一个例子——车辆启动后后视图像在仪表板显示屏上的显示速度是最为突出的设计挑战。

上电后,FPGA立即加载存储于NOR器件中的配置比特流。传输完成后,FPGA转换为活动(已配置)状态。FPGA包括许多配置接口选项,通常包括并行NOR总线和串行外设接口(SPI)总线。支持这些总线的存储器在不同厂商的产品之间总是存在微小的不兼容性,增添了采购多款存储器件的困难程度。

全新发布的JEDEC xSPI规范由各大主要NOR闪存厂商联合制定。新标准结束了数十年来NOR闪存厂商独立开发产品、各自为政的局面。虽然存在细微差别,但目前各厂商产品的核心JEDEC xSPI功能已完全相同。JEDEC xSPI规范对总线事务、命令和大量内部功能进行了标准化。结合高吞吐量这一性能,这些下一代闪存可实现全新的应用和功能。例如,赛普拉斯Semper NOR Flash系列符合JEDEC xSPI规范,并提供持续400MB /s读取传输速率,非常适合作为FPGA配置存储器。具体而言,凭借400MB/s的数据速率,容量为128MB(1Gb)的器件,其内容可在320ms内完成传输。

FPGA配置历史回顾

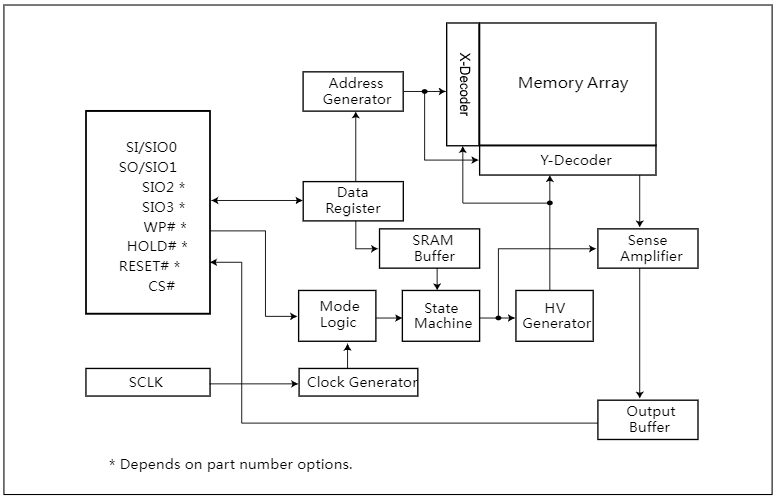

当FPGA首次面世时,可选择的配置存储器是并行EPROM或并行EEPROM产品。随着时间的推移,NOR闪存技术应运而生,同时因其系统内可重复编程性和高性价比而被广泛采用。在第二次革命性转折中,SPI存储器接口在大多数应用中取代了并行NOR接口。今天的SPI存储器产品具有高密度、小封装尺寸和高读取吞吐量,以及最重要的特点——更高效的低引脚数接口。

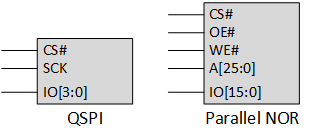

图1 - 千兆位四路SPI(6引脚)和并行NOR(45引脚)接口

图1显示了千兆位SPI器件与千兆位并行NOR的引脚分配的对比。对于一个千兆位存储器,四路串行外设接口(QSPI)器件具有六引脚接口,而并行NOR器件则需要45个引脚。引脚数量的巨大差异导致QSPI器件作为首选配置接口而被广泛采用。QSPI接口允许在不改变器件占用空间的情况下更改密度。

FPGA配置速度

随着工艺节点缩小,FPGA器件得以继续增加可用的可编程逻辑模块数量,进而导致对更高密度和更快速度配置存储器的需求。现代FPGA在配置期间需要加载多达128MB的数据。这些高密度配置比特流需要更长的时间才能从NOR闪存器件传输到FPGA。配置接口不仅针对读取吞吐量进行了优化,还专注于促进不同NOR闪存制造商之间的互操作性。

SPI读取吞吐量

过去几年,从最初以x1模式运行的SPI接口开始,一直到以x4 DDR模式运行的现代QSPI产品,SPI读取吞吐量发生了显著增长。从表1可以看出,下一代闪存器件能够推动SPI总线性能实现又一次跃迁。

|

总线类型 |

总线宽度 |

P引脚数 |

时钟频率(MHz) |

传输类型 |

数据吞吐量(MB/秒) |

|

SPI |

x1 |

4 |

20 |

SDR |

1.5 |

|

QSPI |

x4 |

6 |

133 |

SDR |

66 |

|

QSPI |

x4 |

6 |

80 |

DDR |

80 |

|

xSPI |

x4 |

7 |

200 |

DDR |

200 |

|

xSPI |

x8 |

11 |

200 |

DDR |

400 |

表1 - 闪存器件SPI读取吞吐量选项

现代SPI器件能够永久配置为固定的总线宽度和传输类型,可在上电时立即运行。FPGA须支持这一永久配置,以便在上电后立即启动配置过程。

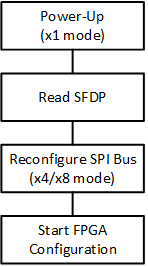

又或者,SPI存储器可在x1模式下退出通电状态,从而允许主机系统(FPGA)查询存储器中的串行闪存可发现参数(SFDP)表中的特性。这一x1模式已成为多家存储器厂商支持的标准功能,并允许FPGA检索有关器件功能的关键信息。一旦检索到器件特性,就可以快速重新配置FPGA存储器控制器和SPI存储器器件,以获得最大的读取性能。

图2 - 通电时使用串行闪存可发现参数(SFDP)表配置SPI总线功能

在选用可使用x1、x4或x8总线宽度以及SDR或DDR传输类型运行的下一代闪存设备时,使用集成SFDP表检索关键设备信息将格外重要。所选择的总线宽度和传输类型必须与FPGA上实现的总线接口基础设施保持一致。

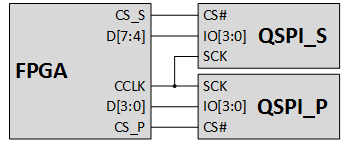

双QSPI配置接口

为减少FPGA配置时间,许多现代FPGA允许将配置位流分区至两个QSPI器件(图3)。这两个QSPI器件以并行方式连接,其中位流的低半字节存储在“主”QSPI器件(QSPI_P)中,位流的高半字节存储在“辅助”QSPI器件(QSPI_S)中。这两个器件在加载位流时并行运行,从而有效地使读取数据传输速率提升一倍。

请注意,除共享SCK(串行时钟)线以外,接口在两个器件上基本上是独立的。之所以要共享SCK线,是为了在以并行方式(即同时)读取器件时实现时序偏差最小化。当使用相同目标地址执行相同操作时,可以一次仅对一个器件进行访问,也可以同时对两个器件进行访问。

图3 - 双QSPI配置接口(11个引脚)允许配置位流在两个QSPI器件之间进行分区,从而有效地将读取数据传输速率提升一倍。

当大型FPGA器件需要以最快的方式传输大配置(即高密度)配置比特流时,这种11引脚双QSPI配置将具有非常大的优势。

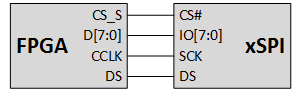

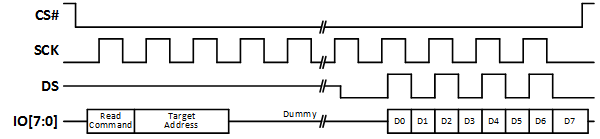

闪存配置

下一代闪存采用x1(主要用于SFDP访问)、x4或x8 IO总线宽度运行,支持SDR或DDR格式传输数据,并且通过使用新的数据选通(Data Strobe)信号以促进高速传输。例如,使用11引脚接口的赛普拉斯Semper NOR闪存八进制配置(图4)。

图4 - 低引脚数接口支持SDR或DDR格式的x1、x4或x8 IO总线宽度传输数据。图中显示的是采用11引脚接口的赛普拉斯Semper NOR闪存八进制配置。

这一新的数据通选必须结合到FPGA配置接口中,从而可利用下一代闪存器件的高吞吐量读取性能。数据选通与输出读取数据边缘对齐,其方式与低功耗DDR DRAM器件上的选通方式相同(图5)。数据选通“绘制”数据眼图,并允许FPGA以高时钟频率有效抓取数据。

图5 - 具有数据选通功能的x8 DDR读取事务与输出读取数据边缘对齐,使FPGA能够以高时钟频率有效抓取数据。

支持连续读取操作是非常适用于FPGA配置的闪存功能之一。连续读取始于主机(MCU(微控制器)或FPGA)置位CS#(CS片选引脚),然后发出读取命令,后跟目标地址。经过多次延迟周期,存储器从目标地址输出数据。如果主机继续切换时钟,则存储器将通过从下一个顺序地址输出数据来响应。只要时钟继续切换,存储器将继续从顺序地址输出数据。这种顺序读取功能可以允许FPGA配置单个读取事务。

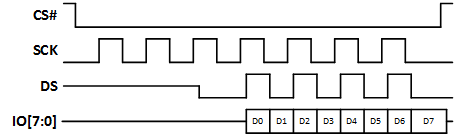

AutoBoot(自动启动)是另一项有助于FPGA配置的功能。AutoBoot在通电复位期间从预先配置的目标地址执行自动读取,然后在第一次CS#置位时立即输出数据(图6)。此功能对需要简单配置机制的ASIC(专用芯片)器件也十分有用。一旦CS#解除置位,内存将返回其待命状态,并以正常方式处理后续操作。

图6 - 运行中的AutoBoot读取功能(具有3个预热周期)

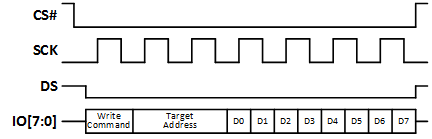

NOR 闪存器件的写入事务(图7)与标准SPI操作几乎完全相同,但有两点例外。首先,在整个事务期间必须将新的数据选通信号驱动为LOW(低电平)。其次,当配置为DDR操作时,数据被写为字(16b),而非传统SPI产品的字节写编程粒度。

图7- NOR 闪存的写入事务需要在整个事务期间将数据选通信号驱动为LOW,并且在配置为DDR操作时将数据写为16位字。

下一代NOR闪存器件可提供满足大规模FPGA应用的高密度和随开即用要求所需的高吞吐量。各大NOR闪存制造厂商都参与了JEDEC xSPI规范的开发,为代工厂商提供了广泛的采购选择。JEDEC xSPI规范涵盖了上述八进制SPI接口以及HyperBus接口,两者均提供400MB/s的读取吞吐量,已实现的读取吞吐量远高于传统SPI产品。为利用高速基础设施,需要对FPGA SPI控制器进行修改。需要考虑的新功能包括DDR数据速率,用于数据抓取的新数据选通引脚和扩展的x8总线接口。此外,一些NOR闪存器件(例如赛普拉斯Semper NOR系列)允许在实施双QSPI配置架构时消除其中一个QSPI器件。在需要进行快速FPGA配置的情况下,以及在执行实时重新配置的FPGA应用中,下一代闪存所提供的性能将具有强大的优势。

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:使用高速NOR闪存配置FPGA

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1655文章

22282浏览量

630060

原文标题:使用高速NOR闪存配置FPGA

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高性能SPI NOR FLASH芯片ZB25VQ系列推荐

如何在 IAR Embedded Workbench for ARM 开发环境中启用可配置数据闪存并设置大小?

普冉NOR FLASH助力IPC摄像头高效运行

什么是Flash闪存以及STM32使用NAND Flash

昂科烧录器支持Macronix旺宏电子的串行NOR闪存存储器MX25U51245G

使用高速NOR闪存配置FPGA

使用高速NOR闪存配置FPGA

评论