易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对应的。对于易灵思的FPGA来讲,PLL,GPIO,MIPI,LVDS和DDR相对于core部分都是外设。而这些外设的设置都是在interface designer中的。下面以pll的添加为例,对于trion系列的设置简单说明。钛金系列会稍微的区别,但是只要了解了一个,另一个都是大同小异的。

一、PLL的添加

(1)打开interface desinger。

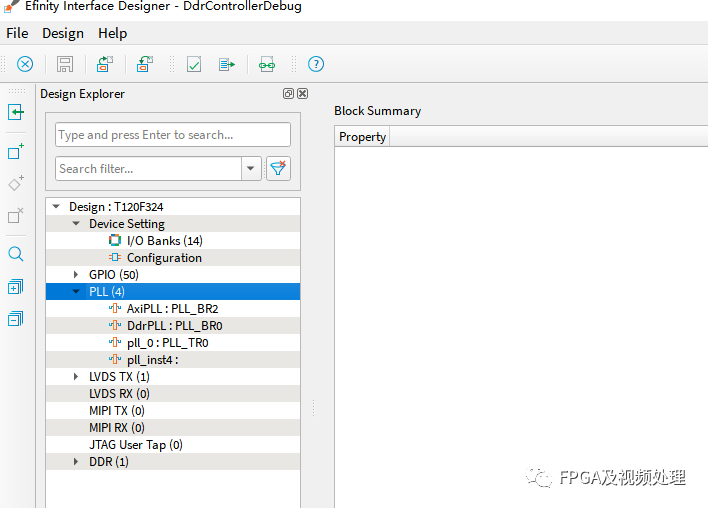

(2)选择pll 右击选择Create block,就可以添加pll

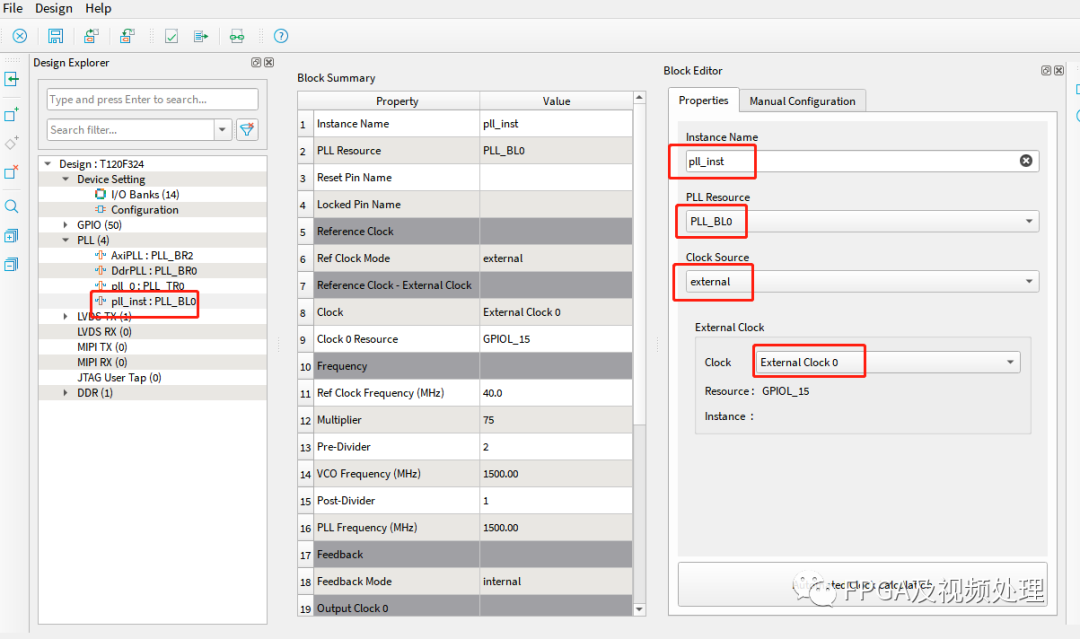

(3)这里我们把pll的例化名修改为pll_inst,并且按回车(必须回车)。

PLL resource对应PLL的位置,这也是易灵思的PLL使用与别家有区别的地方,必须要指定PLL的位置。

clock source是指pll参考时钟的源来自哪里,包括外部和内部。

External clock:指示参考时钟的源,包括参考时钟0,参考时钟1。

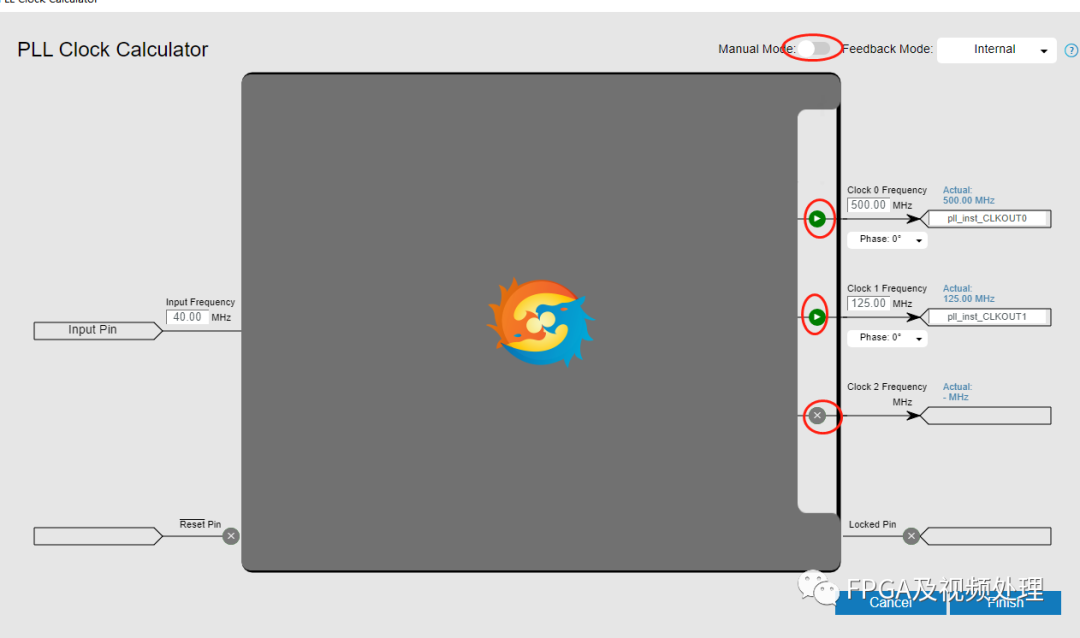

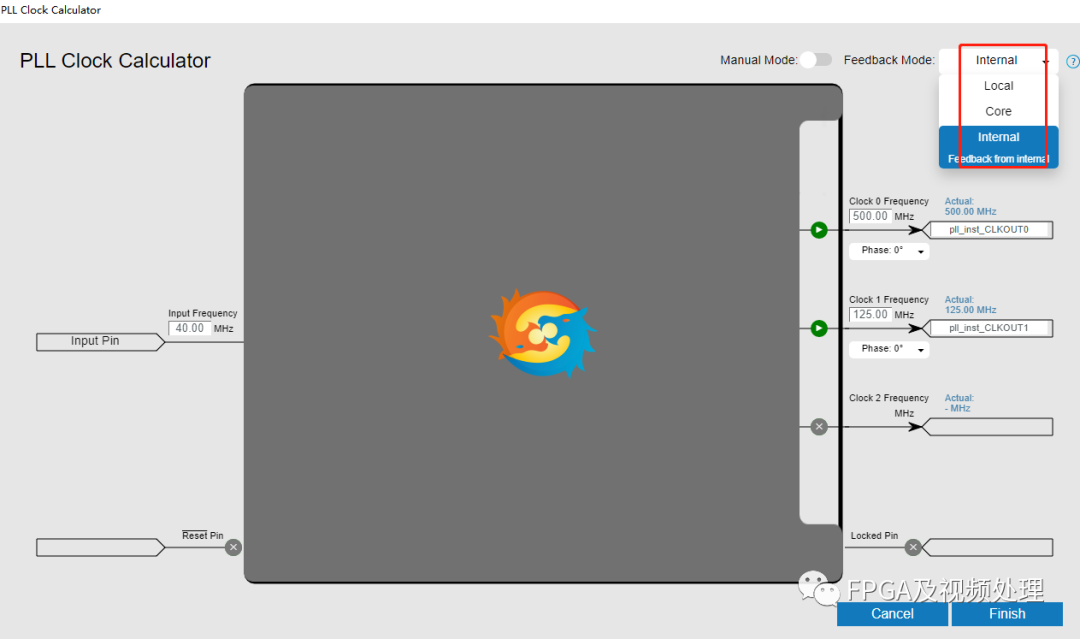

(4)点击Automated Clock Calculation打开时钟设置界面。trion最多可以设置3个时钟,红包框中的箭头和x可以用于打开和关闭相应的时钟。

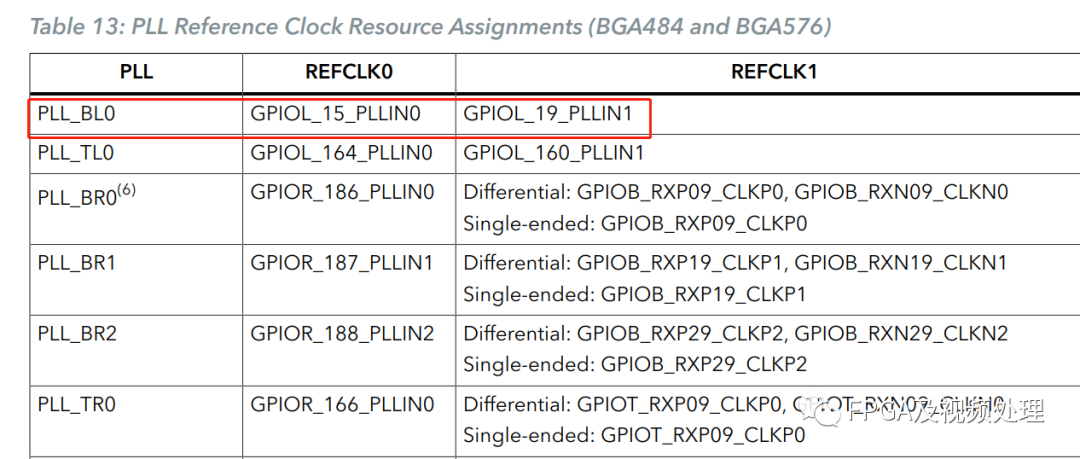

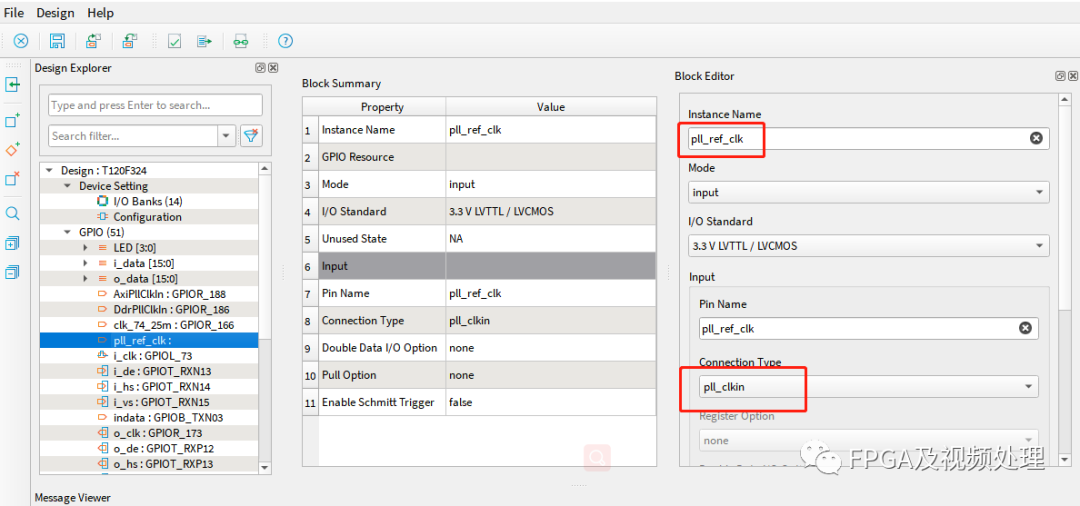

(5)设置完成上面的操作之后,我们需要指定PLL的参考时钟来源。从ds上我们可以看到PLL_BL0有两个时钟源,分别是REFCLK0和REFCLK1,分别对应GPIOL_15_PLLIN0和GPIOL_19_PLLIN1。

然后再添加PLL的参考时钟脚,这里我们例化为pll_ref_clk,并要把connection Type设置为pll_clkin。并分配到GPIOL_15_PLLIN0上,因为上面选择了External Clock0。这样PLL的设置就差不多了。

二、关于时钟源

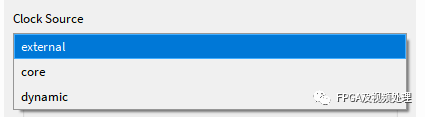

在选择clock source时,有三个选项,分别是external, core和dynamic。

external好理解,就是参考时钟从外部IO进入的,上面的设置就是。

core是指时钟从FPGA内部给PLL的参考,比如一个PLL的输出给另一个PLL做参考时,第二个PLL的参考就是设置成core,或者从GCLK进入FPGA再环到PLL的输入。

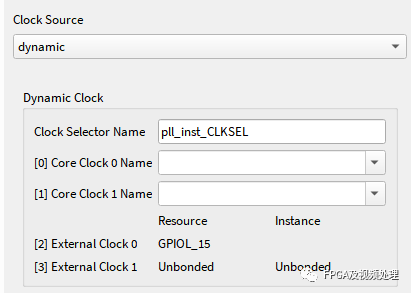

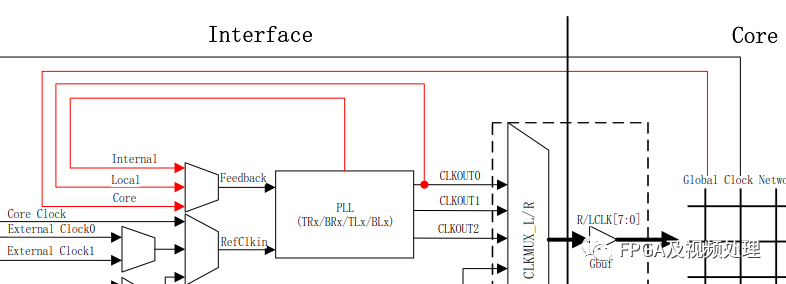

至于Dynamic Clock就是动态输入选择,支持多路选择,如下图,可以支持两个core和两个external时钟。但是因为PLL不支持动态重配置,所以这个功能应用有限。

三、PLL的反馈方式

PLL有三种反馈,core,Local和internal。

从下面的图来看,不同的反馈位置是不一样的。core的反馈路径是从FPGA的core内部来反馈,可以保证输入时钟与输出时钟同频同相。这在源同步设计中是很有用的。而local和internal可以支持输出更多的频率,大家可以在操作中发现如果是core反馈的话,有些频率是设置不出来的,而local和interanl却可以。

关于PLL的注意事项

(1) PLL的反馈时钟的频率不能超过refclk的4倍。

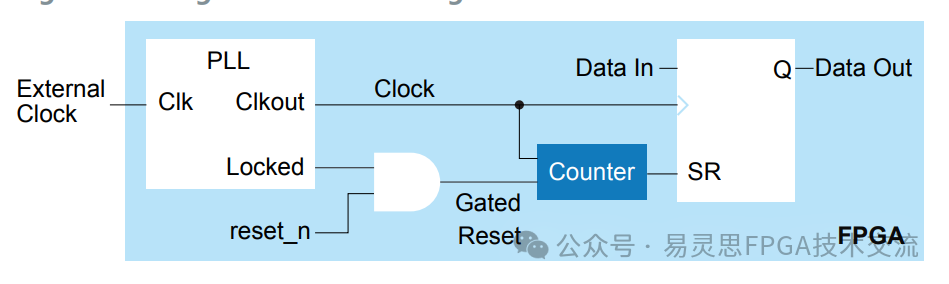

(2)经常会有客户反应上电之后PLL存在失锁的情况,这是什么原因呢?这个是因为上电时PLL的参考时钟不稳定,造成PLL不能锁定在固定的频率,这样之后,即使后继参考时钟稳定也不能锁定。

那解决方案是什么呢?要求等参考时钟稳定之后再释放PLL的复位,或者等参考时钟稳定之后再复位一次。

(3)当需要使用PLL的locked信号做为复位时,要求pll的locked信号拉高25us之后再释放复位。如下图,在locked信号之后添加计数器,记数到25us之后释放器件的SR。

上面描述其实描述相对粗糙,语句什么的也没有太去考虑措辞,花半个小时BB下,能用起来就行,如果实在有看不懂的,欢迎留言。

审核编辑 黄宇

-

pll

+关注

关注

6文章

976浏览量

137592

发布评论请先 登录

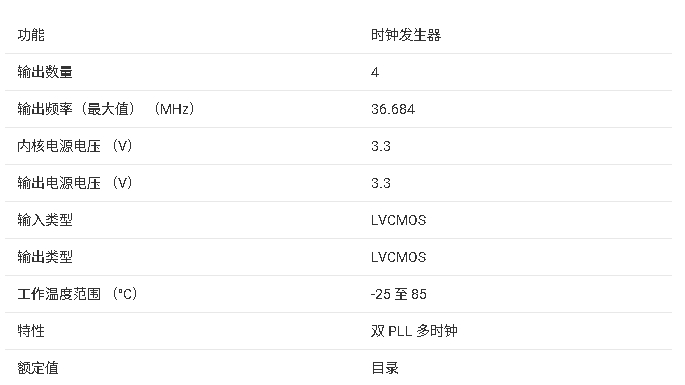

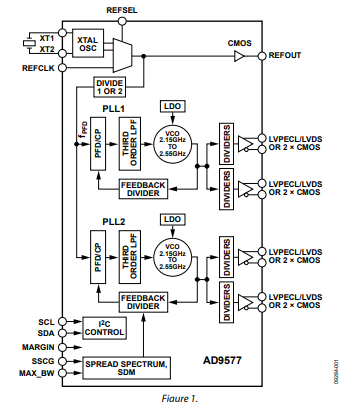

PLL1708双PLL多时钟发生器技术文档总结

PLL1707/PLL1708 双PLL多时钟发生器技术文档总结

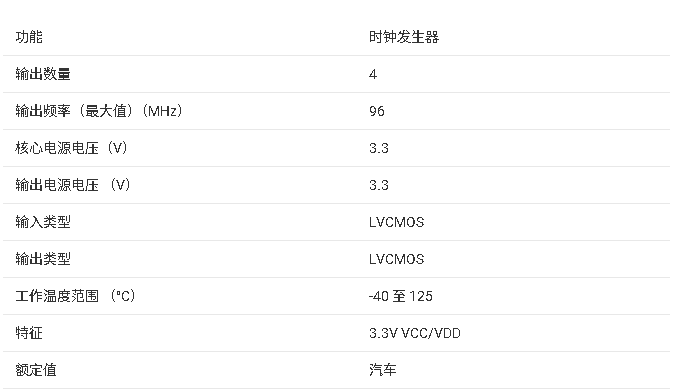

PLL1707-Q1 3.3V双PLL多时钟发生器技术文档总结

易灵思 FPGA TJ375的PLL的动态配置

PLL技术在FPGA中的动态调频与展频功能应用

智多晶PLL使用注意事项

原厂方案:利用力科示波器设置PLL参数

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc

harmony OS NEXT-Navagation基本用法

锁相环(PLL)电路设计与应用(全9章)

AD9577带双路PLL、扩频和余量微调功能的时钟发生器技术手册

PLL用法

PLL用法

评论