No.1引言

随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在FPGA中的动态调频与展频功能应用。

No.2PLL技术基础

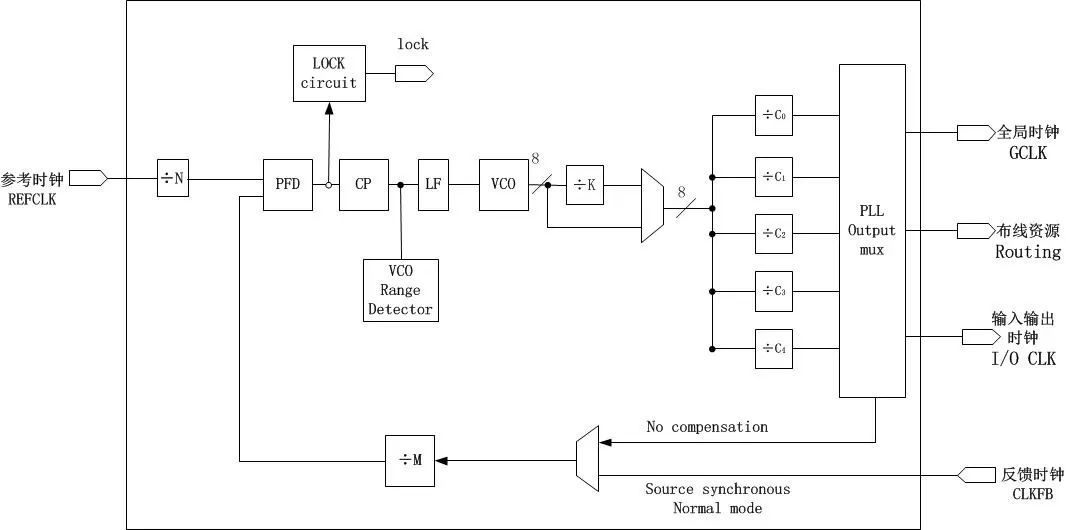

PLL(Phase-Locked Loop,相位锁定环)是一种反馈控制系统,用于生成和稳定时钟信号。它主要由鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和分频器组成。PLL通过不断调整VCO的输出频率,使其与参考时钟信号保持稳定的相位关系,从而实现高精度的时钟合成。

在FPGA中,PLL模块提供了可靠的时钟管理与综合功能,支持精准分频和动态调频。通过PLL,FPGA可以生成多个不同频率的时钟信号,满足复杂系统对时钟资源的需求。

No.3动态调频功能应用

动态调频是指通过编程方式实时调整PLL输出时钟的频率。这一功能在需要灵活配置时钟频率的应用场景中尤为重要,如通信系统中的频率跳变、测试设备中的时钟校准等。

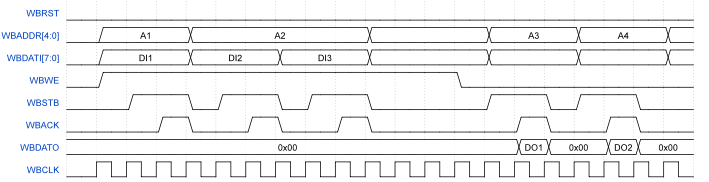

在Seal 系列FPGA中,动态调频功能通过WISHBONE数据总线实现。用户可以通过编程方式动态调整PLL的分频系数,从而改变输出时钟的频率。这一过程无需对FPGA工程进行反复编译和配置,大大提高了开发效率。

WISHBONE数据总线时序

通过配置PLL的动态调频功能,用户可以根据系统需求实时调整时钟频率。例如,在无线通信系统中,可以根据信道切换的需求动态调整本地振荡器的频率,实现快速频率跳变。

No.4展频功能应用

展频时钟(Spread Spectrum Clocking, SSC)技术是一种通过动态调整时钟频率来降低电磁干扰(EMI)的方法。它将时钟信号的频谱能量分散到一定的频率范围内,从而降低在单一频点上的峰值能量,减少电磁干扰。

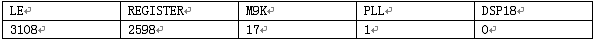

例如,在智多晶的SA5Z- 30 FPGA中,展频功能通过PLL的精准分频和动态配置实现。用户可以通过编程方式动态调整PLL参数,从而改变输出时钟的频率。通过周期性地调整这些参数,可以实现时钟信号的展频效果,可以有效降低时钟信号的电磁干扰,提高系统的电磁兼容性。在高性能计算系统中,可以通过展频技术减少时钟信号对其他敏感电路的干扰,提高系统的整体稳定性。

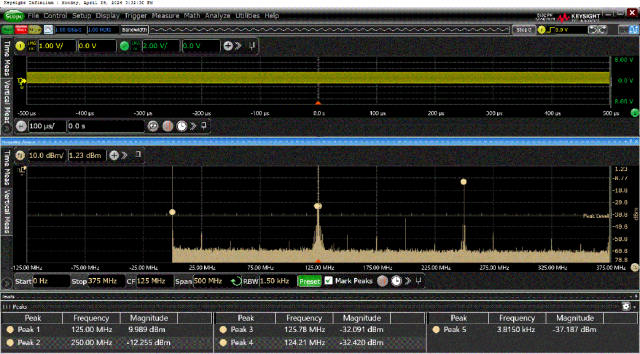

没有启动SSC功能时,对125 MHz时钟信号进行测试,此时看示波器FFT图,可以看出时钟频率在125 MHz集中,容易产生电磁干扰(EMI)的风险。

未启动展频信号测试

SSC功能打开,测试展频后的125 MHz时钟信号,查看FFT图,时钟频率分散在125 MHz附近,从而降低了电磁干扰(EMI)的风险。

启动展频信号测试

No.5结论

PLL技术在FPGA中的动态调频与展频功能应用为现代电子系统设计提供了强大的支持。通过灵活配置PLL参数,用户可以实现实时调整时钟频率和降低电磁干扰的目标,满足复杂系统对时钟资源的高要求。随着技术的不断发展,PLL技术将在更多领域发挥重要作用,推动电子系统的性能提升和创新发展。

本文基于西安智多晶微电子有限公司提供的《AN05104_SA5Z-30 SA5Z-30 PLL展频功能应用指导》和《AN05001_Seal 5000 FPGA PLL动态调频应用指导》两篇技术文档编写,技术文档可在智多晶微电子有限公司官网进行查阅。希望本文能对您在FPGA设计和开发中有所帮助。如果对PLL在FPGA中的使用有疑问,欢迎咨询西安智多晶微电子有限公司的技术支持团队!

-

FPGA

+关注

关注

1655文章

22287浏览量

630327 -

滤波器

+关注

关注

162文章

8355浏览量

184772 -

pll

+关注

关注

6文章

976浏览量

137592 -

时钟管理

+关注

关注

0文章

17浏览量

8509

原文标题:“芯”技术分享 | PLL技术在动态调频与展频功能的应用

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PLL技术在FPGA中的动态调频与展频功能应用

PLL技术在FPGA中的动态调频与展频功能应用

评论