完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

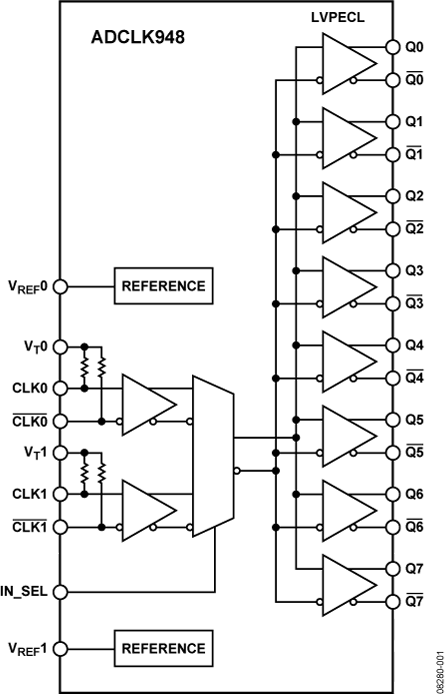

该器件具有两个差分输入,通过IN_SEL控制引脚进行选择。两个输入均配备中心抽头、差分、100 Ω片内端接电阻,接受直流耦合LVPECL、CML、3.3 V CMOS(单端)以及交流耦合1.8 V CMOS、LVDS和LVPECL输入。提供VREFx引脚用于偏置交流耦合输入。

ADCLK948内置8个全摆幅射极耦合逻辑(ECL)输出驱动器。对于LVPECL(正ECL)工作模式, VCC 偏置至正电源, VEE 偏置至接地。对于ECL工作模式, VCC 偏置至接地, VEE 偏置至负电源。输出级旨在从各端将800 mW直接驱动至端接于VCC -2V的50 Ω负载,从而获得1.6 V的总差分输出摆幅。

ADCLK948采用32引脚LFCSP封装,额定工作温度范围为−40°C至+85°C标准工业温度范围。