三态模型

一个进程从创建而产生至撤销而消亡的整个生命周期,可以用一组状态加以刻划,根据三态模型,进程的生命周期可分为如下三种进程状态: 1. 运行态(running):占有处理器正在运行 2. 就绪态(ready):具备运行条件,等待系统分配处理器以便运行 3. 等待态(blocked):不具备运行条件,正在等待某个事件的完成。

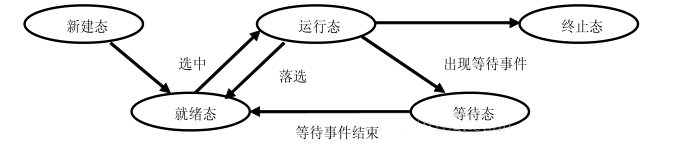

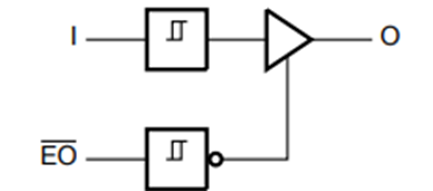

下面是三个状态的转换图:

运行状态的进程将由于出现等待事件而进入等待状态,当等待事件结束之后等待状态的进程将进入就绪状态,而处理器的调度策略又会引起运行状态和就绪状态之间的切换。

引起进程状态转换的具体原因如下:

运行态—→等待态:等待使用资源;如等待外设传输;等待人工干预。

等待态—→就绪态:资源得到满足;如外设传输结束;人工干预完成。

运行态—→就绪态:运行时间片到;出现有更高优先权进程。

就绪态—→运行态:CPU 空闲时选择一个就绪进程。

五态模型

在一个实际的系统里进程的状态及其转换比上节叙述的会复杂一些,例如引入专门的新建态(new)和终止态(exit )

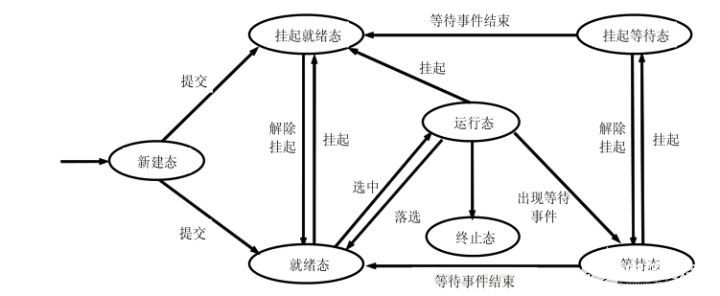

状态转换图如下所示:

新建态对应于进程刚刚被创建的状态。创建一个进程要通过两个步骤,

为一个新进程创建必要的管理信息,

让该进程进入就绪态。此时进程将处于新建态,它并没有被提交执行,而是在等待操作系统完成创建进程的必 要操作。需要注意的是,操作系统有时将根据系统性能或主存容量的限制推迟新建态进程的提交

类似地,进程的终止也要通过两个步骤,首先,是等待操作系统进行善后,然后,退出主存。当一个进程到达了自然结束点,或是出现了无法克服的错误,或是被操作系统所终结,或是被其他有终止权的进程所终结,它将进入终止态。进入终止态的进程以后不再执行,但依然临时保留在操作系统中等待善后。一旦其他进程完成了对终止态进程的信息抽取之后,操作系统将删除该进程。

引起进程状态转换的具体原因如下:

NULL—→新建态:执行一个程序,创建一个子进程。

新建态—→就绪态:当操作系统完成了进程创建的必要操作,并且当前系统的性能和虚拟内存的容量均允许。

运行态—→终止态:当一个进程到达了自然结束点,或是出现了无法克服的错误,或是被操作系统所终结,或是被其他有终止权的进程所终结。

终止态—→NULL:完成善后操作。

就绪态—→终止态:未在状态转换图中显示,但某些操作系统允许父进程终结子进程。

等待态—→终止态:未在状态转换图中显示,但某些操作系统允许父进程终结子进程。

七态模型

进程的挂起

到目前为止,我们或多或少总是假设所有的进程都在内存中。事实上,可能出现这样一些情况,例如由于进程的不断创建,系统的资源已经不能满足进程运行的要求,这个时候就必须把某些进程挂起(suspend),对换到磁盘镜像区中,暂时不参与进程调度,起到平滑系统操作负荷的目的。

引起进程挂起的原因是多样的,主要有:

系统中的进程均处于等待状态,处理器空闲,此时需要把一些阻塞进程对换出去,以腾出足够的内存装入就绪进程运行。

进程竞争资源,导致系统资源不足,负荷过重,此时需要挂起部分进程以调整系统负荷 ,保证系统的实时性或让系统正常运行。

把一些定期执行的进程(如审计程序、监控程序、记账程序)对换出去,以减轻系统负荷。

用户要求挂起自己的进程,以便根据中间执行情况和中间结果进行某些调试、检查和改正。

父进程要求挂起自己的后代进程,以进行某些检查和改正。

操作系统需要挂起某些进程,检查运行中资源使用情况,以改善系统性能;或当系统出现故障或某些功能受到破坏时,需要挂起某些进程以排除故障。

七态模型描述

下面是具有七态模型的进程状态及其转换:

在此类系统中,进程增加了两个新状态:

挂起就绪态(ready,suspend)

挂起就绪态表明了进程具备运行条件但目前在二级存储器中,只有当它被对换到主存才能被调度执行 挂起等待态(blocked,suspend)挂起等待态则表明了进程正在等待某一个事件且在二级存储器中。

引起进程状态转换的具体原因如下:

等待态—→挂起等待态:如果当前不存在就绪进程,那么至少有一个等待态进程将被对换出去成为挂起等待态;操作系统根据当前资源状况和性能要求,可以决定把等待态进程对换出去成为挂起等待态。

挂起等待态—→挂起就绪态:引起进程等待的事件发生之后,相应的挂起等待态进程将转换为挂起就绪态。

挂起就绪态—→就绪态:当内存中没有就绪态进程,或者挂起就绪态进程具有比就绪态进程更高的优先级,系统将把挂起就绪态进程转换成就绪态。

就绪态—→挂起就绪态:操作系统根据当前资源状况和性能要求,也可以决定把就绪态进程对换出去成为挂起就绪态。

挂起等待态—→等待态:当一个进程等待一个事件时,原则上不需要把它调入内存。但是在下面一种情况下,这一状态变化是可能的。当一个进程退出后,主存已经有了一大块自由空间,而某个挂起等待态进程具有较高的优先级并且操作系统已经得知导致它阻塞的事件即将结束,此时便发生了这一状态变化。

运行态—→挂起就绪态:当一个具有较高优先级的挂起等待态进程的等待事件结束后,它需要抢占 CPU,,而此时主存空间不够,从而可能导致正在运行的进程转化为挂起就绪态。另外处于运行态的进程也可以自己挂起自己。

新建态—→挂起就绪态:考虑到系统当前资源状况和性能要求,可以决定新建的进程将被对换出去成为挂起就绪态。

可以把一个挂起进程等同于不在主存的进程,因此挂起的进程将不参与进程调度直到它们被对换进主存。

一个挂起进程具有如下特征:

该进程不能立即被执行。

挂起进程可能会等待一个事件,但所等待的事件是独立于挂起条件的,事件结束并不能导致进程具备执行条件。

进程进入挂起状态是由于操作系统、父进程或进程本身阻止它的运行。

结束进程挂起状态的命令只能通过操作系统或父进程发出。

Linux操作系统的进程状态转换

Linux操作系统的进程

/*

* The task state array is a strange "bitmap" of

* reasons to sleep. Thus "running" is zero, and

* you can test for combinations of others with

* simple bit tests.

*/

static const char * const task_state_array[] = {

"R (running)", /* 0 */

"S (sleeping)", /* 1 */

"D (disk sleep)", /* 2 */

"T (stopped)", /* 4 */

"t (tracing stop)", /* 8 */

"X (dead)", /* 16 */

"Z (zombie)", /* 32 */

};

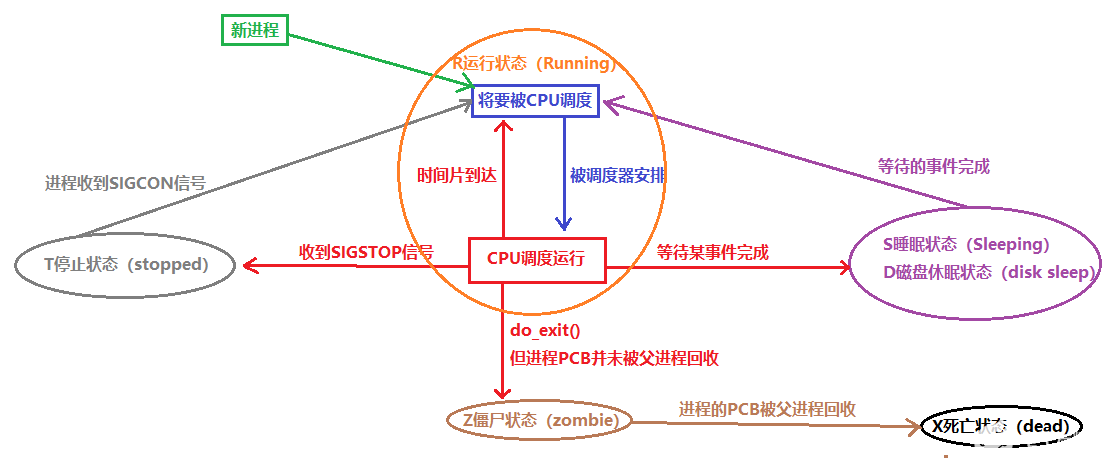

从Linux源码中可以看出,Linux下有7中进程状态:

R运行状态(Running):处于运行状态的进程并不带表一定就正在被CPU调度运行,它包括了正在被CPU运行的进程和可以被CPU调度运行的程序,也就是说改状态包含了三状态模型中的就绪态和运行态。

S睡眠状态(Sleeping):处于改状态的进程表示该进程正在等待某时间的完成,通常也称为可中断睡眠状态,该状态属于三状态模型中的阻塞态。

D磁盘休眠状态(disk sleep):该状态也叫做不可中断睡眠状态,处于该状态的进程通常都在等待I/O操作的结束,该状态也属于三状态模型中的阻塞态。

T停止状态(stopped):我们可以通过向进程发送SIGSTOP信号让目标进程处于停止状态,通过向处于停止状态的进程发送SIGCON信号让目标进程继续运行,该状态也属于三状态模型中的阻塞态。

t追踪停止状态(tracing stop):

X死亡状态(dead):该状态只是一个返回状态,不会在任务列表中见到,该状态属于退出状态。

Z僵尸状态(zombie):当一个进程退出,但它的父进程并没有去收回该进程的信息时,该进程所处的状态叫做僵尸状态,该状态属于退出状态。

Linux系统进程状态间的切换

创建一个新进程,操作系统会为该新进程创建一个空白PCB(task_struct),用来存储该进程的各项信息。

电子发烧友App

电子发烧友App

评论