什么是三态门?

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。 三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态(门,总线,......).

举例来说:

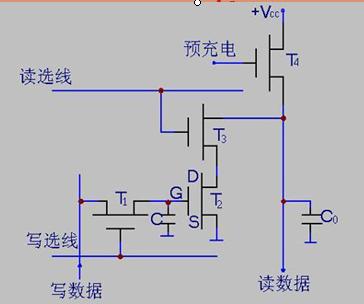

内存里面的一个存储单元,读写控制线处于低电位时,存储单元被打开,可以向里面写入;当处于高电位时,可以读出,但是不读不写,就要用高电阻态,既不是+5v,也不是0v

计算机里面用 1和0表示是,非两种逻辑,但是,有时候,这是不够的,

比如说,他不够富有 但是他也不一定穷啊,她不漂亮,但也不一定丑啊,

处于这两个极端的中间,就用那个既不是+ 也不是―的中间态表示, 叫做高阻态。

高电平,低电平可以由内部电路拉高和拉低。而高阻态时引脚对地电阻无穷,此时读引脚电平时可以读到真实的电平值.

高阻态的重要作用就是I/O(输入/输出)口在输入时读入外部电平用.

1. 三态门的特点

三态输出门又称三态电路。它与一般门电路不同,它的输出端除了出现高电平、低电平外,还可以出现第三个状态,即高阻态,亦称禁止态,但并不是3个逻辑值电路。

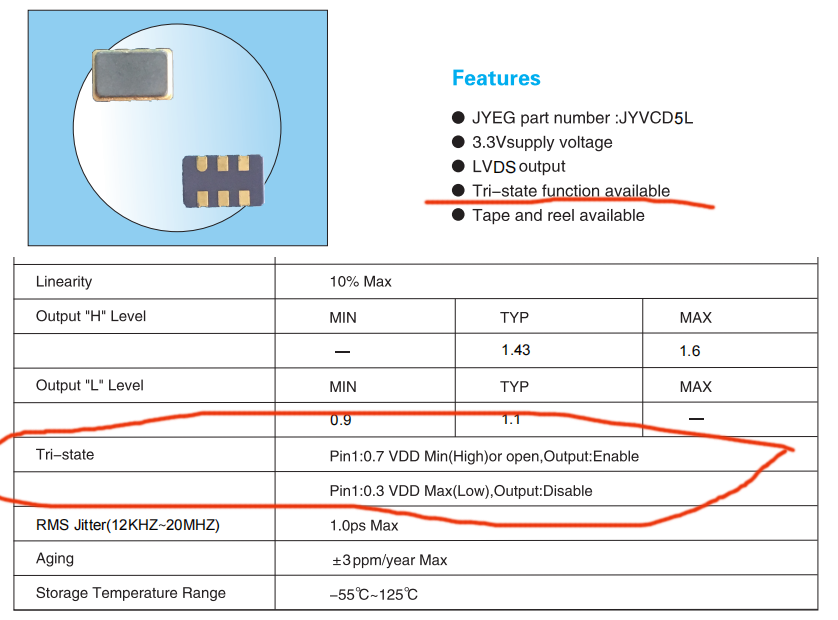

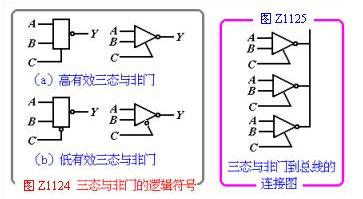

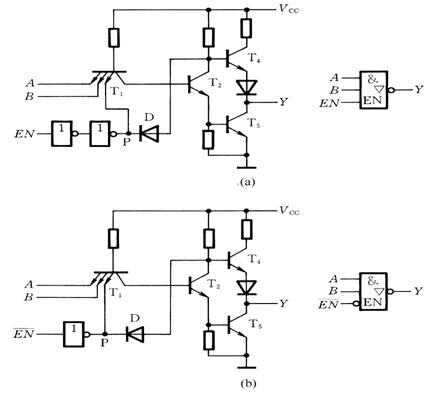

2. 三态逻辑与非门

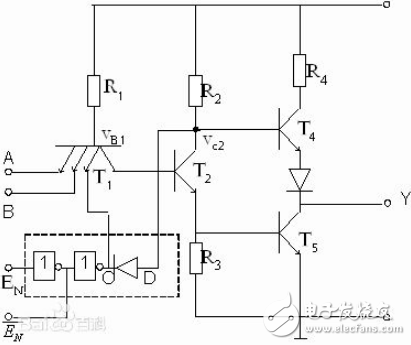

三态逻辑与非门如图Z1123所示。这个电路实际上是由两个与非门加上一个二极管D2组成。虚线右半部分是一个带有源泄放电路的与非门,称为数据传输部分,T5管的uI1、uI2称为数据输入端。而虚线左半部分是状态控制部分,它是个非门,它的输入端C称为控制端,或称许可输入端、使能端。

当C端接低电平时,T4输出一个高电平给T5 ,使虚线右半部分处于工作状态,这样,电路将按与非关系把uI1, uI2接受到的信号传送到输出端, 使uo或为高电平,或为低电平。

当C端接高电平时,T4输出低电平给T5,使 T6、T7、T10 截止。另一方面,通过D2把T8的基极电位钳在1v左右,使T9截止。由于T9、T10均截止,从输出端u0看进去,电路处于高阻状态。

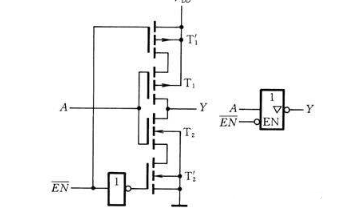

三态逻辑与非门的逻辑符号如图Z1124所示。其中(a)图表示C端为高电平时为工作状态,称为高有效三态与非门。(b)图表示C端为低电平时的工作状态,称为低有效三态与非门。在使用时应注意区分。

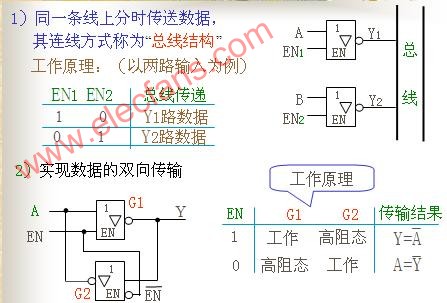

三态与非门的最重要的用途就是可向一条导线上轮流传送几组不同的数据和控制信号,如图Z1125所示,这种方式在计算机中被广泛采用。但需要指出,为了保证接在同一条总线上的许多三态门能正常工作,一个必要条件是,任何时间里最多只有一个门处于工作状态,否则就有可能发生几个门同时处于工作状态,而使输出状态不正常的现象。

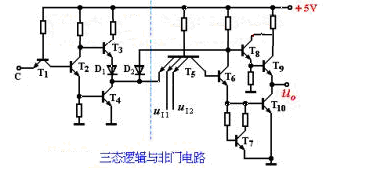

三态输出门电路(TS(Three-state output Gate)门)

上图为三态门输出门电路的原理图。在图中,如果将虚线方框内的两个反相器和一个二极管剪掉,剩下的部分就是典型的TTL与非门电路。

所谓三态是指输出端而言。普通的TTL与非门其输出极的两个晶体管T4、T5始终保持一个导通,另一个截止的推拉状态。T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(vcc)阻抗无穷大。因此这第三种状态也称高阻状态。

现对三种状态进行分析:

控制信号可在EN处加入,也可在![]() 处加入:

处加入:

EN=0,![]() =1,则C=0,vB1=0.9V,vc2=0.9V

=1,则C=0,vB1=0.9V,vc2=0.9V

vB4=vc2=0.9V,T4截止(T4导通的电位vB4>1.4V)

vB1=0.9V,T5截止,输出端Y为高阻状态。

EN=1,![]() =0,C=1,对与非门另两个A、B输入端无影响,为正常的与非门电路。

=0,C=1,对与非门另两个A、B输入端无影响,为正常的与非门电路。

当A=B=1,则T2、T5导通,vc2=1.0V(前已分析)。二极管D处于反相截止状态(因为其阳极电压vc2=1.0V,小于阴极C点电位vIH=3.4V),在电路中不起作用。

若A、B中有一个为0,则T2、T5截止,由于vc2=vIH+0.7=4.1V,足够保证T4导通。

即当EN=1(![]() =0),二极管D在电路中不起作用,电路保持完整的与非门逻辑功能。

=0),二极管D在电路中不起作用,电路保持完整的与非门逻辑功能。

三态门逻辑符号如下:

EN=1,![]()

![]() =0,

=0,![]()

EN=0, Y为高阻状态 ![]() =1,Y为高阻状态

=1,Y为高阻状态

常用逻辑门电路符号:

![]()

![]()

与门 与非门 非门(反相器)

![]()

![]()

![]()

![]()

![]()

![]()

Y=![]()

![]()

OC与非门 三态与非门

(外接集电极电 C=1, ![]()

![]() =0,

=0,![]()

阻后![]() ) C=0,高阻

) C=0,高阻 ![]() =1,高阻

=1,高阻

C=1,Y=A ![]() =0,Y=A

=0,Y=A

C=0,Y高阻 ![]() =1,Y高阻

=1,Y高阻

C=1,![]()

![]() =0,

=0,![]()

C=0,Y高阻 ![]() =1,Y高阻

=1,Y高阻

例题1:试确定下列各TTL门电路的输出Yi(i=1,……16)

确定左边表格中Y16的值。A、B、C三个控制变量能否取000,001,010,100四种组合? 例题2:试画出Y1、Y2 、Y3 、Y4的波形。A、B的波形如下图所示:

请读者自行画出Y3 、Y4的波形。要求在半分钟(30秒钟)内完成。

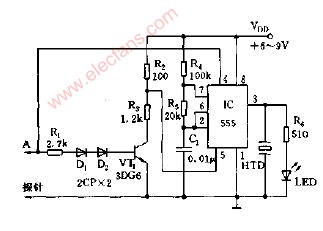

三态门电路

电子发烧友App

电子发烧友App

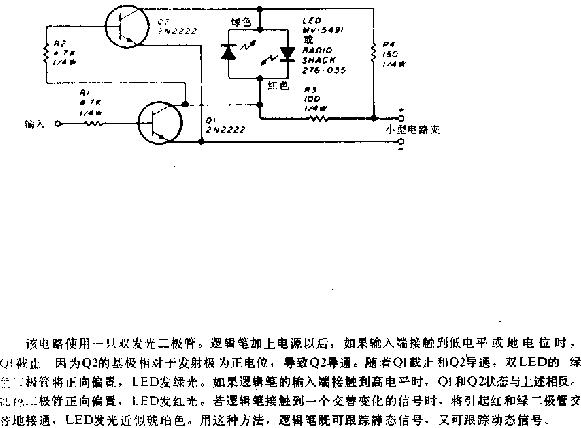

评论