三态输出的缓冲器有哪些用途?

三态输出缓冲器是一种电子元件,其主要作用是将一个输入信号转换成一个可以控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信系统等。在这篇文章中,我们将会详尽、详实、细致地介绍三态输出缓冲器的用途及其原理。

一、三态输出缓冲器的作用

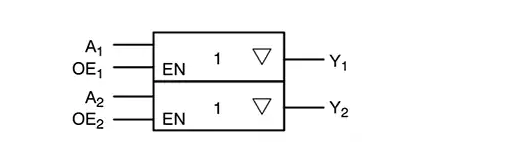

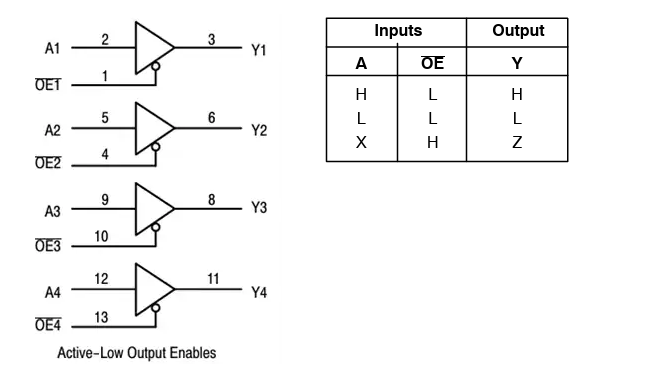

三态输出缓冲器的主要作用是通过输入控制电平控制输出信号。这种缓冲器可以产生三种不同状态:逻辑 0、逻辑 1和高阻态。当输入控制电平为逻辑 0 时,输出设备处于低电平状态。反之,当输入控制电平为逻辑 1 时,输出设备处于高电平状态。当输入控制电平为高阻态,输出设备不会受到任何控制,其输出电平等于输入电平。这样,三态输出缓冲器就可以通过控制输入电平产生逻辑输出。

二、三态输出缓冲器的原理

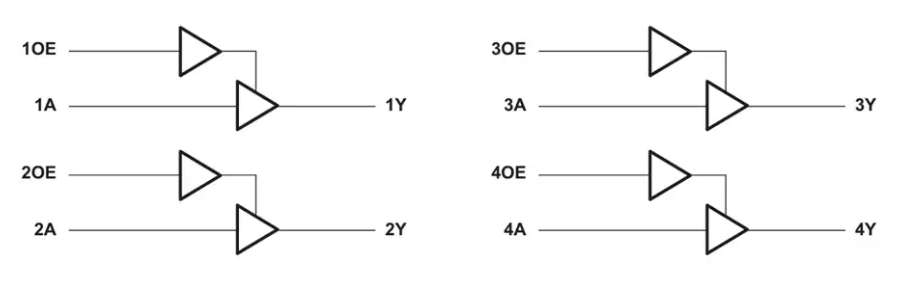

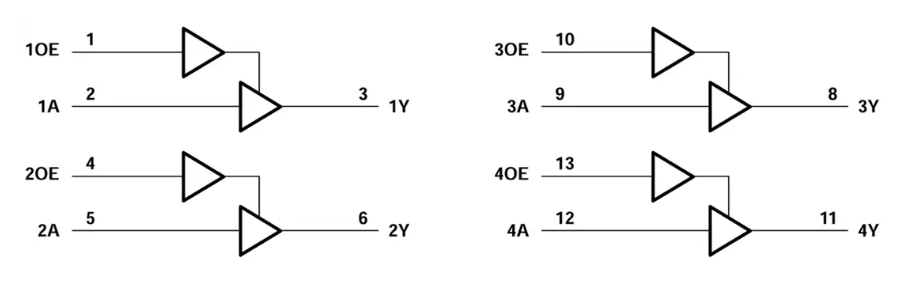

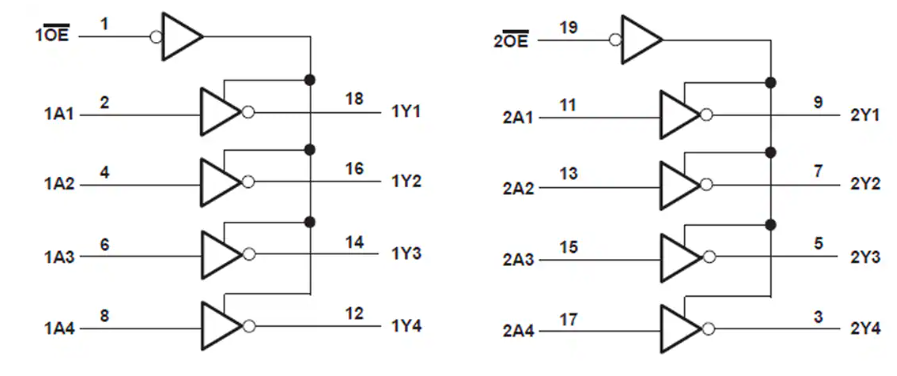

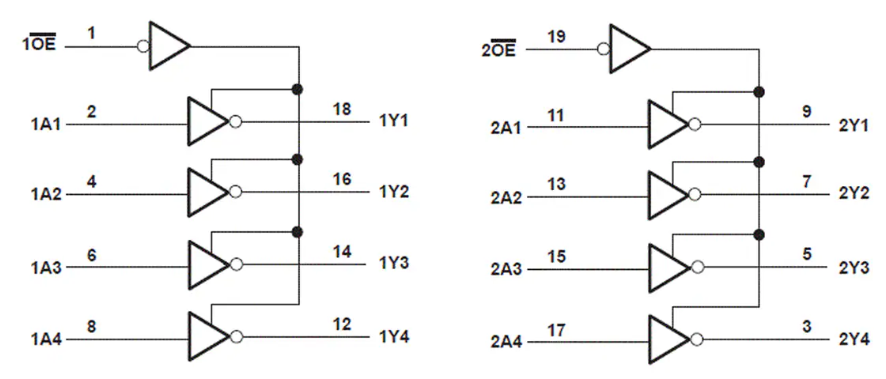

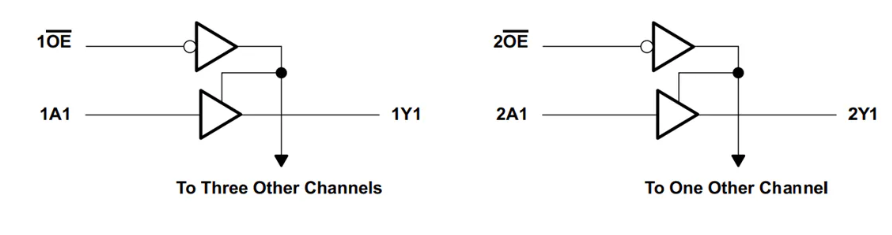

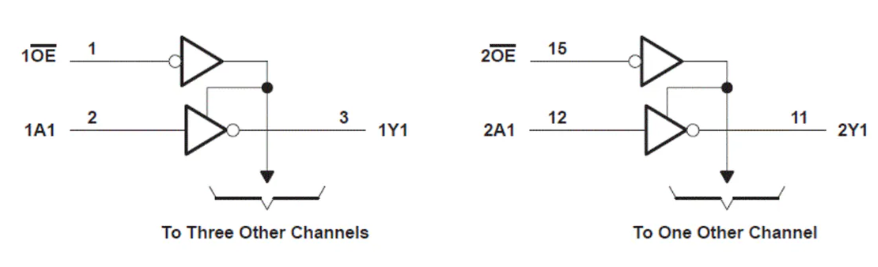

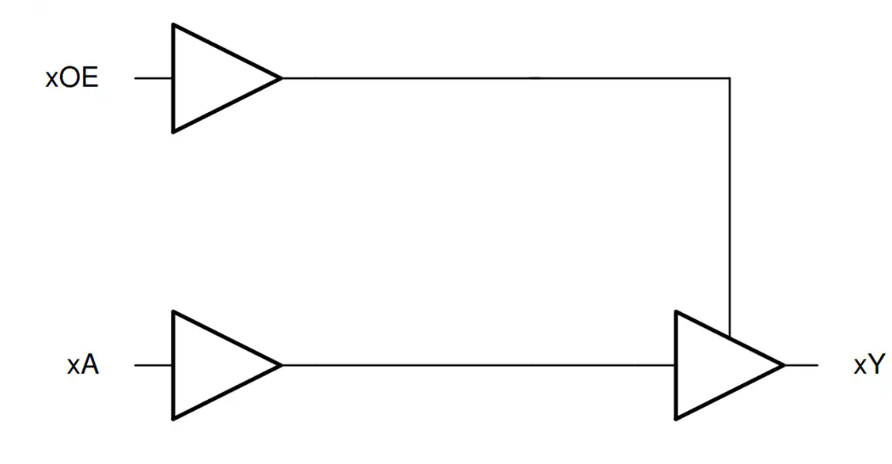

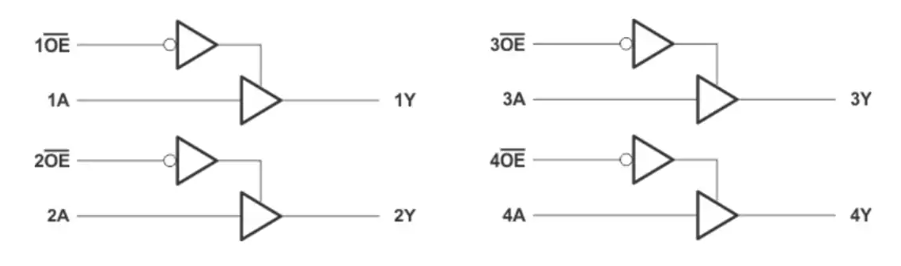

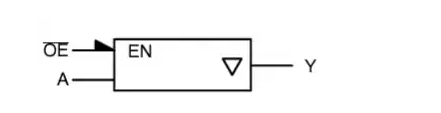

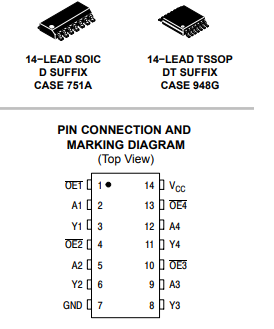

三态输出缓冲器由两个逻辑门构成:输入控制门和输出门。输入控制门通过一个输入信号对输出门进行控制。当输入控制门收到逻辑 1 信号时,输出门被激活,输出逻辑 1 信号。当输入控制门收到逻辑 0 信号时,输出门被禁用,输出逻辑 0 信号。当输入控制门接收到高阻态信号时,输出门将处于不确定状态,也就是高阻。

三态输出缓冲器的输出门可以控制多个输出设备。这些设备可以是门电路、LED 显示器、驱动器等。当输入控制门被激活时,输出设备将会被控制,产生相应的逻辑电平。

三、三态输出缓冲器的应用

1. 数码电路

三态输出缓冲器可以用于数码电路中的多路器和选择器。这些器件可以将多个输入信号映射到不同的输出端口。通过使用控制信号,可以通过控制三态输出缓冲器输出的状态,将一个输入信号分配到多个输出信号中。这些功能对于数字信号的处理尤为重要。

2. 计算机

三态输出缓冲器广泛应用于计算机中。在计算机中,三态输出缓冲器可以用于控制系 统总线和内部总线。总线可以被连接到多个设备,用于在计算机内进行数据传输。通过使用三态输出缓冲器,可以控制总线的状态,使其只能被一个设备访问,以避免竞争等问题。

3. 消费电子设备

三态输出缓冲器还可以用于消费电子设备中。例如,在电视机遥控器中,通过使用三态 输出缓冲器,可以控制多个按键,使之产生相应的控制信号。在音频播放器中,三态输出缓冲器可以用于控制音频信号,并将其输出到扬声器。

4. 通信系统

三态输出缓冲器还可以用于通信系统中。在通信系统中,传输的信号通常是数字信号,因此对于数据传输的处理和控制尤为重要。通过使用三态输出缓冲器,可以控制和处理传输中的数字信号,并将其传输到其他设备中。

综上,三态输出缓冲器具有广泛的应用范围。无论是在计算机系统、消费电子设备、通信系统还是数码电路中,三态输出缓冲器都发挥着重要的作用。三态输出缓冲器的原理和应用是电子工程师们必须要掌握的知识。

-

驱动器

+关注

关注

54文章

9012浏览量

153347 -

缓冲器

+关注

关注

6文章

2215浏览量

48674 -

LED显示器

+关注

关注

1文章

82浏览量

14666 -

门电路

+关注

关注

7文章

202浏览量

41303 -

三态缓冲器

+关注

关注

1文章

12浏览量

4739

发布评论请先 登录

八进制三态同相缓冲器/线路驱动器/线路接收器MC74HC244A和MC74HCT244A详解

NL27WZ126 3态高电平使能双路缓冲器技术解析与应用指南

MC74VHCT125A三态总线缓冲器技术深度解析与应用指南

SN74AHCT126四路总线缓冲器技术解析与应用指南

SN74AHC126四路三态总线缓冲门技术解析与应用指南

Texas Instruments SN74HCT240八通道缓冲器/线路驱动器数据手册

Texas Instruments SN74HC240八通道缓冲器/线路驱动器数据手册

Texas Instruments SN74AHCT367六路缓冲器和线路驱动器数据手册

Texas Instruments SN74HC368六路反相缓冲器数据手册

Texas Instruments SN74HC126四路缓冲器数据手册

Texas Instruments SN74LV125AT四路总线缓冲器闸数据手册

三态输出的缓冲器有哪些用途?

三态输出的缓冲器有哪些用途?

评论