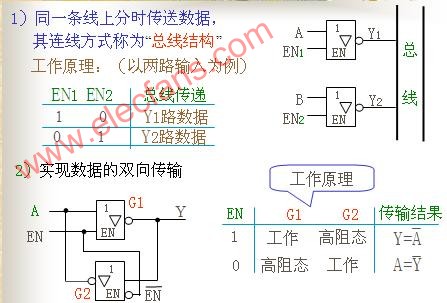

三态门简介:

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。高阻态相当于隔断状态(电阻很大,相当于开路)。高阻态是一个数字电路里常见的术语,指的是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定。

处于高阻抗状态时,输出电阻很大,相当于开路,没有任何逻辑控制功能。高阻态的意义在于实际电路中不可能断开电路。三态电路的输出逻辑状态的控制,是通过一个输入引脚实现的。

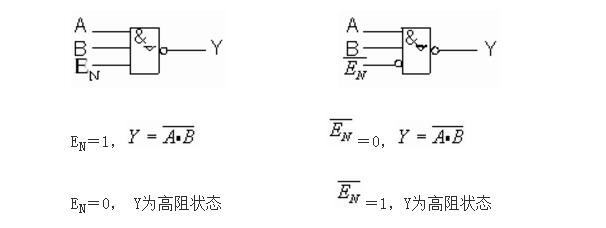

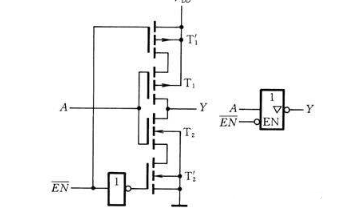

三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态器件。当EN有效时,三态电路呈现正常的“0”或“1”的输

出;当EN无效时,三态电路给出高阻态输出。

三态门在双向端口中运用时,如图所示,设置Z为控制项,当Z=1时,三态门呈高阻状态,上面的线路不通只能输入,当Z=0时,三态门呈正常高低电平的输出状态,可输出,即O路通。三态门是一种扩展逻辑功能的输出级,也是一种控制开关。主要是用于总线的连接,因为总线只允许同时只有一个使用者。通常在数据总线上接有多个器件,每个器件通过OE/CE之的信号选通。如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

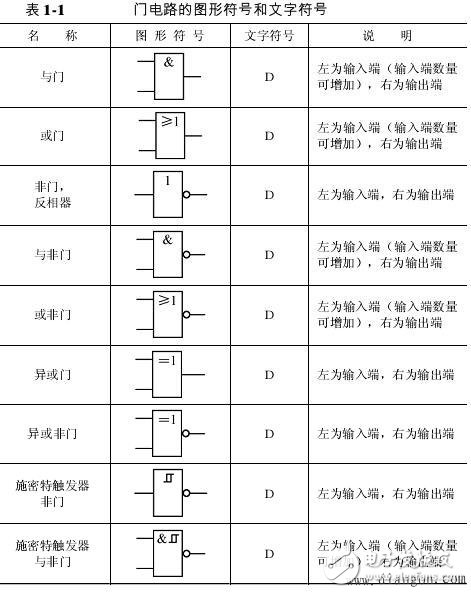

三态门逻辑符号:

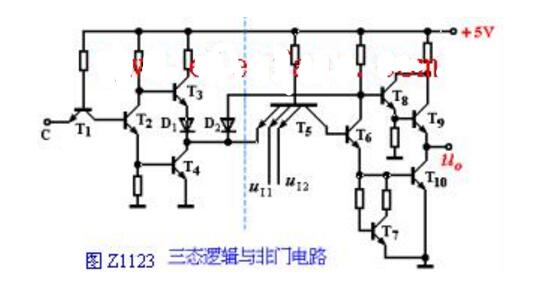

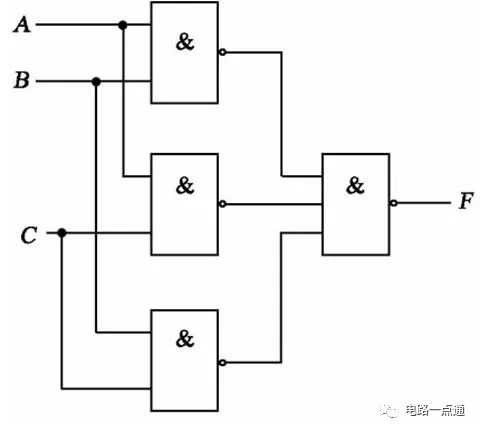

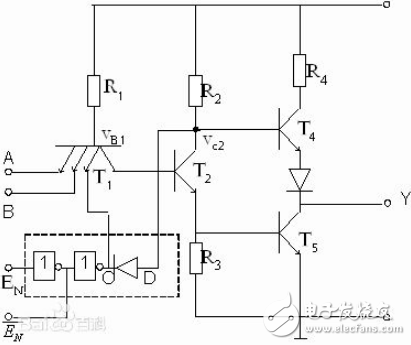

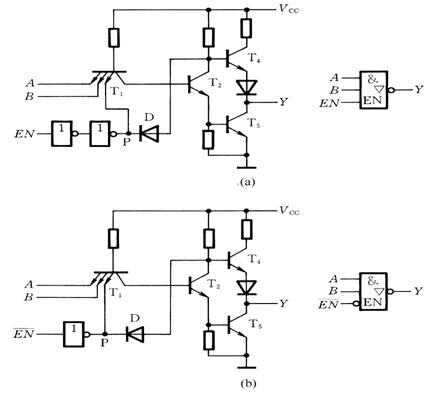

三态门逻辑电路图一:

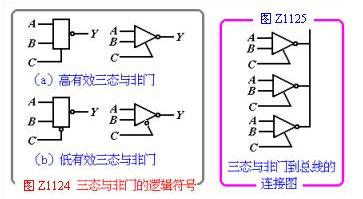

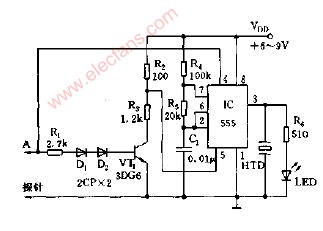

三态逻辑与非门如图Z1123所示。这个电路实际上是由两个与非门加上一个二极管D2组成。虚线右半部分是一个带有源泄放电路的与非门,称为数据传输部分,T5管的uI1、uI2称为数据输入端。而虚线左半部分是状态控制部分,它是个非门,它的输入端C称为控制端,或称许可输入端、使能端。

当C端接低电平时,T4输出一个高电平给T5,使虚线右半部分处于工作状态,这样,电路将按与非关系把uI1,uI2接受到的信号传送到输出端,使uo或为高电平,或为低电平。

当C端接高电平时,T4输出低电平给T5,使T6、T7、T10截止。另一方面,通过D2把T8的基极电位钳在1v左右,使T9截止。由于T9、T10均截止,从输出端u0看进去,电路处于高阻状态。

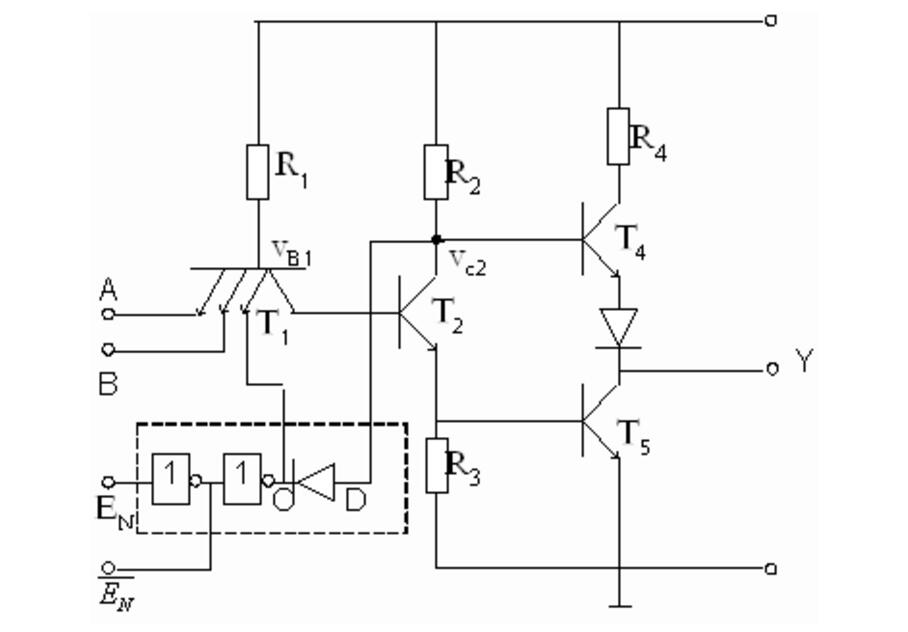

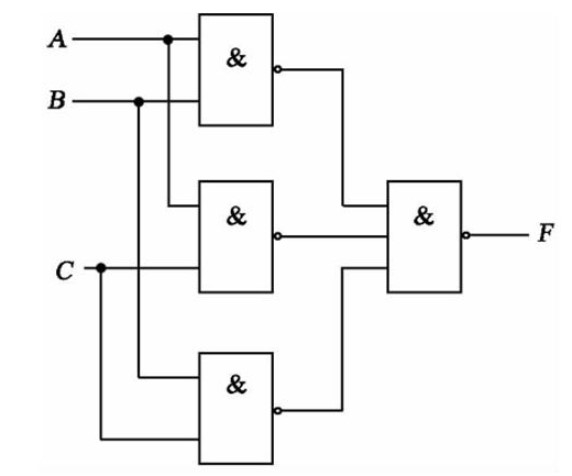

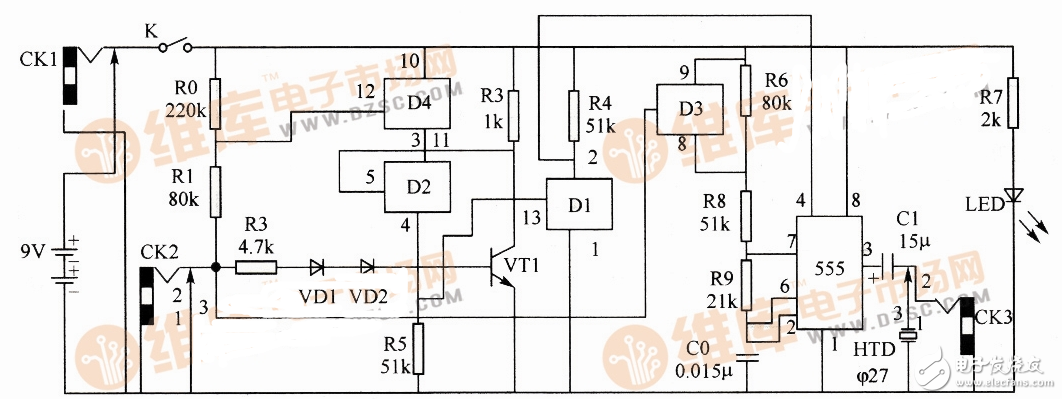

三态门逻辑电路图二:

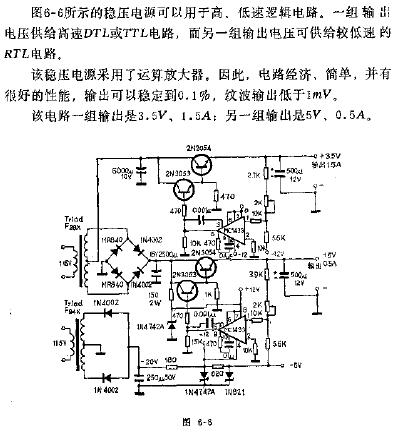

在图中,如果将虚线方框内的两个反相器和一个二极管剪掉,剩下的部分就是典型的TTL与非门电路。

所谓三态是指输出端而言。普通的TTL与非门其输出极的两个晶体管T4、T5始终保持一个导通,另一个截止的推拉状态。T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(vcc)阻抗无穷大。因此这第三种状态也称高阻状态。

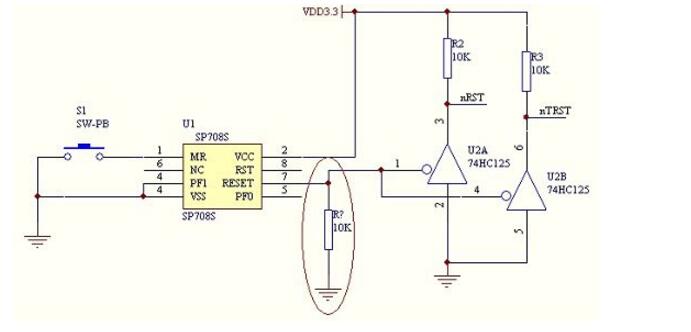

三态门逻辑电路图三:

该系统复位电路采用手动复位方式,采用一个复位芯片SP708S、一个按键、三个10KΩ电阻和两个三态门实现复位电路,通过RESET引脚和TRST引脚分别实现对ARM外围电路的复位和JTAG复位,采用复位芯片SP708S和三态门可提高复位信号的稳定性。ARM处理器的复位信号是低电平有效,R2、R3分别是两个上拉电阻,当系统没有复位时保持高电平;一旦按键按下SP708S芯片的RESET端输出低电平信号,两个三态门分别有效,而三态门的输入端接地,因此输出端输出低电平信号使系统实现复位功能。但是根据实际的工程项目测试该复位电路一直处于复位状态。

电子发烧友App

电子发烧友App

评论