控制门电路的通断。 可以具备这三种状态的器件就叫做三态(门,总线,......).举例来说:内存里面的一个存储单元,读写控制线处于低电位时,存储单元被打开,可以向里面写入;当处于高电位时,可以读出,但是

2008-05-26 13:01:37

三态输出的缓冲器有哪些用途? 三态输出缓冲器是一种电子元件,其主要作用是将一个输入信号转换成一个可以控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信

2023-09-21 15:55:36 389

389 本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF) 的 HDIO 输出缓冲器的上电电压为 3.3 V 或 2.5 V 并且 Data(数据)控制信号与 Tristate(三态)控制信号的切换时间彼此相近,则可能会受到三态数据争用条件的影响。

2023-07-12 09:50:32 213

213

八进制透明锁存器(三态);八进制 D 触发器(三态)-74F373_374

2023-03-03 20:05:16 0

0 16 位注册驱动器,具有反向寄存器启用和动态控制输出;三态-74AVC16334A

2023-02-21 18:51:10 0

0 18 位注册驱动器,具有反向寄存器启用和动态控制输出;三态-74AVC16834A

2023-02-21 18:50:57 0

0 具有动态控制输出的 18 位注册驱动程序;三态-74AVC16835A

2023-02-21 18:40:05 0

0 具有反向寄存器使能和动态控制输出的 20 位寄存驱动程序;三态-74AVC16836A

2023-02-21 18:39:50 0

0 在当前计算密集的高性能系统中,动态随机存储器(DRAM)和嵌入式动态随机存取存储器(embedded-DRAM,eDRAM)是主要的动态快速读/写存储器。先进的 DRAM 存储单元有两种,即深沟

2023-02-08 10:14:57 3874

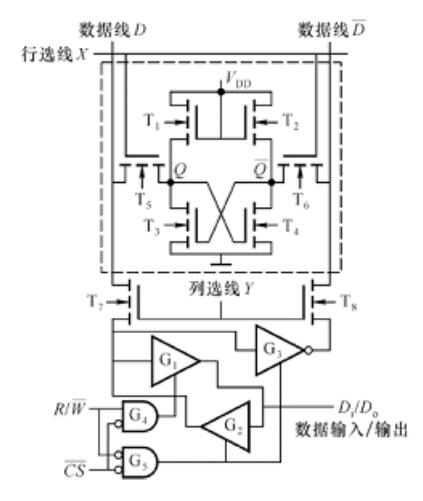

3874 在芯片设计时,通常需要用到各种类型的存储单元,用以临时或者永久地存储数据。根据应用场合的不同,所用到的存储单元也不同。本文对常见的几个存储单元进行了介绍,并简述了其工作原理和特点。需要特别

2022-12-02 17:36:24 1465

1465

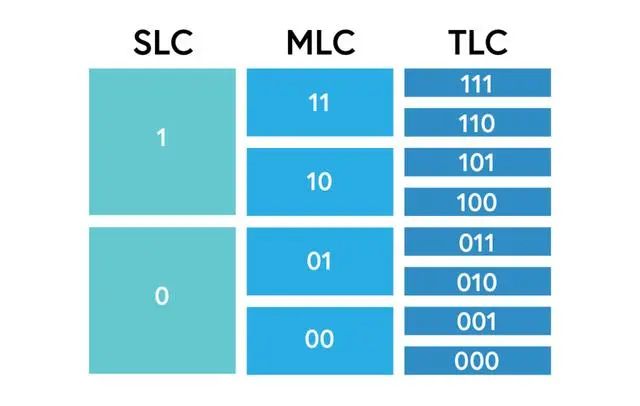

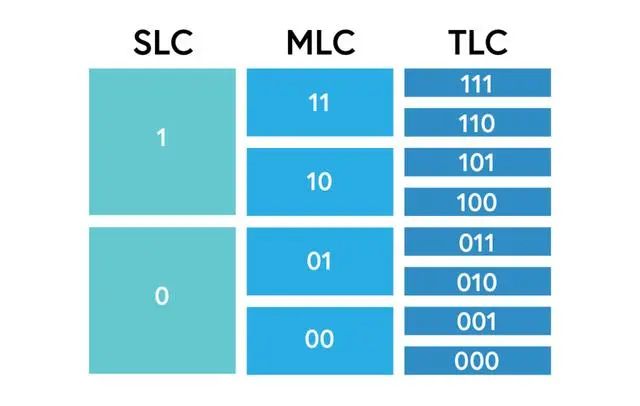

就基本的 SSD 存储单元而言,有 SLC、MLC、TLC 和 QLC。其中,TLC 是最受欢迎的,不过,QLC 最终将取代它们。在 I/O 方面,有 SATA 和 NVMe。

2022-08-26 16:41:35 2959

2959

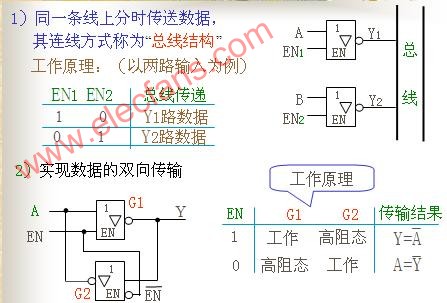

闪速存储器(Flash Memory)又称闪存(Flash),是一种非易失性存储器,用存储单元阈值的高低表示数据。浮栅(Floating Gate )场效应管(见图5-80)是Flash存储单元采用的主要技术。

2022-08-08 15:46:00 802

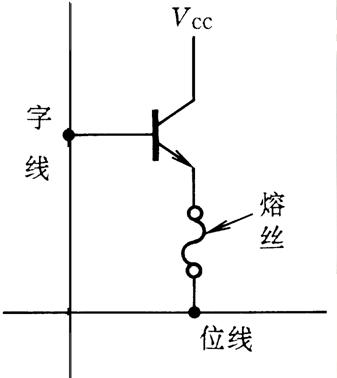

802 三态输出门电路的输出端除了出现高、低电平外,还会出现第三种状态——高阻态,所以叫做三态输出门电路。 三态门的工作原理: 当控制端a为“1”时,b型管3导通,同时a端电平通过反向器成为低电平,让

2021-08-12 11:39:49 10760

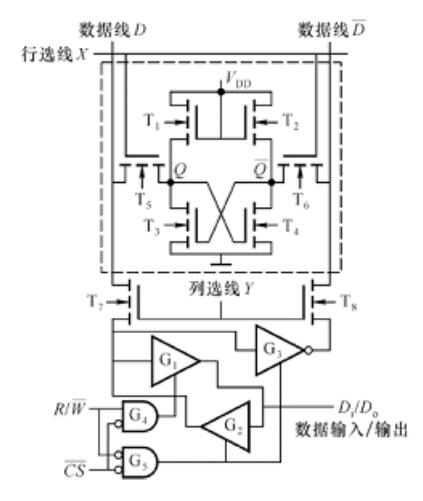

10760 数据必须首先在计算机内被表示,然后才能被计算机处理。计算机表示数据的部件主要是存储设备;而存储数据的具体单位是存储单元;因此,了解存储单元的结构是十分必要的。

2021-01-08 10:03:55 2042

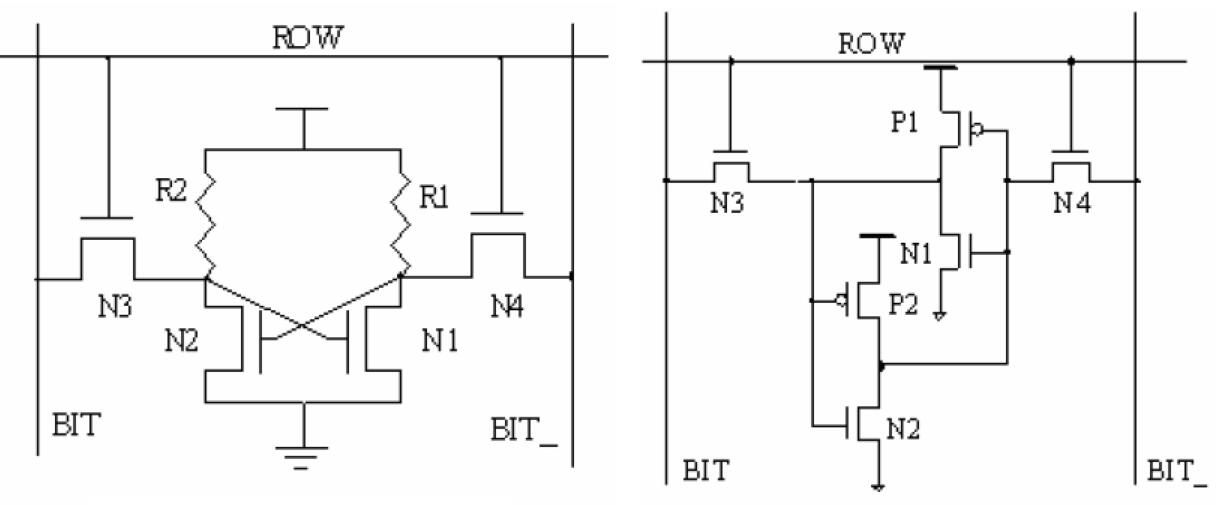

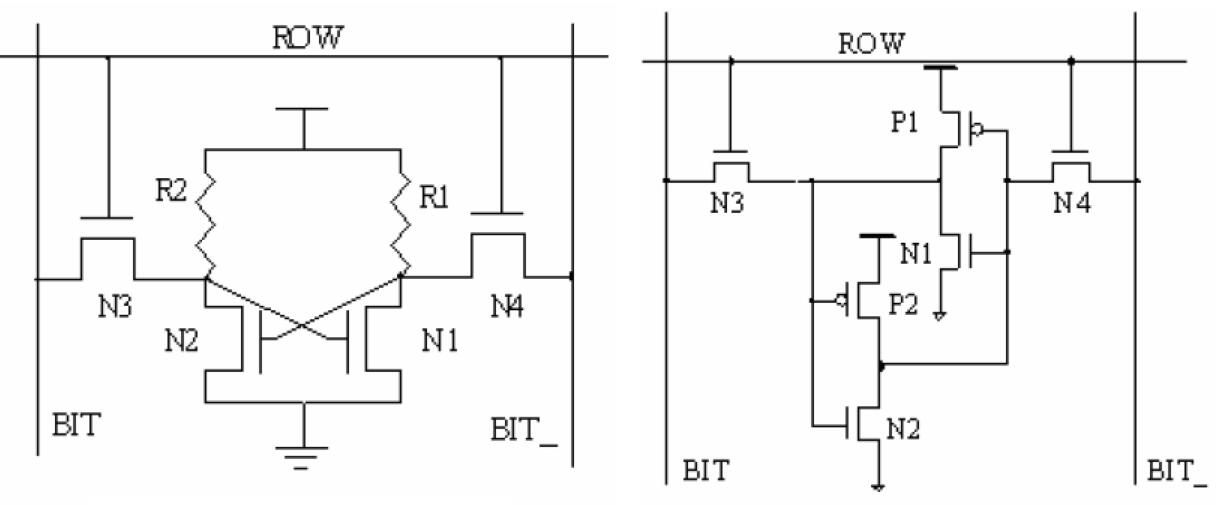

2042 按照数据存取的方式不同,ram中的存储单元分为两种:静态存储单元一静态RAM(SRAM);动态存储单元动态RAM(DRAM)。 1.静态存储单元(SRAM):它由电源来维持信息,如触发器,寄存器等

2020-12-02 14:31:30 2036

2036

本文档的主要内容详细介绍的是三态门应用的Multisim仿真实例电路图免费下载。

2020-09-23 17:32:00 38

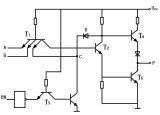

38 大学计算机教学中的计算机硬件实验。在计算机硬件实验中,三态电路有着广泛的应用,例如构建一个具有分时共享功能的总线电路就需要用到多个三态电路。

2020-08-07 17:14:32 1593

1593

1.74HC595是典型的移位串转并三态输出驱动器。2、8位并行三态输出,并且可以级联输出。3、100MHz的移位频率传输数据。4、高阻抗输入,Mos推动输出。可以兼容TTL。5、74HC595常用封装是s016和DP16。

2020-07-27 08:00:00 0

0 静态RAM的基本构造块是SRAM存储单元。通过升高字线的电平触发存储单元,再通过位线对所触发的存储单元进行读出或写入。在静态CMOS存储器中,存储单元阵列将会占去整个存储器芯片面积的一半以上,在一些

2020-05-14 09:19:47 2996

2996

常规的硬件实验测试三态总线电路逻辑功能的方法是,将三态输出门的控制端、输入端分别接逻辑电平开关,改变逻辑电平开关为逻辑1、逻辑0观测输出函数的逻辑状态。存在的问题是,总线分时传输关系不直观。用

2020-04-18 12:50:00 6304

6304 存储单元的作用:可以进行读写操作以及存放数据。

2020-03-22 17:34:00 3663

3663 三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-29 07:09:00 3339

3339 三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-21 07:05:00 7465

7465 三态电路有什么特点,什么是上拉电阻、下拉电阻以及高阻态?

2019-05-21 07:28:00 6003

6003

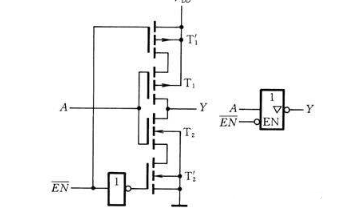

三态门亦称“三态输出门”、“三态门输出电路”。是一种重要的总线接口电路。具有高电平、低电平和高阻抗三种输出状态的门电路。

2019-03-10 09:29:25 15025

15025 三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态,那么三态门输出的三种状态是什么呢?

2019-02-21 16:45:59 66152

66152 三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

2018-10-24 16:09:36 32926

32926 本文从传统三态开关交错并联DC/DC变换器的基本结构出发,将耦合电感和二极管电容同时融合到传统的交错并联DC/DC变换器中,构造基于三态开关单元与双耦合电感的新型输入端交错并联高增益DC/DC变换器

2018-03-21 15:17:24 3

3 本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出门电路与三态门电路的图形符号与真值表。

2018-03-01 14:47:41 113066

113066

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了三款三态门逻辑电路。

2018-03-01 14:03:10 69342

69342

三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42:36 13281

13281

低电平,随它后面接的东西定。三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态(门,总线,......)。

2017-12-25 11:27:11 20313

20313

。O工P存储器的种类很多,很多是基于熔丝和反熔丝,本文介绍的O工P存储器基于反熔丝结构。在反熔丝O工P存储器中,通过对选中单元的编程改变了存储单元内部的结构。理想的读机制下,没有编程的存储单元读取时会读出0,而通过编程的存储单元在读取时会读出1。反

2017-11-07 11:45:21 11

11 PSoC 4 三态缓冲器 Bufoe

2017-10-10 08:39:49 13

13 三态门在数字电路上可以说是应用的非常广泛,特别是一些总线上的应用,因而,随着数字电路的发展,就避免不了用硬件描述语言在FPGA上来设计实现三态门。

2017-02-08 11:37:06 7000

7000 使用赛道存储单元的近阈值非易失SRAM_孙忆南

2017-01-07 21:45:57 1

1 应用于超低电压下的SRAM存储单元设计_刘冰燕

2017-01-07 21:39:44 0

0 三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器

2015-11-16 11:59:30 23

23 介绍了用Multisim仿真软件分析三态门工作过程的方法,目的是探索三态门工作波形的仿真实验技术,即用Multisim仿真软件中的字组产生器产生三态门的控制信号及输入信号,用Multisim中示

2011-05-06 15:59:38 76

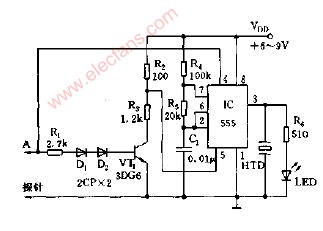

76 图中所示用555时基电路集成三态声光逻辑笔电路.555时基集成电路接成多谐振荡器.

控

2010-10-03 16:56:03 1204

1204 本文就三态电路在FPGA中的应用作了详细的说明。文章首先描述了一个调用lpm中三态电路模块的VHDL程序,这个程序会出现编译不能通过的问题。然后从这个问题出发,通过尝试三态电

2010-08-06 16:56:22 27

27 对第一代开关电流存储单元产生的时钟馈通误差做了合理的近似分析,设计了一种高性能开关电流存储单元。该电路仅在原存储单元的基础上增加了一个MOS管,使误差降为原来的4%,

2010-07-05 14:50:48 22

22 具有三态输出的集成电路其输出具有可控的高阻抗状态,广泛应用于总线结构中。凡是输出连接到总线的逻辑部件,例如:存储器、总线控制器、总线接口等等。无论是TTL电路,还

2010-05-05 10:15:13 16

16 三态门的组成及工作原理

2010-02-28 19:13:26 23595

23595

单管动态MOS存储单元

2009-12-04 16:50:24 3661

3661 四管动态MOS存储单元

2009-12-04 16:34:14 2189

2189 六管NMOS静态存储单元

2009-12-04 15:30:03 6393

6393 E2PROM存储单元的三种工作状态

2009-12-04 13:04:45 1265

1265 E2PROM的存储单元

2009-12-04 13:03:57 1418

1418 使用FAMOS管的存储单元

2009-12-04 12:27:29 823

823

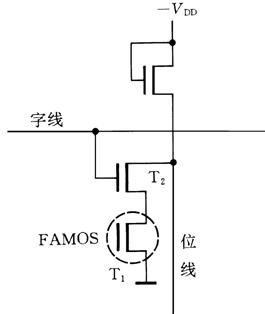

熔丝型PROM的存储单元

2009-12-04 12:25:26 2114

2114

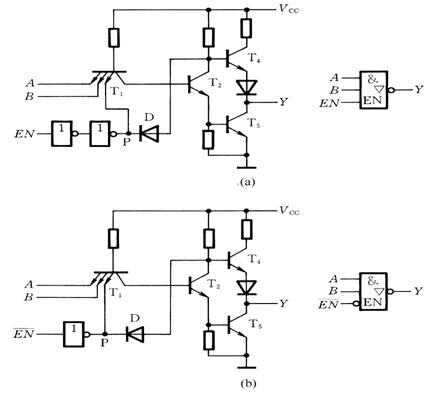

CMOS三态门电路结构

(a)用或非门控制 (b)用与非门控制

2009-07-15 19:09:10 10707

10707

三态输出门的电路图和图形符号

2009-07-15 19:03:57 2698

2698

五用途三态声频逻辑比电路图

2009-05-19 13:45:31 309

309

三态声光逻辑笔电路图

2009-05-19 13:42:17 652

652

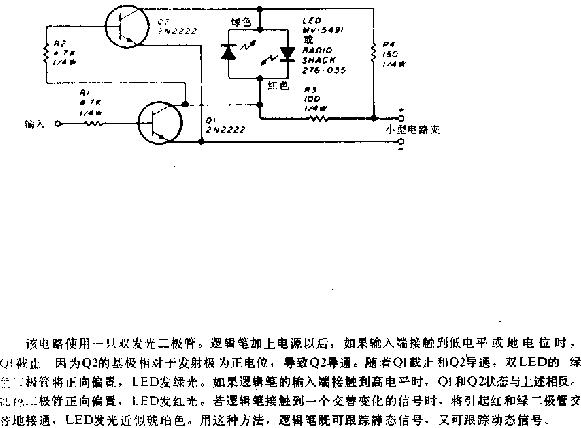

三态逻辑笔电路图

2009-04-07 09:16:34 1514

1514

TTL或非门、集电极开路门和三态门电路

1.TTL或非门

下图为TTL或非门的逻辑电路及其代表符号。

2009-04-07 00:11:59 13667

13667

如何处理内部三态电路—PLD设计技巧 Tri-State vsMUX

Tri-State Buffer

There are two application area

2008-09-11 09:27:21 29

29 什么是三态门?

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。

2008-05-26 12:48:24 41856

41856

低电压甲乙类开关电流存储单元

引言 开关电流存储单元是电流模式采样数据信号处理系统的基本单元电路,其性能的优

2007-08-15 16:06:29 532

532

电子发烧友App

电子发烧友App

硬声App

硬声App

389

389 213

213

0

0 0

0 0

0 3874

3874 1465

1465

2959

2959

802

802 10760

10760 2042

2042 2036

2036

1593

1593

0

0 2996

2996

6304

6304 3339

3339 7465

7465 66152

66152 32926

32926 3

3 113066

113066

69342

69342

20313

20313

11

11 7000

7000 76

76 27

27 22

22 16

16 29

29 41856

41856

评论