三态电路有什么特点,什么是上拉电阻、下拉电阻以及高阻态?

2019-05-21 07:28:00 7701

7701

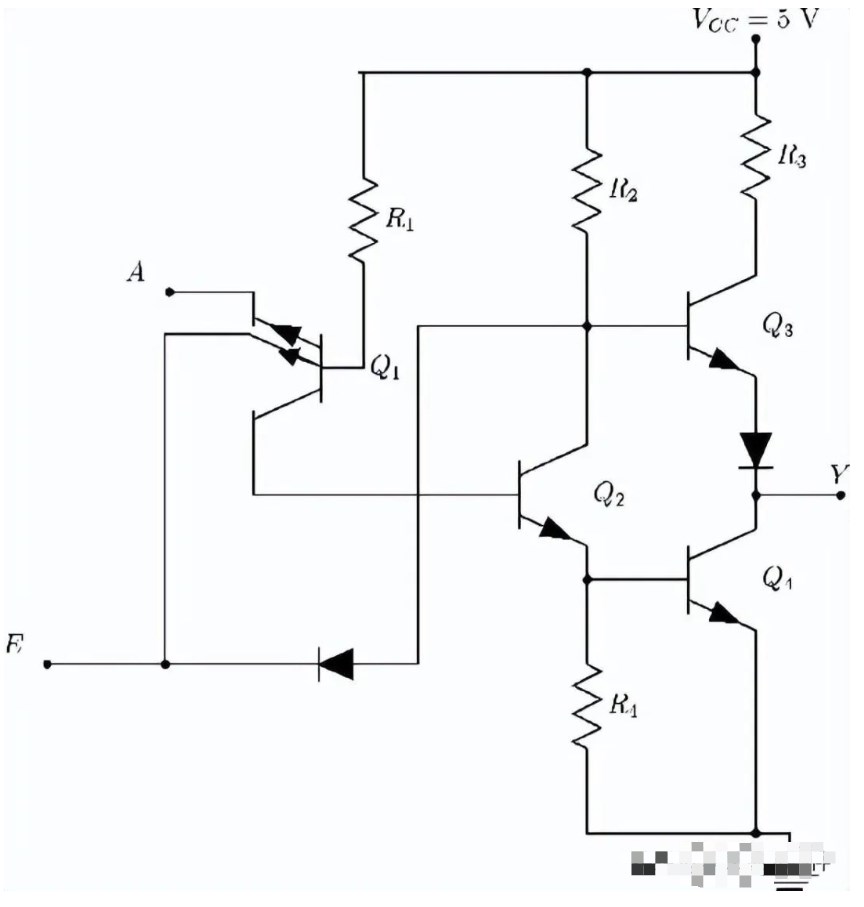

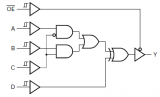

TTL三态门输出电路是一种重要的接口元件,它能够提供三种输出状态:高电平、低电平和高阻态。这种电路在实现数字系统之间的连接和数据传输时起着至关重要的作用。

2024-02-18 15:41:19 6464

6464

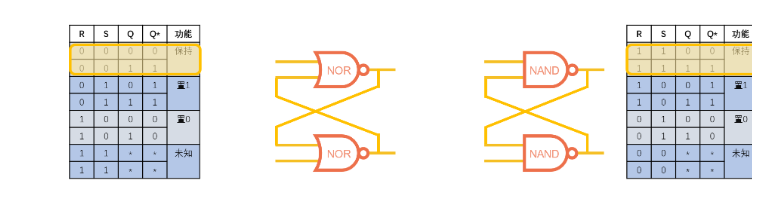

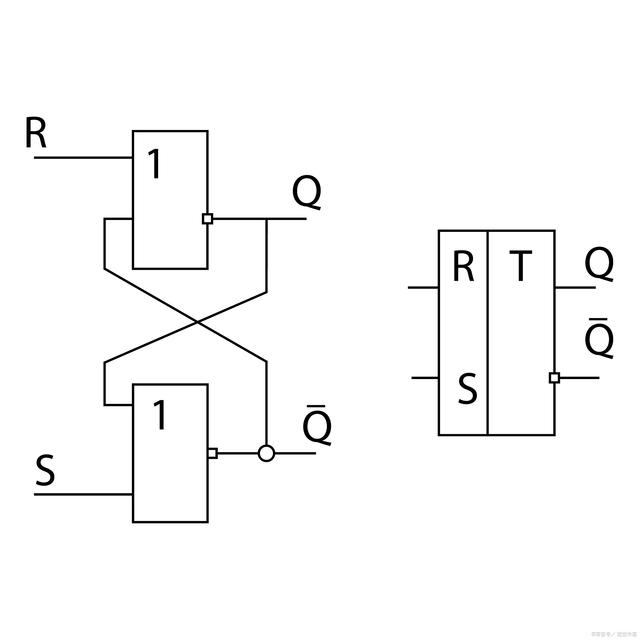

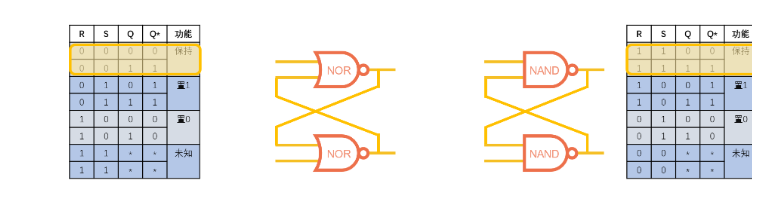

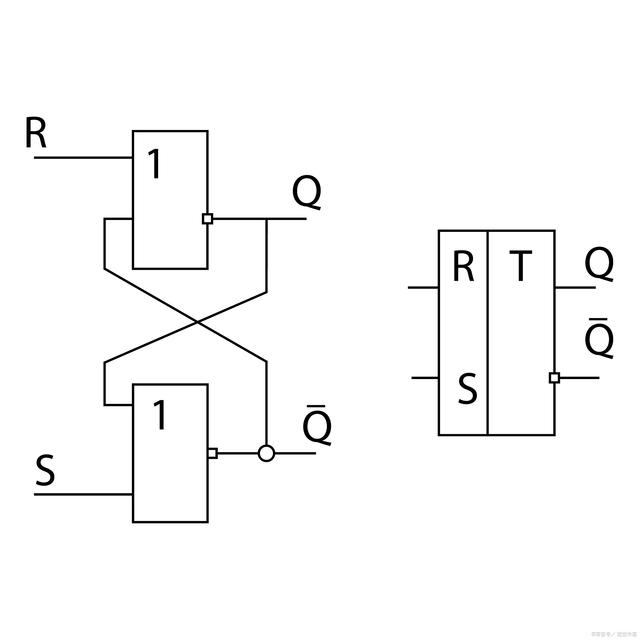

基本的RS触发器是一种使用与非门和或非门构成的存储器元件,它可以存储一个比特的信息并在触发信号的控制下改变状态。与非门和或非门则是用于逻辑运算的基本门电路,它们执行逻辑“与”和“或”运算并输出相应的结果。

2024-03-01 17:22:21 11972

11972

一、三态单片机IO的三态是指:高电平(1)、低电平(0)、高组态(Z)。二、高阻态高阻i是一种电路状态.既不是高电平,也不是低电平,以高阻态对下级电路输出,下级电路什么影响也没有.高阻态的IO电平

2021-11-25 06:42:28

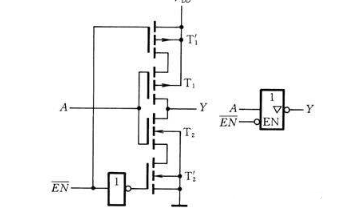

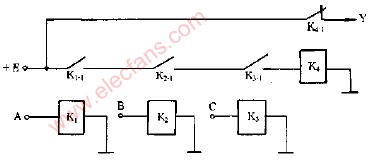

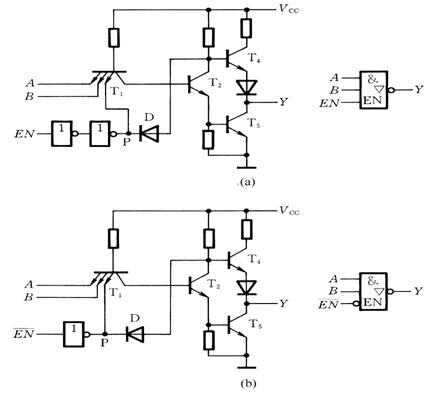

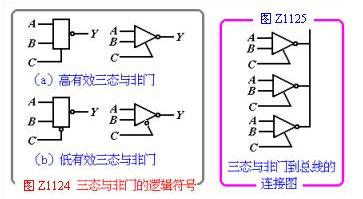

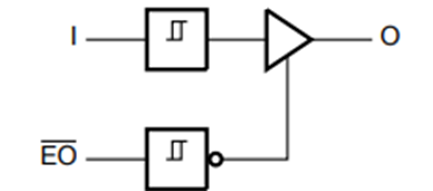

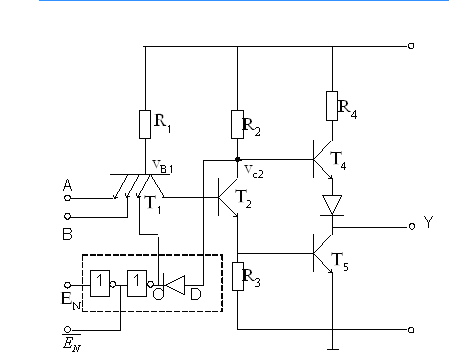

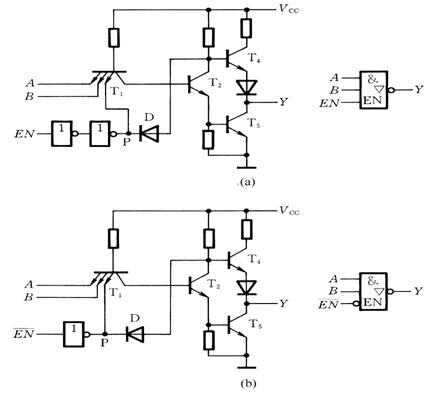

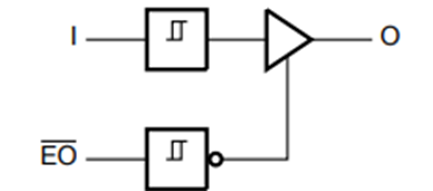

三态输出门的电路图和图形符号

2019-10-25 07:17:31

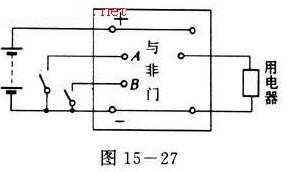

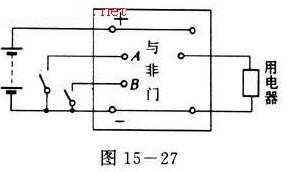

与非门电路怎样构成自锁电路?急急急

2011-12-09 14:03:52

逻辑门电路电子教案 逻辑门电路:用以实现基本和常用逻辑运算的电子电路。简称门电路。 基本和常用门电路有与门、或门、非门(反相器)、与非门、或非门、与或非门和异或门等。 逻辑0和1: 电子电路

2009-09-16 16:10:39

逻辑门及组合逻辑电路实验实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法。4.

2008-09-25 17:28:34

“门”电路是什么?是门里的电路吗? 并不是哦,门电路是一种逻辑关系电路,用来实现基本的逻辑运算和符合逻辑元素的单元电路。所以像平时听见的与门,或门,非门,与非门,异或门都是门电路。 (图

2023-04-13 17:44:29

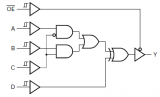

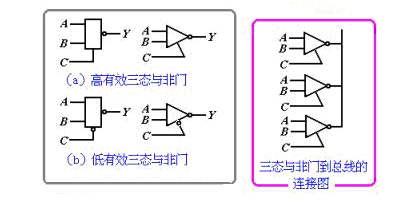

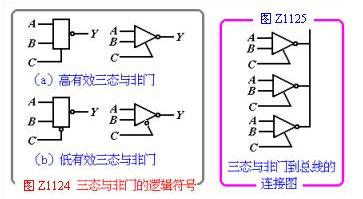

截止。所以从输出端看进去电路处于高阻状态即禁止状态。这种电路是当E为高电平时实现与非功能,故称为高电平有效三态门。还有一种三态输出与非门电路,将控制信号经一非门反相后再送到与非门的VT1的控制输入端

2009-10-20 09:50:53

时实现与非功能,故称为高电平有效三态门。还有一种三态输出与非门电路,将控制信号经一非门反相后再送到与非门的VT1的控制输入端。显然,当E=0时,电路实现与非功能,有两种状态;而当E=1时,电路处于高阻

2009-10-20 09:51:51

使用CMOS门电路时输入端特别注意不能悬空。在使用时应采用以下方法: 1、与门和与非门电路:由于与门电路的逻辑功能是输入信号只要有低电平,输出信号就为低电平,只有全部为高电平时,输出端才为高电平

2018-12-03 10:49:35

使用CMOS门电路时输入端特别注意不能悬空。在使用时应采用以下方法: 1、与门和与非门电路:由于与门电路的逻辑功能是输入信号只要有低电平,输出信号就为低电平,只有全部为高电平时,输出端才为高电平。而与非门电路

2018-08-30 11:18:22

1.6TTL输出管集电极开路门(OC门) 1.7TTL与非门构成的三态逻辑门(TSL门)2有关集成触发器——TTL与非门构成的触发器 2.1D型前沿触发器由四管单元TTL与非门2个+二管单元TTL与非门

2018-08-24 16:30:23

TTL集成与非门电路中不用的输入端如何处理呢?

2023-04-28 10:52:05

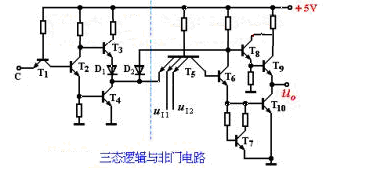

,还能作线与联接,人们又开发了一种三态与非门,它的输出除了具有一般与非门的两种状态,即输出电阻较小的高、低电平状态外,还具有高输出电阻的第三状态,称为高阻态,又称为禁止态。 一个简单的TSL门的电路

2012-01-11 00:34:11

门电路的封装图,图(b)为其内部结构图。六、TTL或非门、集电极开路门和三态门电路1.TTL或非门 下图为TTL或非门的逻辑电路及其代表符号。 由图可见 ,或非逻辑功能是对TTL与非门的结构改进

2009-04-07 00:01:07

”门来形成AND,OR和NOT功能的三种基本门类型。仅使用NAND门的各种逻辑门以及上面的三种常见类型,异或,异NOR和标准NOR可以仅使用单独的可形成栅极NAND栅极。常用的数字逻辑与非门IC包括

2021-01-22 08:00:00

门电路是数字电路中最基本的逻辑单元。它可以使输出信号与输入信号之间产生一定的逻辑关系。在数字电路中,信号大都是用电位(电平)高低两种状态表示,利用门电路的逻辑关系可以实现对信号的转换。最基本的门电路

2021-07-05 06:10:52

三态门和OC门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。因此,需要一种新的与非门电路来实现线与逻辑,这种门电路

2008-05-26 13:01:37

晶振的高阻态在电路起什么作用,为什么有的晶振需要三态脚有的不需要,晶振的三态是靠什么去控制的?

2025-05-15 11:08:06

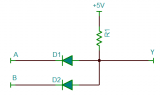

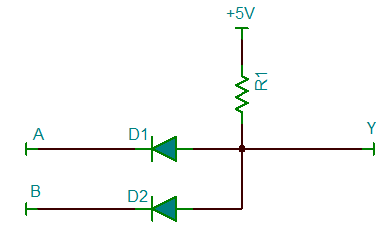

以上基本的与、或、非门,可以实现与、或、非三种逻辑运算。但是由于它们的输出电阻比较大,带负载的能力差,开关性能也不理想,因此基本的与、或、非门不具有实用性。解决的办法之一是采用二极管与三极管门的组合,组成

2009-04-06 23:59:45

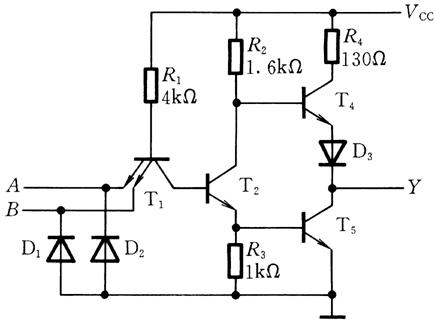

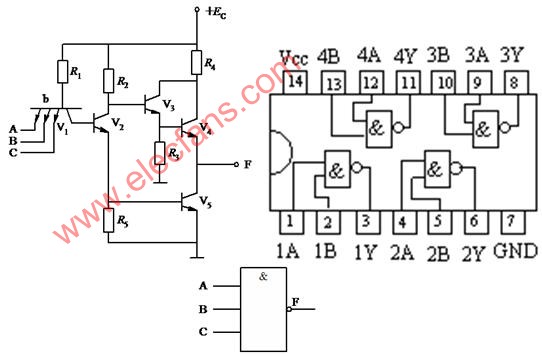

逻辑门电路是以简单的分立元器件组成而成,这里我们以一个简单的逻辑与非门电路74HC01为例讲解下创建方法,74HC01的逻辑电路图如图2-16所示,是由4个一样的逻辑与非门电路组合而成

2020-09-07 17:40:36

如何测量与非门电路的时延参数呢?

2023-04-28 10:46:54

嵌入式硬件(三)数字逻辑电路一、组合逻辑电路1.非门2.与门3.与非门4.或门5.或非门6.异或门7.三态门二、时序逻辑电路1.触发器(flip-flop)(1)RS触发器(2)D触发器2.锁存器

2021-07-26 08:02:44

反相器的速度与哪些因素有关?什么是转换时间和传播延迟呢?怎样去设计一种CMOS三态缓冲器的电路呢?

2021-10-20 06:24:39

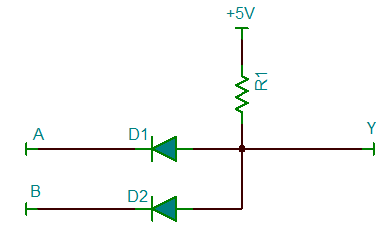

有时候我们搭电路时只需要实现一个简单的逻辑,但用一个4门的集成电路来设计未免过于昂贵与占面积,而且IC里没用到的门电路又必须拉高或拉低,相当烦琐。鉴于简化电路的需要我整理了一套用三极管、二极管、电阻

2019-09-19 16:24:52

组成的逻辑门电路,可实现2输入或3输入的AND,OR,NAND,NOR,EXOR操作。与非门或非门或门与门异或门三输入与非门三输入或非门三输入与门三输入或门

2018-10-11 17:44:32

集成逻辑电路、组合逻辑电路实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法

2008-12-11 23:36:32

常用表示方法:高阻态常用字母 Z 表示三态门图1 三态门逻辑符号 三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。三态

2019-01-08 11:03:07

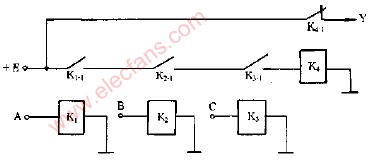

顺序脉冲发生器、 三态逻辑和微机总线接口5.4.1 顺序脉冲发生器顺序脉冲分类计数型

2008-05-27 11:29:27 28

28 实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实

2010-08-18 14:50:44 0

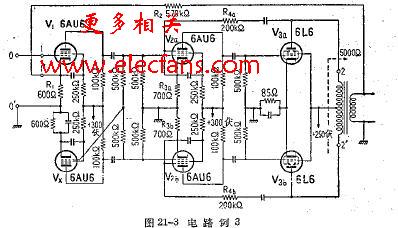

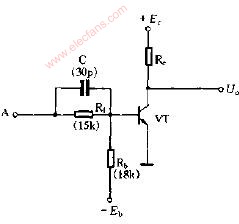

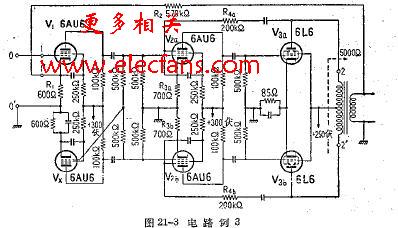

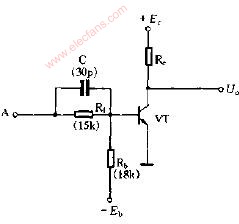

0 推挽放大电路图三例

2007-11-25 12:09:35 2846

2846

什么是三态门?

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。

2008-05-26 12:48:24 49852

49852

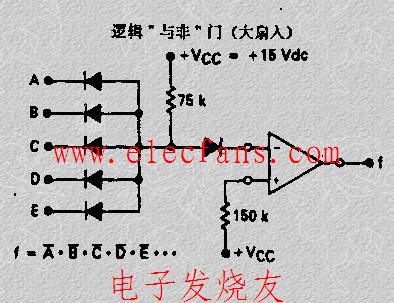

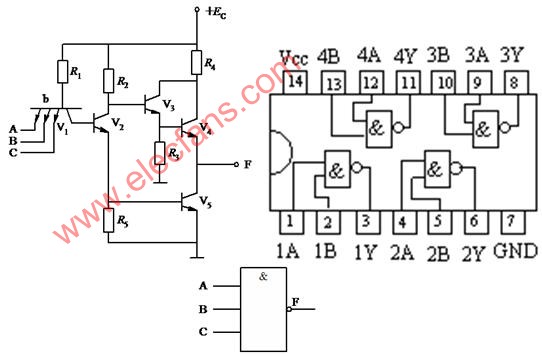

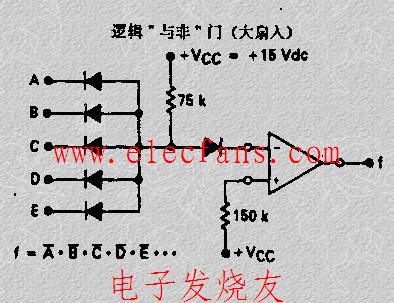

逻辑与非门

2008-06-12 23:24:21 2017

2017

第七讲 TTL集成逻辑门电路

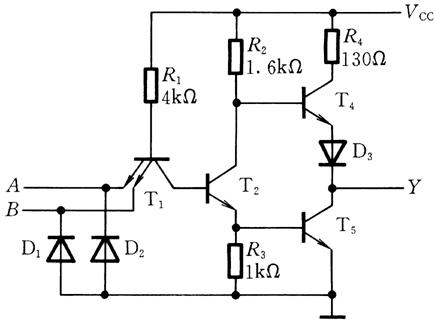

3 . 3 TTL集成逻辑门电路3 . 3 . 1 TTL与非门一、TTL与非门的工作原理1.电路结构2.工作原理

2009-03-30 16:05:37 7041

7041

3.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理2.OC门的应用二、与或非门三、三态输出门(TSL门)1.三态输出门

2009-03-30 16:14:25 2921

2921

3.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理2.OC门的应用二、与或非门三、三态输出门(TSL门)1.三态输出门

2009-03-30 16:15:14 2656

2656

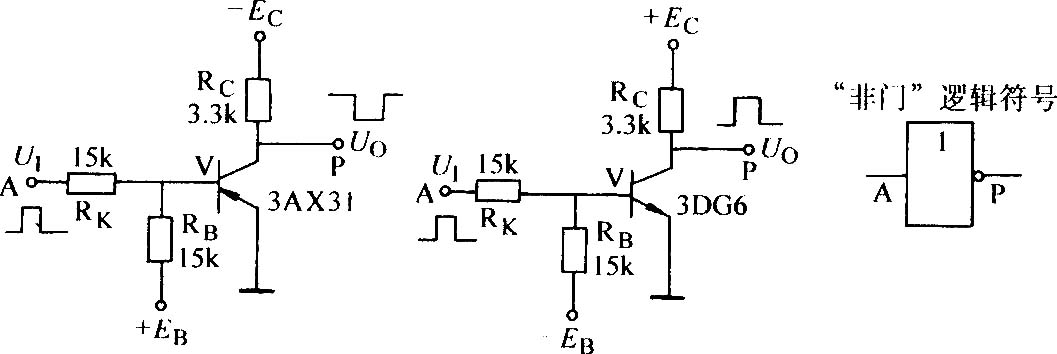

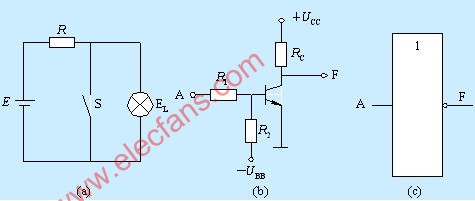

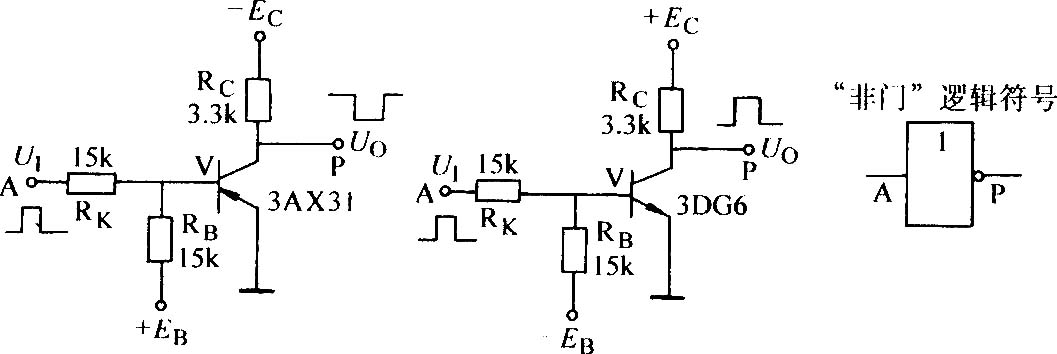

非门电路图

2009-04-05 09:41:07 4194

4194

与非门电路图

2009-04-06 23:12:46 10460

10460

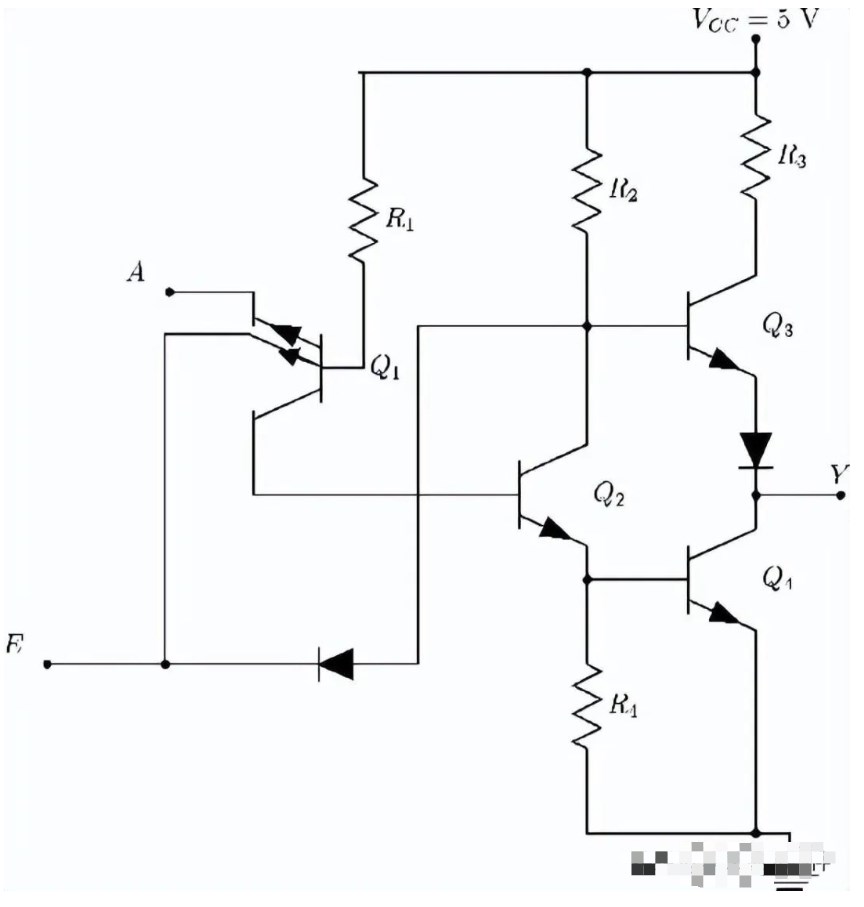

与非门电路原理

(1)电路结构及工作原理 TTL与非门是TTL逻辑门的基本形式,典型的TTL与非门电路结构如图8-16所示。该电路由

2009-04-06 23:14:15 20333

20333

与非门电路介绍图15-26甲是我们实验用的与非门,它也有两个输入瑞A、B,图乙是它在电路中的接法。

2009-04-06 23:17:48 18020

18020

或非门电路图

或非门的逻辑符号及波形图如图8-14所示。

(a) 逻辑符号 &n

2009-04-06 23:23:04 25905

25905

TTL与非门电路

基本TTL反相器不难改变成为多输入端的与非门 。它的主要特点是在电路的输入端采用了多发射极的BJT ,如下图所示。器件中的每一个发射

2009-04-07 00:11:11 13376

13376

TTL或非门、集电极开路门和三态门电路

1.TTL或非门

下图为TTL或非门的逻辑电路及其代表符号。

2009-04-07 00:11:59 17424

17424

三态与非门(TSL)

利用OC门虽然可以实现线与的功能,但外接电阻Rp的选择要受到一定的限制而不能取得太小,因此影响了工作速度。

2009-04-07 00:15:37 10530

10530

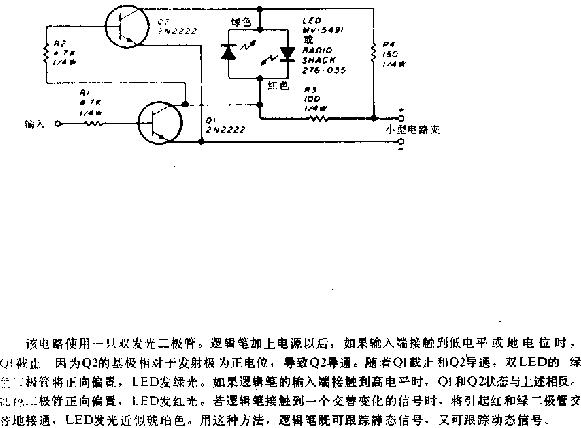

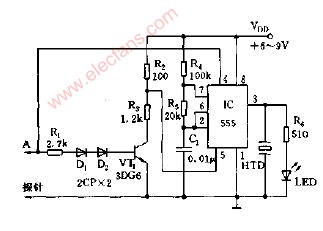

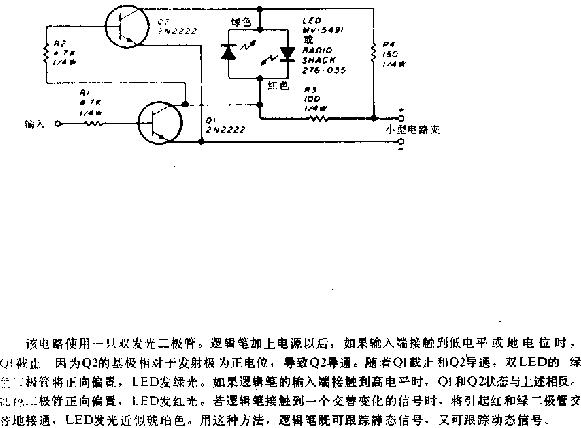

三态逻辑笔电路图

2009-04-07 09:16:34 2408

2408

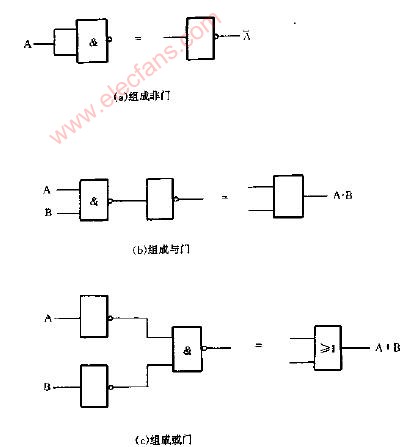

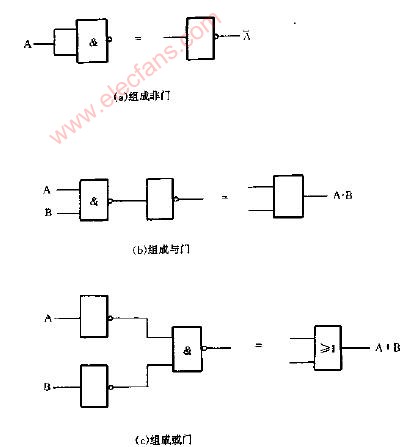

利用与非门组成的一些门电路图

2009-05-08 14:35:10 20348

20348

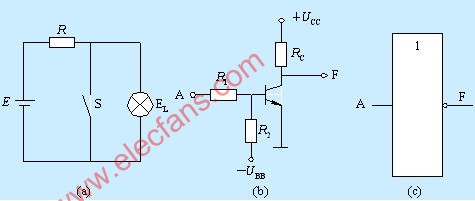

三极管非门电路图

2009-05-08 14:37:14 8031

8031

继电器与非门电路图

2009-05-08 15:35:18 2483

2483

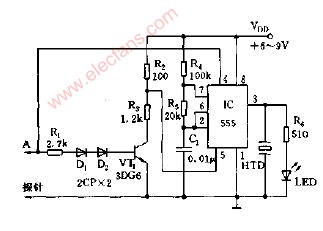

三态声光逻辑笔电路图

2009-05-19 13:42:17 885

885

五用途三态声频逻辑比电路图

2009-05-19 13:45:31 678

678

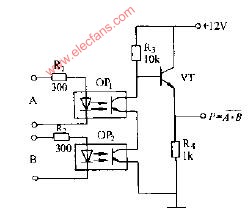

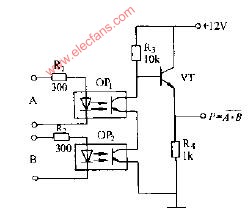

光耦合器构成的与非门电路图

2009-06-04 16:25:53 5960

5960

TTL与非门电路

2009-07-15 18:55:34 3706

3706

三态输出门的电路图和图形符号

2009-07-15 19:03:57 3527

3527

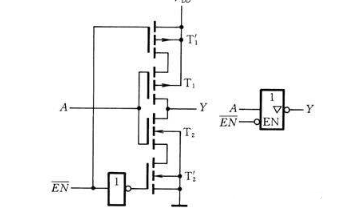

CMOS三态门电路结构

(a)用或非门控制 (b)用与非门控制

2009-07-15 19:09:10 13373

13373

非逻辑及非门电路

非逻辑:逻辑表达式为F= 。

2009-09-24 10:21:46 5215

5215

TTL集成与非门电路

TTL与非门芯

2009-09-24 10:25:42 3712

3712

与非门,与非门是什么意思

DTL与非门电路:

常将二极管与门和或门与三极管非门组合起来组成与非门和或非门电路,以消除在串接时产生的电

2010-03-08 11:41:15 12493

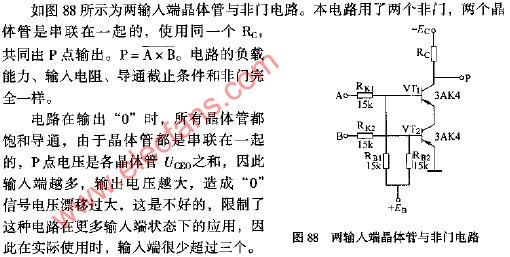

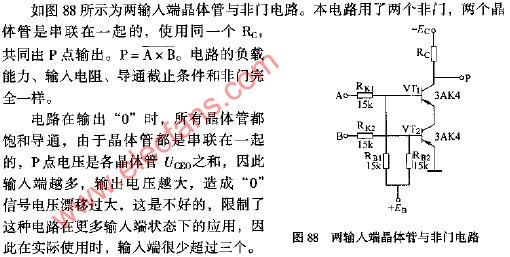

12493 两输入端晶体管与非门电路图

2010-03-29 17:03:19 5168

5168

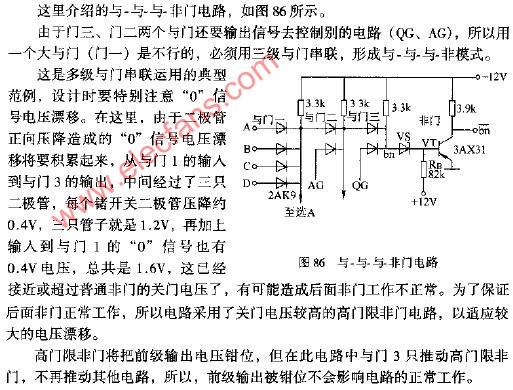

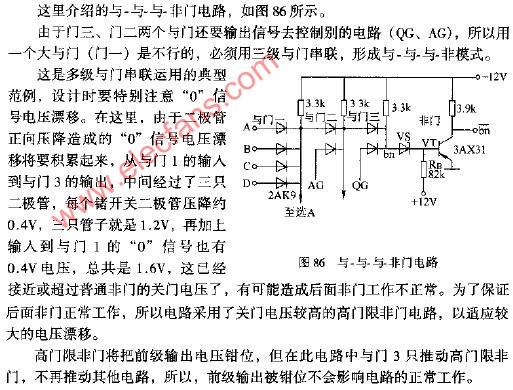

与-与-与-非门电路图

2010-03-29 18:06:09 2191

2191

三态门:计算机的逻辑部件

常用的集成门电路器件分为两大类:CMOS和TTL。 CMOS是由单极型场效应三极管组成集成电路, TTL是晶体管-晶体管逻辑电路

2010-04-15 14:55:00 2161

2161 图中所示用555时基电路集成三态声光逻辑笔电路.555时基集成电路接成多谐振荡器.

控

2010-10-03 16:56:03 1711

1711 实验三 集电极开路门电路及三态门电路的研究 一、实验目的 1、熟悉集电极开路OC门及三态TS门的逻辑功能和使用方法 2、掌握三态门构成总线的特点及方法 3、掌握集电极负载电阻RL对

2012-07-16 23:03:30 37

37 内容提要: 本章系统地介绍数字电路的基本逻辑单元门电路,及其对应的逻辑运算与图形描述符号,并针对实际应用介绍了三态逻辑门和集电极开路输出门,最后简要介绍TTL集成门和CMOS集成门的逻辑功能、外特性

2017-10-26 17:27:59 9

9 与非门的输出端接在同一格导线上,将这些与非门上的数据(状态)用同一条导线输送出去。因此,需要一种新的与非门电路来实现线与逻辑,这各门电中就是集电极开路与非门电路,简称OC门(open collector)。OC门电路及逻辑符号见图

2017-11-09 15:55:15 66371

66371

为满足实际应用中实现线与的要求,专门生产了一种可以进行线与的门电路一一集电极开路门电路,简称OC门。OC与非门电路如图2所示。与普通TTL与非门电路相比,去掉了图2 所示TTL与非门电路的、中的三极管T4和二极管D,使输出端三极管T3的集电极开路,故称为集电极开路门电路。

2017-11-09 16:21:24 26032

26032

低电平,随它后面接的东西定。三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态(门,总线,......)。

2017-12-25 11:27:11 27795

27795

三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42:36 16307

16307

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了三款三态门逻辑电路。

2018-03-01 14:03:10 81602

81602

本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出门电路与三态门电路的图形符号与真值表。

2018-03-01 14:47:41 131514

131514

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。

2018-07-26 10:53:43 45501

45501

三态逻辑电平笔,Logic probe

关键字:三态逻辑电平笔

在脉冲电路的制作中,经常需要检测各门电路的输入、输出状态。三态逻辑

2018-09-20 19:18:55 2291

2291 三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

2018-10-24 16:09:36 35791

35791 本文档的主要内容详细介绍的是两个与非门电路的介绍 与非门(英语:NAND gate)是数字电路的一种基本逻辑电路。若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1)。与非门可以看作是与门和非门的叠加。

2019-01-09 08:00:00 18

18 三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态,那么三态门输出的三种状态是什么呢?

2019-02-21 16:45:59 73743

73743 三态门亦称“三态输出门”、“三态门输出电路”。是一种重要的总线接口电路。具有高电平、低电平和高阻抗三种输出状态的门电路。

2019-03-10 09:29:25 19309

19309 三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-29 07:09:00 5188

5188 三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-21 07:05:00 9571

9571 用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。常用的门电路在逻辑功能上有与门、或门、非门、与非门、或非门、与或非门、异或门等几种。

2019-08-15 15:42:44 16481

16481 在学电子电路中,要学会分析电路,就从了解电路的三种状态开始。电路有哪三种状态:通路(负载)、短路、开路(空载)三种状态下的电源电压分别是U=E-IR,U=0。U=E,以下内容分别介绍这三种状态的具体情况。

2019-09-13 09:54:00 102834

102834 门电路(数字电路)与模拟电路(也叫线性电路)工作时最大的区别就是:门电路的输入输出信号一般只有两种状态(少数情况还有一种三态逻辑电路)不是高电平就是低电平(数字电路中1代表高电平0代表低电平),而模拟电路的输入输出则是连续而复杂变化的电信号。

2019-09-19 11:06:28 26102

26102 常见的晶体管有二极管、三极管和MOS管,主要的逻辑门电路:与门、或门、非门、与非门、或非门、异或门等,这篇文章介绍用晶体管搭建常见的逻辑门电路。

2020-11-01 11:03:30 17072

17072

三态输出门电路的输出端除了出现高、低电平外,还会出现第三种状态——高阻态,所以叫做三态输出门电路。 三态门的工作原理: 当控制端a为“1”时,b型管3导通,同时a端电平通过反向器成为低电平,让

2021-08-12 11:39:49 14601

14601 常见的晶体管有二极管、三极管和MOS管,主要的逻辑门电路:与门、或门、非门、与非门、或非门、异或门等,这篇文章介绍用晶体管搭建常见的逻辑门电路。

2023-04-26 14:51:33 14398

14398

与非门(NAND Gate)是数字电路中的基本逻辑门之一,它实现了逻辑AND(与)操作后再进行逻辑NOT(非)操作。

2023-09-04 15:31:07 7040

7040

TTL与非门的电压传输特性 TTL与非门的静态输入与输出特性 TTL与非门的动态特性 TTL与非门是一种基本的逻辑门电路,用于将两个输入信号进行逻辑与运算,并输出结果。TTL(双晶体管逻辑)是一种

2024-01-23 13:52:51 7603

7603 数字电路中的逻辑门电路分类 数字电路是计算机系统中的重要组成部分,它们由逻辑门电路构成。逻辑门电路是一种基本的数字电路,用于根据输入的逻辑状态生成输出。逻辑门电路可分为多个类别,包括与门、或门、非门

2024-02-04 09:14:16 6326

6326 本文就CMOS或非门电路和TTL或非门电路的逻辑功能进行了详细讲解。首先介绍了CMOS和TTL两种电路的基本原理和实现方式。然后分别从输入特性、输出特性和功耗三个方面,深入比较了CMOS和TTL电路

2024-02-22 11:19:29 6039

6039 TTL(晶体管-晶体管逻辑)三态门是一种特殊类型的数字逻辑门,它具有三种输出状态:高电平、低电平和高阻抗状态(也称为三态或高阻态)。

2024-05-28 16:04:03 4169

4169 TTL三态输出门是一种特殊的数字逻辑门,它具有高电平、低电平和高阻抗(三态)三种输出状态。

2024-05-28 16:14:59 7654

7654 TTL三态门是一种特殊的逻辑门,它具有三个状态:高电平、低电平和高阻抗状态(也称为“三态”或“浮动”状态)。

2024-05-28 17:18:14 5097

5097 三态缓冲器之所以得名,是因为它具备三种不同的工作状态:正常逻辑状态输出、高阻状态和使能状态。这三种状态赋予了三态缓冲器强大的功能和灵活性。 1.正常逻辑状态输出:当使能输出有效时,三态缓冲器能够实现正常的逻辑状态输

2024-06-27 16:01:46 2510

2510 三态门电路是一种特殊的数字逻辑电路,其输出可以有三种状态:高电平、低电平和高阻抗状态。这种电路在数字系统中有着广泛的应用,如数据总线、地址总线等。 一、三态门电路的工作原理 三态门电路的基本组

2024-07-30 15:17:05 9711

9711 三态逻辑作为一种数字电子技术中的逻辑类型,允许信号线在三种状态之间切换。本文介绍了三态逻辑电路原理并介绍了四种基本类型的三态缓冲器。如果你对三态逻辑感兴趣,相信这篇内容会让你对其有基础的认识。

2024-08-01 09:59:32 5263

5263

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,是一种特殊的逻辑门电路,其工作原理主要基于三态输出控制。三态缓冲器对输入值不执行任何运算,其输出值和输入值一样,但它在计算机的设计中有着重要作用。

2024-08-02 17:47:05 9970

9970 中微爱芯推出可配置多功能逻辑门电路AiP74LVC1G99,该电路可配置为多种三态逻辑门,如“与门”、“与非门”、“或门”、“或非门”、“异或门”、“同或门”、“反相器”、“缓冲器”以及“多路复用器”,用法灵活多样。

2025-06-17 10:52:56 1055

1055

电子发烧友App

电子发烧友App

评论