`通过控制 variable streaming型FFT核进行FFT变换,首先前16周期进行1024点变换,然后跳转进行16点FFT,现在情况是,从FIFO 输出的采样数据正常输入到FFT核,控制

2017-12-12 17:04:14

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

`Xilinx FPGA入门连载74:波形发生器之IP核CORDIC(正弦波)功能仿真特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-04-25 08:33:11

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

在仿真fft ip核时 输出信号一直为0,检查了输入波形,应该没有问题,大家帮忙看看吧输入是由rom里面的mif文件产生的信号。

2017-11-21 10:44:53

我用quartus II调用modelsim仿真fft ip核,仿真结束后我想验证下数据是否正确,结果是:我用matlab生成同样的整形数据,然后用modelsim仿出的结果txt文件与用

2012-09-20 12:48:37

亲爱的大家我已经通过fft核心v9.0的数据表。我想实现FFT核心,但我没有在顶层模块(VHDL)中找到任何FFT核心的例子。如果有人建议我提供一些文档或示例,我将感激不尽。这是我第一次尝试在整个项目中使用xilinx IP核(顶层模块)最好的祝福

2020-05-21 08:19:53

用的xilinx的FFT 9.1版本的ip核 , 仿真出来的结果和我MATLAB算出来的结果差的很多,也没有倍数关系,scaled因数改了好几次,没有溢出,波形大致相同,但是数值上差的太多,已经弄了快两周了,求做过这个的讲讲经验。

2018-07-10 16:16:31

xilinx fft ip v7.1 仿真数据于matlab 仿真数据用很大差距,求指教

2015-10-14 20:48:43

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

:这些仿真模型输出文件只能用于仿真目的,一定不能用于综合或其他用途使用这些模型进行综合,将产生非函数设计(Non—al Design)。使用下面的步骤为FFT兆核函数产生IP功能仿真模型:(1)点击图

2012-08-13 14:34:06

有某试验数据,用matlab求fft之后再求得的功率谱密度是这样的:图1但是用fft ip核,取前4096个数据,得到fft之后的结果是这样的:图2求功率谱密度得到的是这样的:图3试验数据都是零点几

2016-04-21 20:36:18

本帖最后由 jf_25420317 于 2023-11-17 11:10 编辑

FPGA开发过程中,利用各种IP核,可以快速完成功能开发,不需要花费大量时间重复造轮子。

当我们面对使用新IP核

2023-11-17 11:09:22

FPGA的IP软核使用技巧主要包括以下几个方面:

理解IP软核的概念和特性 :

IP软核是指用硬件描述语言(如VHDL或Verilog)描述的功能块,但并不涉及具体的电路实现细节。它通常只经过功能

2024-05-27 16:13:24

Gowin FFT IP用户指南主要包括功能简介、信号定义、参数介绍、工作原理、GUI 调用等,旨在帮助用户快速了解高云半导体 Gowin FFT IP 的特性及使用方法。

2022-10-08 08:11:09

划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。 关键词:LCD;驱动电路;IP 引言

2012-08-12 12:28:42

最近在做FFT IP核,,走了好多弯路,LISENCE激活过了0034的IP核,通过修改LISENCE.DAT的方法。后来生成FFT的时候卡住,又尝试了关闭quartus_map进程和重装jre

2019-04-03 16:16:21

Xilinx为我们提供了一个叫做“Tri-Mode Ethernet MAC”的IP核,简称TEMAC核,三种模式的以太网介质访问控制层器,支持全双工半双工的千兆、百兆、十兆和2.5G的传输速率

2021-07-22 07:26:36

Vivado中xilinx_courdic IP核(求exp指数函数)使用

2021-03-03 07:35:03

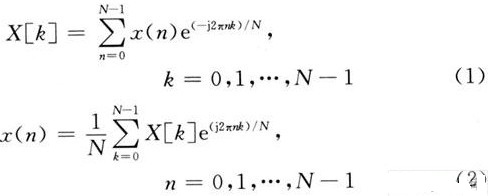

一.Xilinx FFT IP介绍

1.总体特性

•FFT IP核支持复数的正逆傅里叶变换,可以实时配置变换的长度

•变换的长度N=2 ^m^ ,m=3-16,即支持的点数范围为8-65536

2023-06-19 18:34:22

使用altera的FFTIP核的可变流结构进行FFT时,输出为什么跟实际情况是倍数关系

2016-09-20 19:18:10

ise FFT ip核的datasheet文档打不开什么原因

2015-08-27 14:46:45

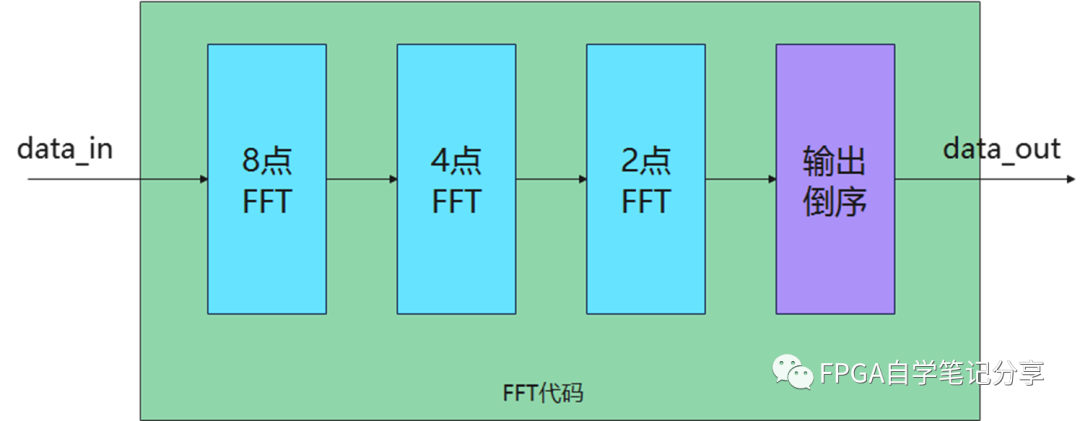

在quartusII中,应用fft ip核时,variable streaming 模式下的bit-reverse(位翻转)是什么意思?烦劳详细帮助新手解释一下,不甚感激

2017-01-09 10:55:59

数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。使用Verilog调用IP

2018-05-15 12:05:13

的数据是可以完全严格比对,如果设计中存在不能完全比对的情况,要特别注意相关参数是否匹配,尤其是缩放因子。一.Xilinx FFT IP介绍1.总体特性 •FFT IP核支持复数的正逆傅里叶变换,可以

2020-02-16 07:36:28

摘要针对FFT算法基于FPGA实现可配置的IP核。采用基于流水线结构和快速并行算法实现了蝶形运算和4k点FFT的输入点数、数据位宽、分解基自由配置。使用Verilog语言编写,利用ModelSim

2019-07-03 07:56:53

除了在Xilinx官网上在哪里能下载到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

刚刚接触IP核做FFT,现在用的是FFTV9.0,已经建立了一个IP核,但是如何仿真呢?是用quartus自带软件,还是要用MATLAB?抑或其他?我用的自带软件,但是什么也没有出来。正确的办法应该怎样呢,谢谢指点。

2011-04-21 10:22:31

本帖最后由 Laputa_fly 于 2013-11-23 13:46 编辑

用quartus9.0调用了altera FFT IP 核 生成了modisim 和 matlab 的仿真文件。用modelsim 仿真有结果。但是按照官方的使用说明用matlab仿真时出现问题。请大家帮忙解决一下。谢谢!

2013-11-23 13:43:41

通过例化调用Xilinx IP核来实现一个512点、数据位宽和相位因子位宽都为10 bit的FFT算法模块,时钟频率为 50MHz,采用流水线,Streaming I/O和定点压缩结构。为了方便验证

2016-12-27 14:12:20

在quartus II13.0版本上调用FFT IP核并进行modelsim-altera仿真,在生成IP核时,step2中勾选generate simulation model、generate

2016-10-07 22:23:33

Viterbi译码的基本过程,接着根据Viterbi译码器IP核的特点,分别详细介绍了并行结构、混合结构和基于混合结构的增信删余3种Viterbi译码器IP核的主要性能和使用方法,并通过应用实例给出了译码器IP

2010-04-26 16:08:39

基于FPGA的FFT和IFFT IP核应用实例AT7_Xilinx开发板(USB3.0+LVDS)资料共享腾讯链接:https://share.weiyun.com/5GQyKKc百度网盘链接

2019-08-10 14:30:03

Xilinx 官方提供的技术参数来实现对 IP 核的写控制。写命令和写数据总线介绍DDR3 SDRAM控制器IP

2022-02-08 07:08:01

我的quartus ii 版本13.1fft核版本13.1 modelsim版本64位 10.4在quartus ii 中使用rtl仿真时(已经在quartus ii中编译成功) 弹出

2019-02-26 16:21:08

的位宽定义是一样的,所以如图所示,只需要查看第0点的定点标定信息。详细的FFT IP核配置说明,可以参考Xilinx官方文档pg109-xfft.pdf。对于仿真产生

2020-01-07 09:33:53

fft仿真没有输出,初始值不正常,但上板验证没问题,试过重新生成ip核没有用,请教一下是什么问题。

2019-05-10 10:27:57

请教大家谁用过 Xilinx PCIe IP 核啊?

2014-01-15 14:38:28

如题,调用altera公司的FFT IP核,用的是13.1版本,将modulsim仿真的结果输入到matlab画出频谱图,功能仿真结果没有问题,但门级仿真中除了原频率信息外,出现了很多不存在的频率

2018-08-28 20:43:56

利用面向对象技术进行可配置的FFT IP 设计与实现摘要:为了缩短产品上市时间并降低设计成本,IP 复用已经成为IC设计的重要手段。以往利用RTL 代码编写的IP,往往是针对特定应

2010-07-04 11:42:13 8

8 利用FFT IP Core实现FFT算法

摘要:结合工程实践,介绍了一种利用FFT IP Core实现FFT的方法,设计能同时对两路实数序列进行256点FFT运算,并对转换结果进行求

2008-01-16 10:04:58 8042

8042

在论坛中经常有人会问起 altera 软件fft ip 中使用方法,有些人在使用这个fft ip core 的时候没有得到正确的结果,事实上,这个ip core 还是比较容易使用的。有些人得不到正确的仿真结果

2011-05-10 15:19:24 0

0 IP核生成文件:(Xilinx/Altera 同) IP核生成器生成 ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则asyn_fifo.veo 给出了例化该核方式(或者在 Edit-》Language Template-》C

2012-08-15 15:57:09 35

35 MC8051_IP核简单指令的仿真步骤。

2016-05-06 11:47:41 0

0 FFT变换的IP核的源代码,有需要的下来看看。

2016-05-24 09:45:40 18

18 利用FPGA的IP核设计和实现FFT算法

2016-05-24 14:14:47 37

37 Xilinx FPGA工程例子源码:FFT变换的IP核的源代码

2016-06-07 11:44:14 10

10 Xilinx FPGA工程例子源码:PCI Express IP核应用参考设计

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源码:USB IP核

2016-06-07 14:41:57 13

13 Xilinx FPGA工程例子源码:Xilinx TCP_IP协议实现

2016-06-07 14:54:57 33

33 Xilinx FPGA工程例子源码:Xilinx 的IP:1024点FFT快速傅立叶变换

2016-06-07 15:07:45 51

51 介绍如何设计HLS IP,并且在IP Integrator中使用它来作一个设计——这里生成两个HLS blocks的IP,并且在一个FFT(Xilinx IP)的设计中使用他们,最终使用RTL

2017-02-07 17:59:29 4760

4760

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-02-08 13:08:11 3085

3085

-FS/2~FS/2 提高采样频率则可提高量程,却会(在转换长度不变的情况下)降低分辨率。此时需要通过增加转换长度的方式增加分辨率,但却会增加处理时间。 相关ip核: FFT V7.1:适用于

2017-02-08 15:15:33 1559

1559 因为自从13.0开始,就开始有Qsys了,而关于FFT和NCO的仿真特别麻烦,网上有关资料又少之又少,所以特写此教程介绍怎么使用modelsim工具仿真附带有QSYS的fft和NCO的ip核的工程教程

2017-02-27 19:02:57 45

45 针对FFT算法基于FPGA实现可配置的IP核。采用基于流水线结构和快速并行算法实现了蝶形运算和4k点FFT的输入点数、数据位宽、分解基自由配置。使用Verilog语言编写,利用ModelSim仿真

2017-11-18 06:32:43 12871

12871

提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作原理,并

2017-11-22 07:20:50 5930

5930

由于OFDM接收机中大多是数据串并转换后的连续低速并行数据流输入FFT,故这里采用流水线结构。之后根据OFDM子载波数选择变换长度。该IP核仅支持50MHZ采样率数据的流水线处理,如果数高速通信场合,可以再次将数据串并转换用多个FFT IP核并行运算,也就是FPGA设计中常用的“面积换速度”。

2018-06-26 10:08:00 2401

2401

数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。 使用Verilog调用

2018-05-28 11:42:14 38569

38569 数字信号处理领域中FFT算法有着广泛的应用。目前现有的文献大多致力于研究利用FFT算法做有关信号处理、参数估计、F+FT蝶形运算单元与地址单元设计、不同算法的FFT实现以及FFT模型优化等方面。

2019-01-07 09:33:00 11670

11670

介绍了在大型工业模拟仿真系统中,利用FPGA和软IP核实现数据采集及收发控制的方案,并对其进行设计实现。重点阐述了在发送指令和采集接收两种数据流模式下.该IP核的控制处理逻辑及工作状态机的设计及实现

2018-11-07 11:14:19 20

20 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 10426

10426

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核

2020-12-29 15:59:39 13270

13270 Xilinx FIR IP的介绍与仿真 1 xilinx fir ip 简介 1)符合 AXI4-Stream 的接口 2)高性能有限脉冲响应(FIR),多相抽取器,多相内插器,半带,半带抽取器和半

2020-10-30 12:29:01 2178

2178 Xilinx快速傅立叶变换(FFT IP)内核实现了Cooley-Tukey FFT算法,这是一种计算有效的方法,用于计算离散傅立叶变换(DFT)。

2022-03-30 11:01:31 4200

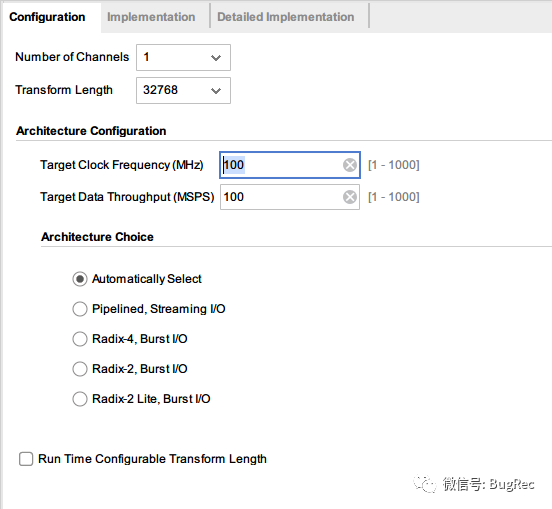

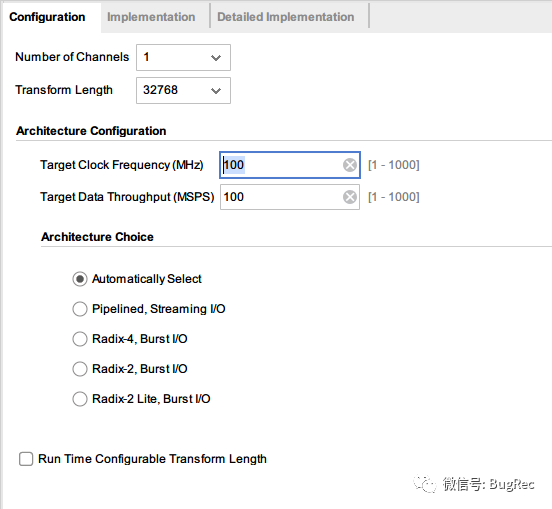

4200 以Xilinx Vivado设计套件中提供的FFT IP为例,简要说明如何进行FFT IP配置和设计。

2022-07-22 10:21:27 3424

3424 Vivado的FFT IP核支持多通道输入(Number of Channels)和实时更改FFT的点数(Run Time Configurable Transform Length)。

2022-09-07 14:31:20 6996

6996 Gowin FFT IP 用户指南主要包括功能简介、信号定义、参数介绍、工作

原理、GUI 调用等,旨在帮助用户快速了解高云半导体 Gowin FFT IP 的特

性及使用方法。

2022-09-15 10:19:24 1

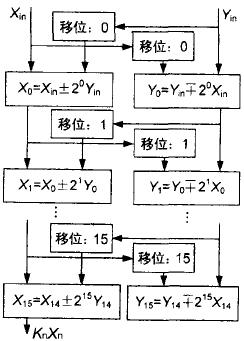

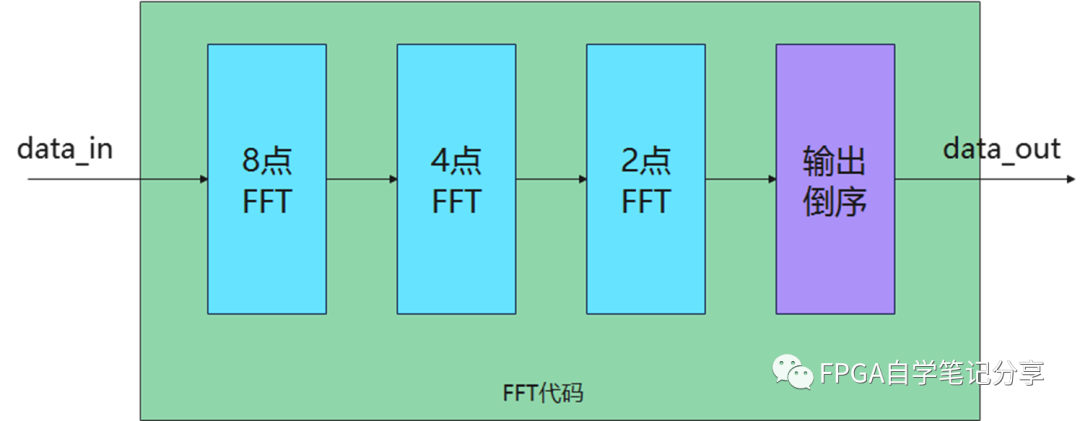

1 上文基2FFT的算法推导及python仿真推导了基2FFT的公式,并通过python做了算法验证,本文使用verilog实现8点基2FFT的代码。

2023-06-02 12:38:57 2761

2761

使用VCS仿真Vivado里面的IP核时,如果Vivado的IP核的仿真文件只有VHDL时,仿真将变得有些困难,VCS不能直接仿真VHDL

2023-06-06 11:15:35 3576

3576

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

这里做最简单的设置,打开Vivado,点开IP Catalog,找到FFT IP核。

2023-06-19 14:38:50 3580

3580

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109。

2023-07-10 10:43:18 2064

2064

DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

2023-07-24 11:23:29 8502

8502

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 在使用FPGA的时候,有些IP核是需要申请后才能使用的,本文介绍如何申请xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

用RAM实现一个DDS,从原理上来说很简单,在实际使用的时候,可能没有直接使用官方提供的IP核来的方便。这个博客就记录一下,最近使用到的这个DDS IP。

2024-10-25 16:54:11 5872

5872

本文介绍了Vidado中FFT IP核的使用,具体内容为:调用IP核>>配置界面介绍>>IP核端口介绍>>MATLAB生成测试数据>>测试verilogHDL>>TestBench仿真>>结果验证>>FFT运算。

2024-11-06 09:51:43 5640

5640

一 傅里叶变换FFT 想必大家对傅里叶老人家都不陌生了,网上也有这方面的很多资料。通过FFT将时域信号转换到频域,从而对一些在时域上难以分析的信号在频域上进行处理。在这里,我们需要注意采样频率

2025-01-08 11:33:44 3265

3265

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该 IP 核利用

2025-05-14 09:36:22 913

913

电子发烧友App

电子发烧友App

评论