Xilinx FIR IP的介绍与仿真

1 xilinx fir ip 简介

1)符合 AXI4-Stream 的接口

2)高性能有限脉冲响应(FIR),多相抽取器,多相内插器,半带,半带抽取器和半带内插器,希尔伯特变换和内插滤波器实现

3)最多支持 256 组系数,处理一组以上时,每组 2 至 2048 个系数。

4)输入数据高达 49 位精度

5)滤波器系数高达 49 位精度

6)支持多达 1024 个交错数据通道

7)支持高级交错数据通道序列

8)通过共享控制逻辑支持多个并行数据通道

9)插值和抽取因子通常最多为 64,单通道滤波器的最大为 1024

10)支持大于时钟频率的采样频率

11)在线系数重装能力

12)用户可选的输出舍入

13)高效的多列结构,适用于所有过滤器的实现和优化

Fir 公式

常规抽头延迟线 FIR 滤波器表示

2设计验证思路

混频模块内部包含两个 dds 模块,一个产生 2khz sine 波,一个产生 3khz sine 波,然后相乘得到 1khz+6khz 的混频,然后使用 xilinx FIR IP 设计一个低通滤波器滤掉 6khz,最后只剩 1khz。

3 matlab fdatool 设计低通滤波器

1)打开 fdatool

2)低通滤波器设计

Fs=44100;

Fpass =3000;

Fstop =5000;

Apass = 1;

Astop =120;

3系数量化

4)matlab 导出.coe

4 xilinx FIR IP的设置与仿真

左侧包含 IP Symbol、Freq.Response、Implementation Details 和 CoefficientReload。右侧包括 Filter Options、Channel Specification、Implementation、Detailed Implementation、Interface 和 Summary.

1)Filter Options

(1)系数源(Coefficient Source):直接在 GUI 中使用系数矢量参数或使用由 CoefficientFile 参数指定的 .coe 文件,指定要使用的系数输入。

(2)系数向量(Coefficient Vector ):用于直接在 GUI 中指定滤波器系数。过滤器系数使用逗号分隔列表以十进制形式指定,与过滤器系数数据文件中的 coefdata 字段相同。与 .coe 文件一样,可以使用 FIR 编译器根据您的要求适当量化的非整数实数来指定滤波器系数。

(3)滤波器类型(Filter Typ ):支持五种滤波器类型:单速率 FIR,插值 FIR,抽取 FIR,希尔伯特变换和插值 FIR。

2)Channel Specification

(1)选择格式(Select format ):选择用于指定硬件过采样率,内核可用于处理输入采样并生成输出的时钟周期数的格式。该值直接影响核心实现和所使用资源的并行度。选择“频率规格”后,可以指定“输入采样频率”和“时钟频率”。这些值之间的比率以及其他核心参数决定了硬件过采样率。

选择“输入采样周期”时,可以指定输入采样之间的时钟周期数。同样,选 择“输出采样周期”时,可以指定输出采样之间的时钟周期数。

(2)采样周期(Sample Period ):输入或输出采样之间的时钟周期数。当指定了多个通道时,该值应该是时分多路复用输入样本数据流之间时钟周期的整数。可以使用分数采样周期来指定大于时钟频率的采样频率 .

(3)输入采样频率(Input Sampling Frequency ):该字段可以是整数或实数值;它指定一个通道的采样频率。根据时钟频率和滤波器参数(例如插值率和通道数)设置上限。

(4)时钟频率(Clock Frequency ):此字段可以是整数或实数值。限制是根据采样频率,内插率和通道数设置的。该领域仅影响体系结构选择。最终的实现可能无法达到指定的时钟速率。

3) Implementation

(1)系数类型(Coefficient Type ):系数数据可以指定为有符号或无符号。

(2)输入数据小数位(Input Data Fractional Bits ):用于表示过滤器输入数据样本的小数部分的输入数据宽度位数。该字段仅供参考。它与系数小数位一起使用,以计算滤波器的输出小数位值。此参数在 IP 集成器中自动设置,但也可以被覆盖。

(3)输出舍入模式(Output Rounding Mode ):指定要应用于过滤器输出的舍入类型。

(4)输出小数位(Output Fractional Bits ):此字段报告用于表示滤波器输出样本小数部分的输出宽度位数

4) Interface

5) Freq.Response

将混频信号和经过 xilinx FIR IP滤波后信号写出 matlab 观察时域和频域 .

1混频信号

滤波前的 1khz+6khz 的混频信号。

2滤波后

如上所示,经过滤波后 6khz 完全被滤除,只剩下 1khz 信号。仿真验证成功。

审核编辑 黄昊宇

-

FIR

+关注

关注

4文章

151浏览量

35109 -

仿真

+关注

关注

53文章

4404浏览量

137648

发布评论请先 登录

Xilinx FPGA串行通信协议介绍

【产品介绍】Modelsim:HDL语言仿真软件

小白也能轻松上手!一招解决IP被封杀难题

FPGA利用DMA IP核实现ADC数据采集

Xilinx Shift RAM IP概述和主要功能

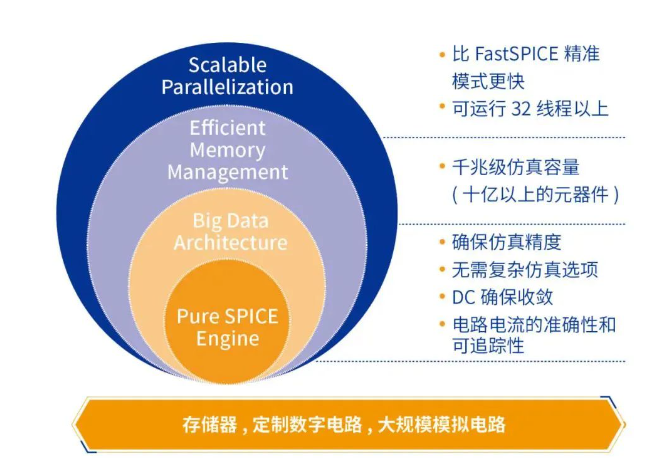

概伦电子千兆级高精度电路仿真器NanoSpice Giga介绍

详解Xilinx的10G PCS PMA IP

博世GTM IP模块架构介绍

Vivado FIR IP核实现

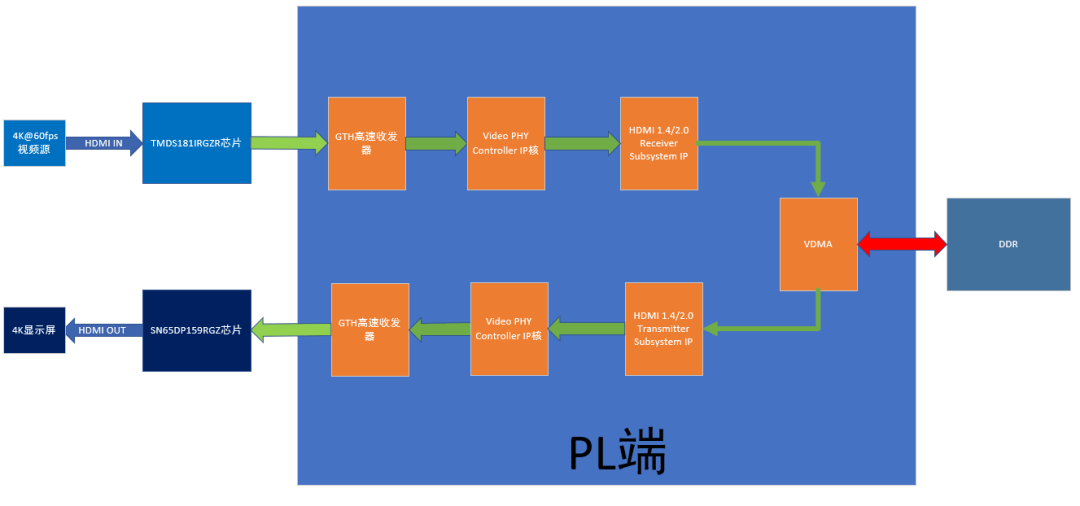

解锁4K,Xilinx MPSoC ARM + FPGA高清视频采集与显示方案!

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释

Xilinx FIR IP的介绍及仿真

Xilinx FIR IP的介绍及仿真

评论