)是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。 AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。 AXI4总线和AXI4-Lite总线具有相同的

2018-01-09 14:10:42 9365

9365

,我们依旧借助PYNQ_z2来完成。 1. ZYNQ功能块 ZYNQ中包含两大功能块:PS部分和PL部分。 PS部分指Processing System,一个

2020-12-25 14:11:50 9770

9770 ;AXI_GPIO是封装好的IP核,PS通过M_AXI_GPIO接口控制PL部分实现IO,使用时消耗管脚资源和逻辑资源。 使用的板子是zc702。 1.MIO方式 Zynq7000 系列芯片有 54 个

2020-12-26 10:12:57 5259

5259

使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL端的LED灯,实验虽然简单,不过可以让我们了解PL和PS是如何结合的。

2021-02-01 10:06:00 7851

7851

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常

2021-01-30 09:54:00 16464

16464

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

2021-02-22 13:51:00 9724

9724

/005899fe6815 二、ZYNQ7020 分为PS端、PL端 PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。 PL: 可编程逻辑

2021-05-12 10:25:31 19446

19446

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 3710

3710

xilinx mpsoc 平台中,PS 和 PL 进行交互时,PS 需要获取 PL 发出的中断信号。从 mpsoc 技术参考手册 ug1085 TRM 中可知,PL 给到 PS 的中断有两组

2023-08-24 16:06:22 2986

2986

PS176是一个显示端口 (DP)至HDMI 2.0视频接口转换器适用于需要视频协议转换的电缆适配器、电视接收器、监视器和其他应用。它将接受任何显示端口输入格式,包括DP 1.1a、dp

2022-05-18 10:31:07

ZYNQ进阶之路9--PS端实现FreeRTOS嵌入式系统导论FreeRTOS简介实现步骤导论在之前的章节中我们我们完成了PS端、PL端和PS+PL的一些工程,本章节我们插入一个小插曲,讲解

2021-12-22 08:29:20

(PS端) + FPGA可编程逻辑资源(PL端)异构多核SoC处理器设计的全国产工业评估板,PS端主频高达1GHz。核心板CPU、ROM、RAM、电源、晶振、连接器等所有器件均采用国产工业级方案

2024-07-25 16:14:10

到写数据通道中。当主机发送最后一个数据时,WLAST信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。 PS与PL内部通信(用户自定义IP)先要自定义一个AXI-Lite

2018-01-08 15:44:39

、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机

2021-05-28 14:28:28

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK中

2020-12-23 17:06:35

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35

2021-01-08 16:44:20

;AXI-Stream 的转换,只不过是专门针对视频、图像等二维数据的。AXI-CDMA:这个是由 PL 完成的将数据从内存的一个位置搬移到另一个位置,无需 CPU 来插手。涉及到DMA主要包括AXI

2022-03-31 11:39:10

的存储器。

⑥ACP : PL端可以直接从PS的Cache中拿到CPU计算的结果,延时低

⑦DMA :DMA控制接口,用于控制高速数据传输的通道。

(3)AXI协议

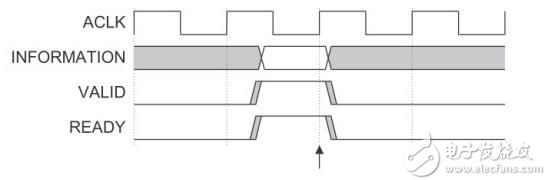

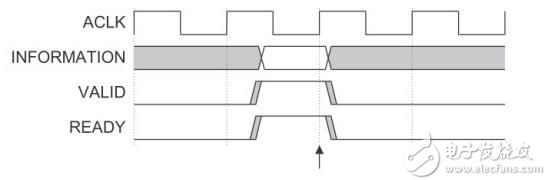

AXI所采用的是一种READY

2023-11-03 10:51:39

使用XPS时,然后将.xmp导入planahead,生成一个比特流文件。我可以使用chipcope / impact进行配置,从PS-> PL运行获取FCLK还是我必须导出到sdk?我正在

2019-09-05 06:03:46

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

PS端QSPI flash 存储PS端 SD卡,Emmc存储PL端32bit 1GB 容量DDR3 存储PL端扩展HDMI 输出实现视频显示应用PL端扩展16路 I/O, 4个LED指示灯PL端扩展标准

2020-03-24 09:39:49

,硬件资源丰富。可通过PL端进行高速图像数据采集,并通过PS端进行业务逻辑控制,运用十分便捷。(2)视频接口丰富可拓展众多目标追踪场合常用的视频接口,如CameraLink、SDI、HDMI、PAL等

2021-05-19 17:10:50

FFT的核心算法,以及与PS部分的数据交换。

PS部分包含了以下的组件:

ARM Core:这是一个基于ARM架构的处理器核心,它运行着我在上一章节介绍的PYNQ系统。它可以通过AXI Lite接口

2023-10-02 22:03:13

本帖最后由 blackroot 于 2015-6-10 17:06 编辑

一直没搞懂PS怎样给PL提供复位和时钟,今天这个问题终于解决了~~~~~用一个简单的例子来说明一下,怎样使用PS输出

2015-06-10 16:59:53

个逻辑胶合者被PS指挥;当然上电和初始化顺序还是一样的,必须先启动配置完PS,才能初始化PL。首先我们在Vivado开发环境中建立RTL工程,并编写我们需要在PL中实现的功能代码HDL文件,把它做为

2015-06-01 11:54:12

总线的从接口,和AXI主接口实现互联,来对BRAM进行读写操作。针对不同的应用场合,该IP核支持单次传输和突发传输两种方式。14.2实验任务本章的实验任务是PS将串口接收到的数据写入BRAM,然后从

2020-09-04 11:08:46

CameraLink1接口输入的差分视频数据转化成并行视频数据。lvds_n_x_1to7_sdr_rx模块开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录

2021-04-19 15:26:53

道数据差分对为4组,需2个连接器。图 114.2lvds_n_x_1to7_sdr_rx模块本案例使用lvds_n_x_1to7_sdr_rx模块将CameraLink1接口输入的差分视频数据转化成

2021-04-22 09:14:50

道数据差分对为4组,需2个连接器。图 114.2lvds_n_x_1to7_sdr_rx模块本案例使用lvds_n_x_1to7_sdr_rx模块将CameraLink1接口输入的差分视频数据转化成并行

2021-04-27 09:40:41

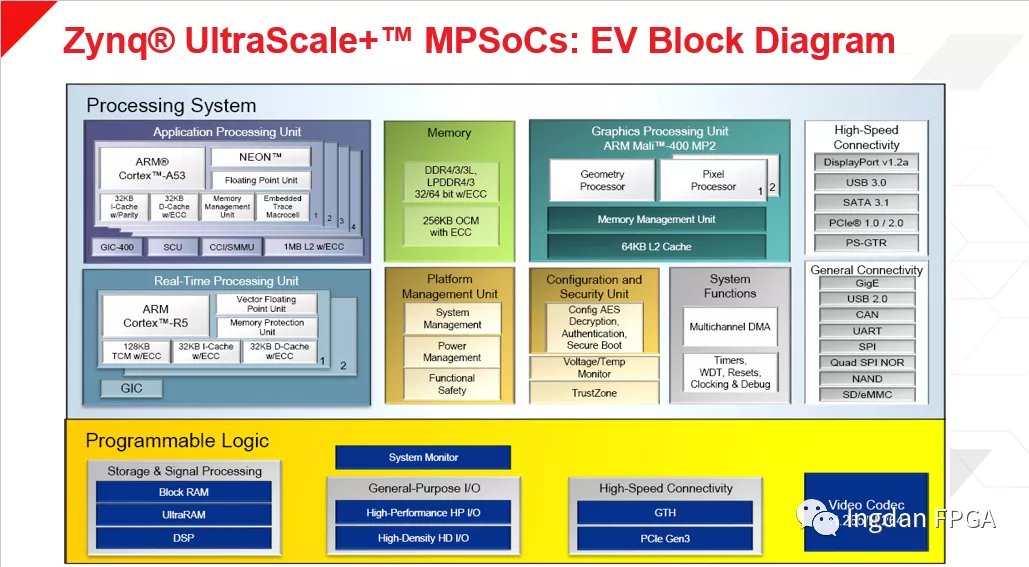

XCZU7EV高性能处理器设计的高端异构多核SoC工业核心板,处理器集成PS端(四核ARM Cortex-A53 + 双核ARM Cortex-R5) + PL端UltraScale+架构可编程逻辑资源,支持

2023-06-21 15:27:45

和M_AXI_HPM0_LPD。 位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。Xilinx在Vivado开发环境里提供现成IP如AXI-DMA,AXI-GPIO

2021-01-07 17:11:26

LT8911 LT7211、普瑞PS8625、昆泰CH7511等方案,DP换LVDS转换主要是用在一些LVDS接口的液晶,将DP信号转出至LVDS屏输出,此时需要用DP TO LVDS这样一个转接板来实现屏显示

2021-08-02 20:00:42

错误。然后,我在SDK中编程PS端,led闪烁正确的频率!我的问题,当锁定Zynq PL时钟? PS程序之后?需要多长时间?是不是意味着,PL配置期间LED闪烁错误,在非易失性Flas Boot中编程PS期间(或之后)闪烁?谢谢的Berker

2020-08-27 15:09:19

我想给板子接上一个u***接口的键盘,不跑操作系统,只用ps部分接收键盘的数据然后传递给PL,不知道如何编写sdk的代码来跟u***的phy通信呢?有没可以参考的例程或者文档?

2015-12-16 17:12:38

(Processing System,PS)和可编程逻辑资源(Programmable Logic,PL)),提供了基于Zynq-7010/7020的多路千兆网口实现方案。1 硬件平台TLZ7x-EasyEVM-S

2021-10-22 09:43:10

FPGA 外围的数据传输带宽以及存储器带宽。但是在 FPGA 内部,可编程逻辑部分随着工艺提升而不断进步的同时,内外部数据交换性能的提升并没有那么明显,所以 FPGA 内部数据的交换越来越成为数据传输的瓶颈

2020-09-07 15:25:33

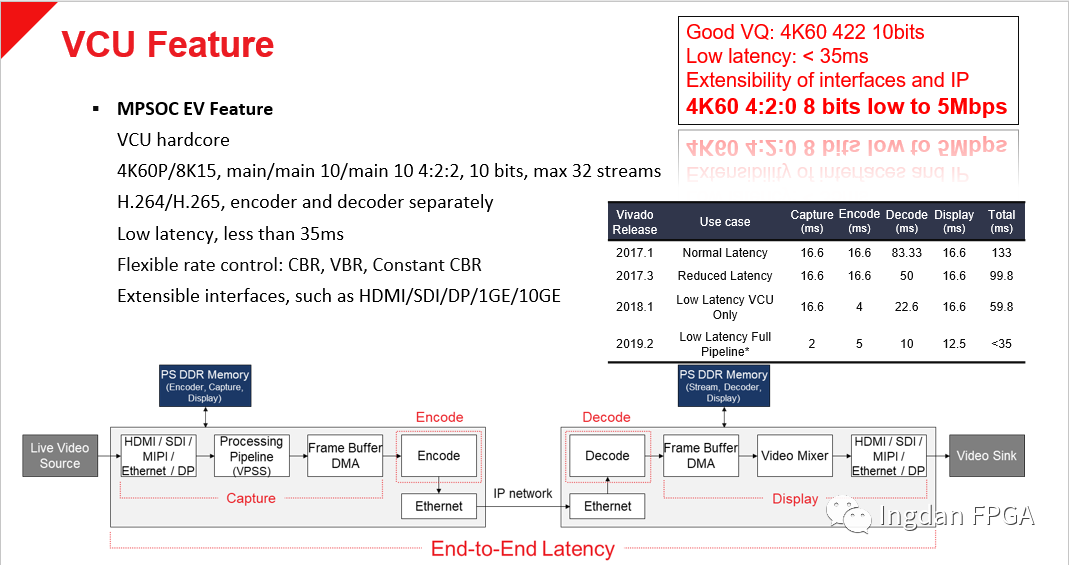

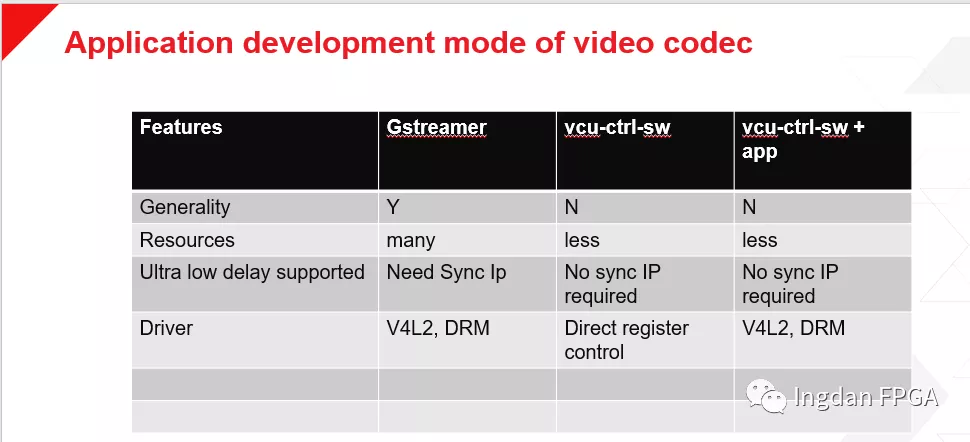

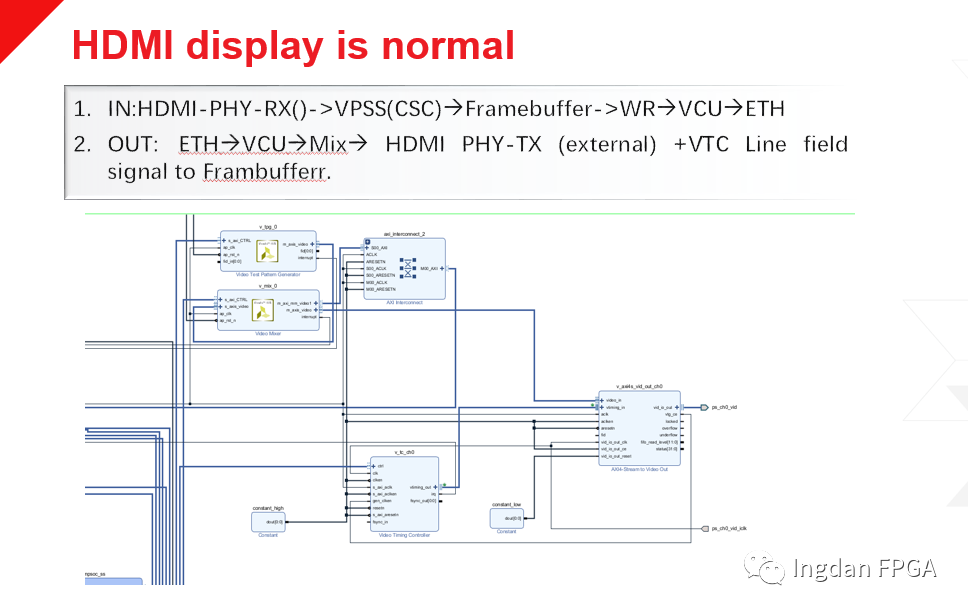

的前提下,调整H.265编码的目标码率,避免过低的码率影响视频质量或过高的码率导致带宽浪费或。通过CBR或VBR模式可以根据网络情况动态调整码率。

低延时模式 :VCU支持低延时编码模式,确保视频在压缩

2024-10-14 17:42:19

随着USB C接口的普及,越来越多的笔记本只保留了USB C接口来传输视频信号,而显示端依旧是HDMI的天下。因此,许多需要扩展显示的场景必须配备一个USB C to HDMI的适配器来实现。如会议

2019-09-23 09:05:04

FMQL20S400M是复旦微四核ARM Cortex-A7@1GHz(PS端)+85K可编程逻辑资源(PL端)异构多核SoC处理器。创龙科技基于FMQL20S400M设计的工业核心板

2024-08-22 14:04:12

文件的PL,然后给每个人提供刺激来测试设计,PS将从PL回读一些输出,在结束我将结果数据发送回用户。换句话说,它是一种“设计测试”服务。(1)我有什么方法可以达到这个目标吗?似乎唯一的“cat

2020-05-21 07:07:50

我的设备是zedboard702,我知道如何在使用PS和PL时使用SDK生成启动映像和程序闪存。问题是我只是使用PL,现在如何编程flash?

2019-09-30 09:43:18

亲爱的大家,我只是想知道如何找到Ultrascale +的PL和PS的地址转换(映射方案到DRAM-我的意思是哪个等级,库等)?

2019-10-16 08:35:37

百万组随机数据matlab和Verilog代码仿真比对;FFT模块详解缩放因子;提供各类定点模型及源代码;提供AD936X配置源码。配套近2000分钟视频教程详述稀疏校验矩阵存储及LDPC编码实现方式

2019-07-23 10:56:41

。ACP为64位AXI从接口,它提供了一个异步缓存相关接入点,实现了PS和PL端加速器之间的低延迟路径。AXI Timer IP核用于计数,可通过其寄存器来计算浮点矩阵乘法运算加速器IP核的运算时间。图

2021-11-11 16:02:09

为配置PL逻辑的控制器),也可以同时配置PS和PL逻辑,可见Zynq芯片可以灵活的搭建嵌入式平台实现不同的功能。这个通过模块图就可以看得更清楚了。http://www.xilinx

2016-10-05 14:05:31

大家好,我已经在PS中产生了一个100Mhz的时钟信号,并使其在外部被PL接收。我使用了原始的ODDR但没有成功我可以从引脚输出100 Mhz时钟。有什么建议么??以上来自于谷歌翻译以下为原文

2019-02-22 09:09:05

一直拉高的。这与写数据通道好像有点区别。

我不清楚PS 端的DDR到底发生了什么,但是和MIG核就是有点不一样,通过仿真MIG核可以发现,PL端的DDR是会先一直发出wready信号的。这个问题就是我

2024-05-31 12:04:29

为什么一个简单的程序运行不了,请求帮忙看一下。做个LED流水灯,是想用PS部分生成100MHz的频率,然后用这个频率来实现PL部分三色led移位,但是好像PS部分有问题,不知道怎么配置了。这是PS

2016-01-02 21:35:38

对应的信号功能后,在PL的代码里面就不需要写任何的逻辑,甚至引脚分配都不需要(生成的PS系统会自动分配)。但是EMIO就要在PS的系统中引出,然后在PL顶层源码中申明端口类型,做引脚分配(因为EMIO用

2019-10-12 17:35:16

定制协处理器引擎来高效的实现该算法,这个使用硬件逻辑实现的协处理器,可以通过AMBA接口与全可编程SoC内的ARM Cortex A9嵌入式处理器连接,此外,通过XilinX所提供的最新高级综合工具

2024-04-10 16:00:14

系统性能的瓶颈时,设计人员可以选全可编程SoC内使用硬件逻辑定制协处理器引擎来高效的实现该算法,这个使用硬件逻辑实现的协处理器,可以通过AMBA接口与全可编程SoC内的ARM Cortex A9嵌入式

2024-05-08 16:23:11

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

2020-08-03 15:53:30

的Linux的xdevcfg设备来编程PL部件。有趣的解决方案是通过在同一芯片的PS部分运行的XVC远程调试基于Zynq的设计。假设我将XAPP1251中描述的AXI-JTAG控制器添加到我的设计中,是否

2020-07-30 13:51:19

基于PS/2鼠标接口单片机输入设备的实现:详细介绍了PS/2鼠标/键盘接口的工作原理.提出了基于PS/2接口的三键鼠标作为单片机输入设备的方法.该方案占用系统资源少,软硬件

2009-10-27 18:30:48 82

82 RS232接口在嵌入式设备中应用广泛。为了充分利用USB接口即插即用的特点,详细介绍一种基于PL2303的RS232与USB转换的设计方案。PL2303是高集成度的通用串行总线(USB)与串口的接口转

2010-12-31 17:23:17 277

277 什么是ps2接口 ps2接口是什么意思?

PS/2接口是目前最常见的鼠标接口,最初是IBM公司的专利,俗称“小口”。这是一种鼠标和键

2009-05-03 22:07:26 27856

27856

什么是PS/2接口

很多老式的品牌机上采用PS/2口来

2010-01-22 12:21:57 2542

2542 一步一步学ZedBoard:使用PL做流水灯:目的是为了学习不使用ARM PS情况下,只对Zynq PL的编程方法,同时学习Xilinx PlanAhead工具的使用方法。(本资料是其相应的完整工程文件下载)

2012-12-05 13:52:39 186

186 本文通过实例详细解析如何利用Zynq-7000的PL和PS进行交互。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22 58287

58287

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1、传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送; 2、PL端接口为FIFO接口; PS到PL的数据传输流程: PS

2017-02-08 01:00:11 2324

2324

因为MicroZed是个低成本的开发套件,所以在板子上除了给PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。

2017-02-09 14:16:11 4978

4978

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 1426

1426

我们先来了解一下上节中介绍的Zynq SoC PS/PL接口,我创建一个很简单的外设,使用的是DSP48E1的DSP逻辑片,依靠这个外设第一个寄存器内的控制字执行乘法,加法或减法。

2017-02-10 12:04:41 843

843

《一步一步学ZedBoard & Zynq》系列第二篇,目的是为了学习不使用ARM PS情况下,只对Zynq PL的编程方法,同时学习Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11 4268

4268 构建SoC系统,毕竟是需要实现PS和PL间的数据交互,如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,本节研究如何再实现PL端对DDR3的读写操作。

2017-09-18 11:08:55 23

23 赛灵思 Zynq™- 7000 All Programmable SoC真正的重要优势之一就是能够通过在可编程逻辑(PL)侧构建外设来提高器件处理系统(PS)侧的性能。最初您可能会认为这将是一项

2017-11-22 14:04:02 1293

1293 zedboard可以将逻辑资源和软件分别映射到PS和PL中,这样可以实现独一无二和差异换的系统功能,主要分为两大部分,处理系统和可编程逻辑。以及二者之间的互联特性。这篇笔记主要记录zedboard的大体架构。

2018-06-26 06:24:00 7451

7451 Zynq在PS和PL之间有9个AXI接口。

2018-12-30 09:45:00 8294

8294 Zynq-7000系列基于Xilinx SoC架构。这些产品在单个设备中集成了功能丰富的双核或单核ARM Cortex™-A9处理系统(PS)和28 nm Xilinx可编程逻辑(PL)。ARM Cortex-A9 CPU是PS的核心,还包括片上存储器、外部存储器接口和一组丰富的外围连接接口。

2019-02-23 11:52:33 63

63 MPSoC是Xilinx基于16nm工艺推出的异构计算平台,由于灵活、稳定,在业界得到了广泛的使用。异构计算是一个比较新的领域,需要协调硬件设计、逻辑设计、软件设计,对工程师的要求很高。实际设计过程中,很多工程师对实现PS/PL之间的数据交互感到头疼。

2020-09-15 09:27:00 12835

12835

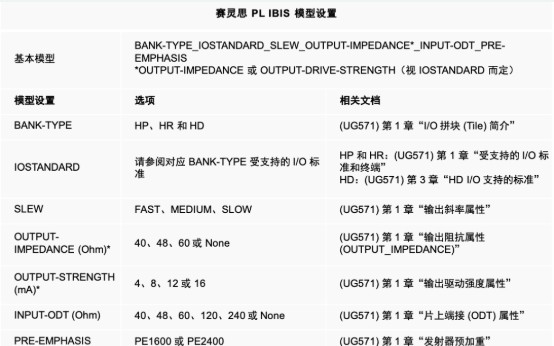

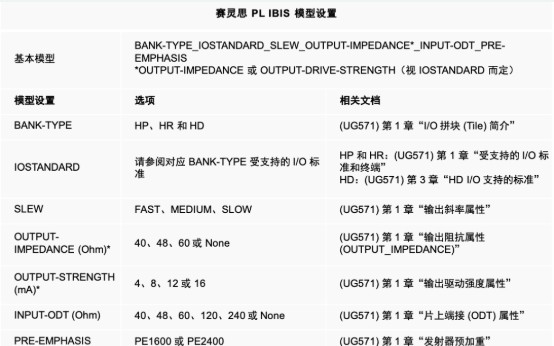

。 本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。 本文主要分 3 个部分: PL I/O 标准 PS MIO

2020-10-15 18:29:15 3123

3123

Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2022-02-08 14:19:49 2342

2342

Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2021-01-23 06:32:33 10

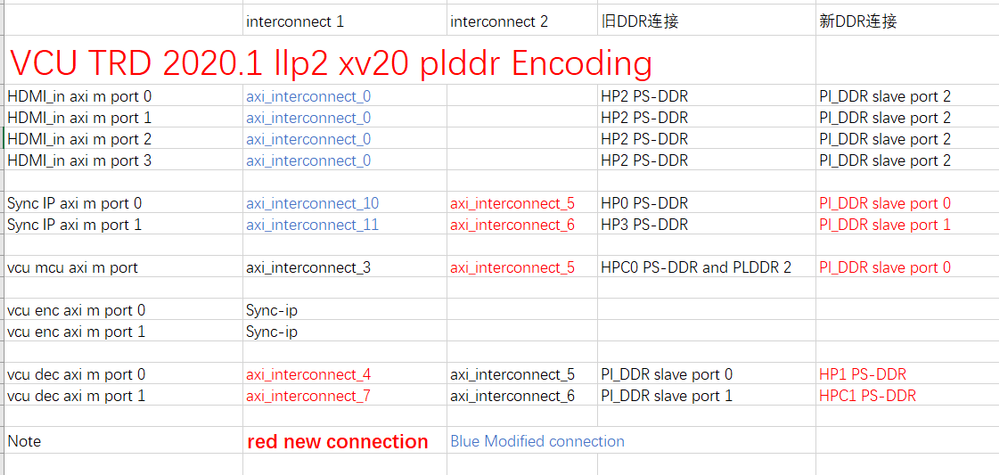

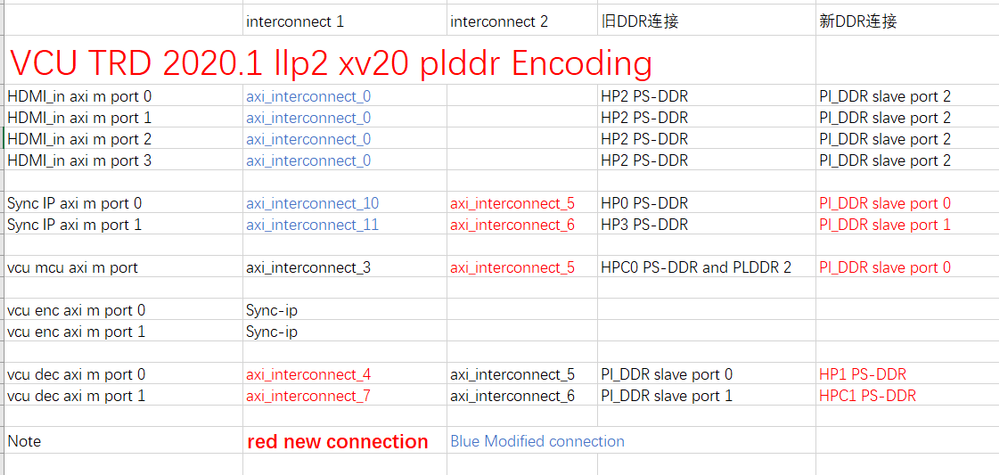

10 Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency XV20 提供了详细命令。 缺省情况下,编码使用的是PS

2021-05-07 15:30:13 7143

7143

Programmable Gate Array是缩写,即现场可编程门阵列,那可编程逻辑PL是什么呢,又有什么特点,我们来介绍一下。 PL提供了用户可配置功能的丰富体系结构,包括可配置逻辑块、

2021-06-18 16:09:46 11177

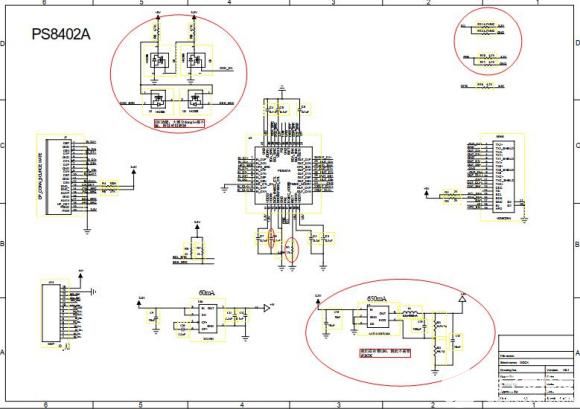

11177 的、抖动非常低的HDMI输出。PS8402A包括I2C over AUX转换和2路DisplayPort双模适配器实现所需的寄存器。PS8402A向后兼容现有的双模DP源设备以及为2路适配器启

2021-11-22 16:06:57 1418

1418

ARM 的 AXI 是一种面向突发的协议,旨在提供高带宽同时提供低延迟。每个 AXI 端口都包含独立的读写通道。要求不高的接口使用的 AXI 协议的一个版本是 AXI4-Lite,它是一种更简单

2022-05-10 09:52:12 4732

4732 这篇文章记录ZYNQ7020的PS端的基本开发流程,关于PL端的开发流程,参考之前文章,这里放个超链接。

2022-07-24 18:12:57 12419

12419 MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线

2022-08-02 09:45:03 1412

1412 Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency XV20 提供了详细命令。缺省情况下,编码使用的是PS DDR

2022-08-02 09:12:42 1212

1212

电子发烧友网站提供《将Zynq PS和PL与内存映射寄存器集成.zip》资料免费下载

2022-12-06 15:14:29 2

2 Zynq-7000系列芯片的逻辑资源(PL)是不同的,Z-7020以下是基于A7 FPGA的,Z-7030以上是基于K7的,资源数量有所不同。而我们使用的Zedboard是Z-7020的。

2022-12-22 09:44:09 3421

3421 S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

2023-02-01 15:36:53 4694

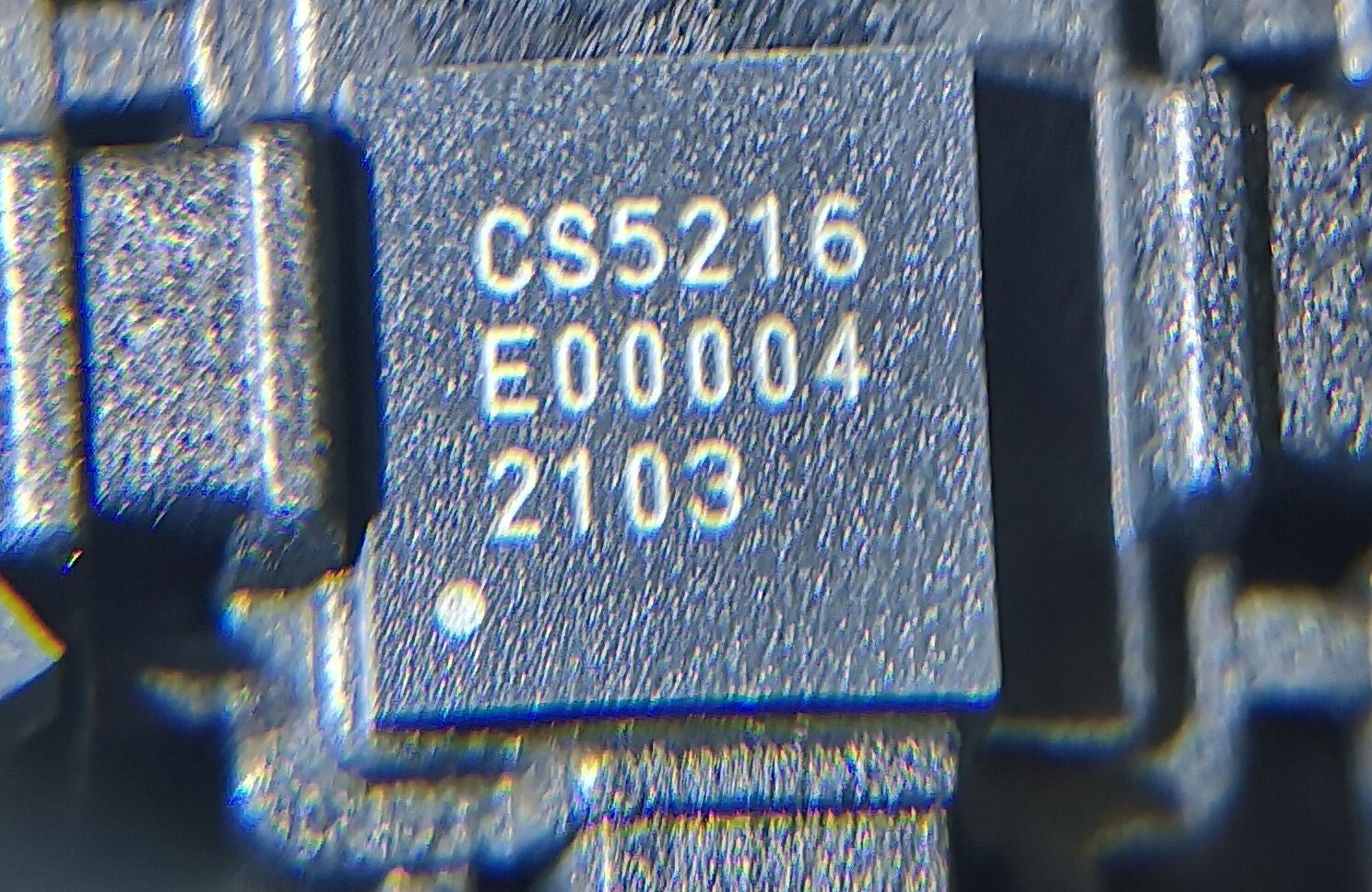

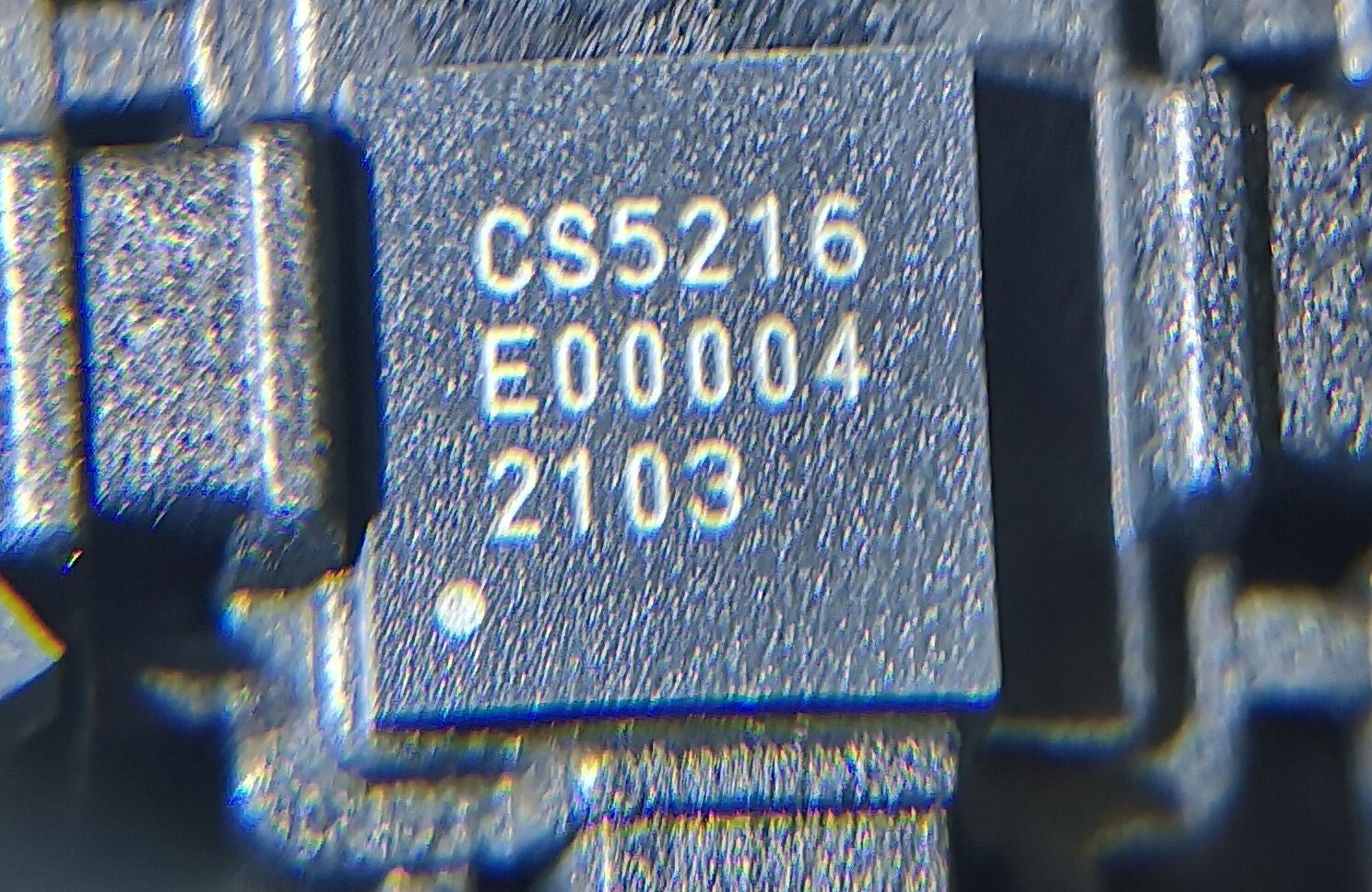

4694 CS5216 DP转HDMI Pin to Pin替代PS8402A方案|PS8402A替代方案|替代PS8402A

2022-03-23 16:16:09 1704

1704

PS176替代方案|PS176 DP++ to HDMI(4K@30Hz)替代方案|CS5218替代PS176

2022-03-23 18:27:07 3030

3030

ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,虽然 PS 端的 ARM 是硬核,但是在 ZYNQ 当中也要将 ARM 硬核添加到工程当中才能使用,FPGA

2023-08-11 09:36:34 13624

13624

电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案应用笔记.pdf》资料免费下载

2023-09-15 10:29:25 3

3 电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案.pdf》资料免费下载

2023-09-15 10:05:18 2

2 骊微电子供应PL3368CPL3369C10-12W电源方案,可以直接兼容替换DP2525,更多产品手册、应用料资请向骊微电子申请。>>

2021-12-10 15:18:06 4

4 资料\Demo\All-Programmable-SoC-demos\”目录下。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机/Linu

2023-01-03 15:50:37 19

19 ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之间的数据交互是系统设计的核心。

2025-10-15 10:33:19 738

738

电子发烧友App

电子发烧友App

评论