本篇主要介绍了Linux中断的使用方法,通过按键来进行中断实验测试,并使用Linux定时器进行按键去抖。

2022-05-25 09:09:05 4843

4843

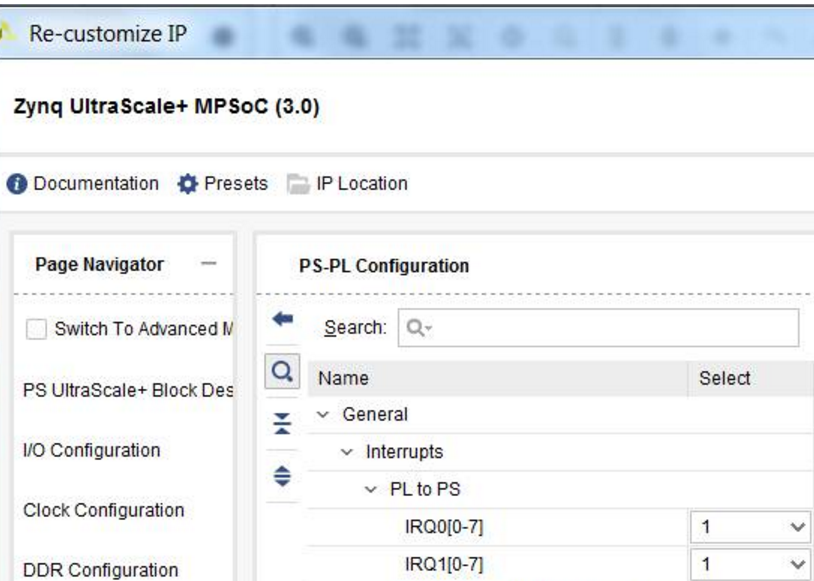

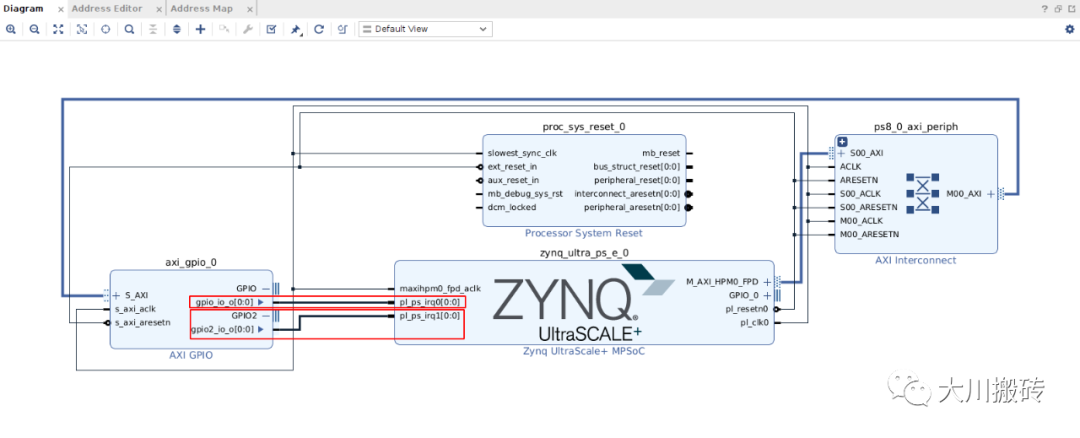

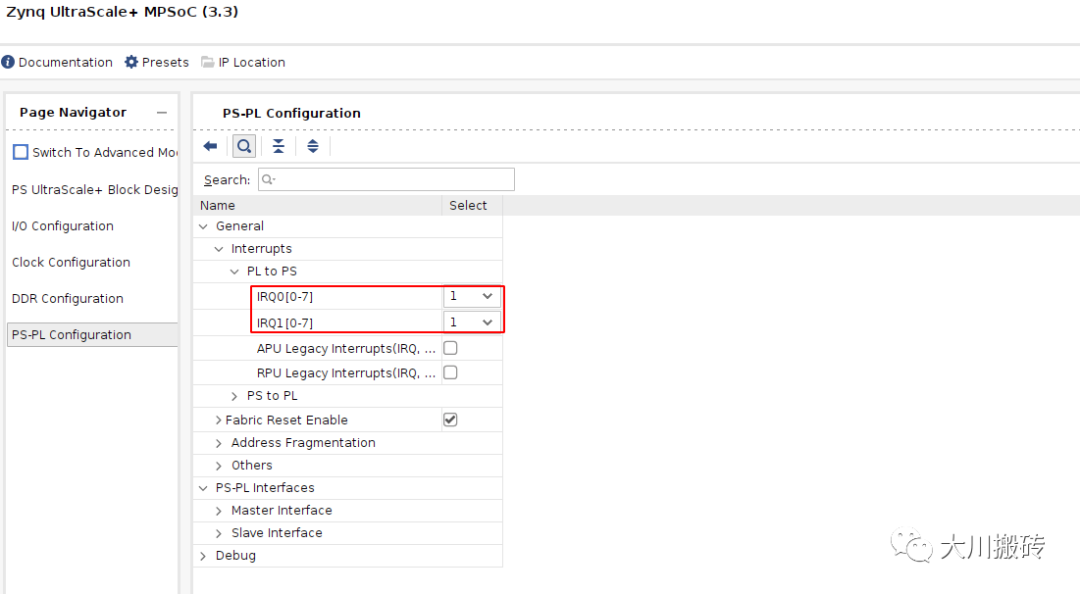

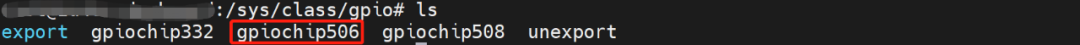

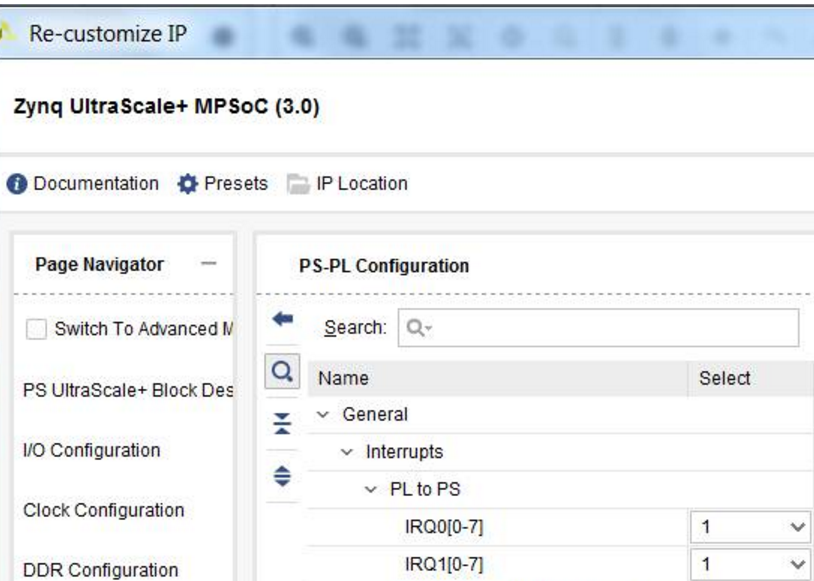

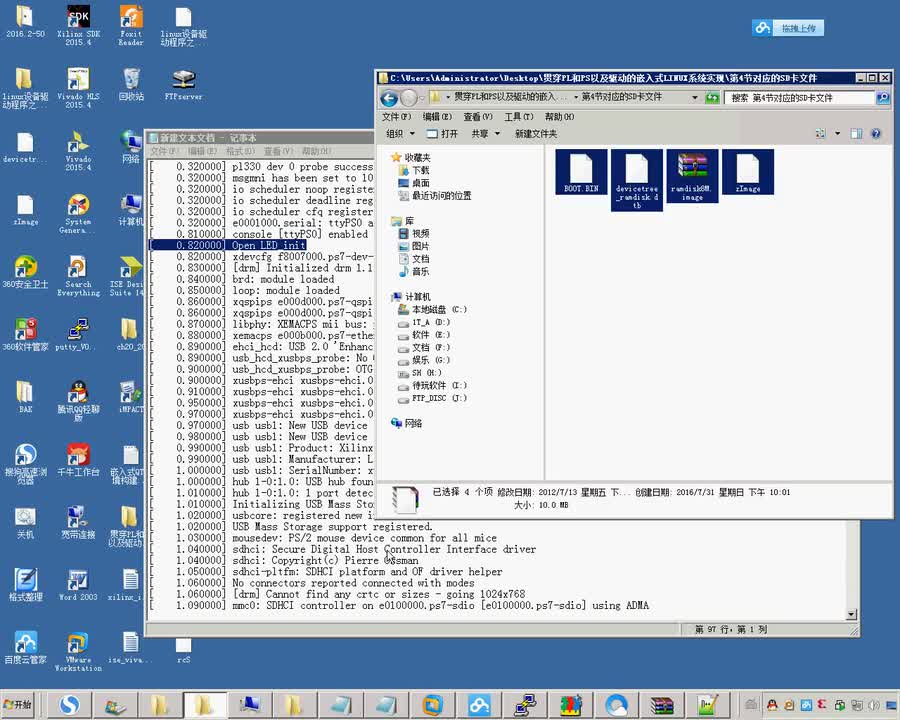

硬件连接MPSoC 可以接收两组来自 PL 的中断信号。在 Vivado 中,可以通过 PS-PL Conf

2017-09-28 06:39:00 9863

9863

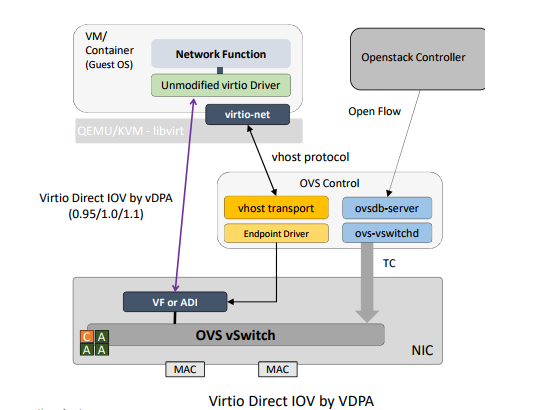

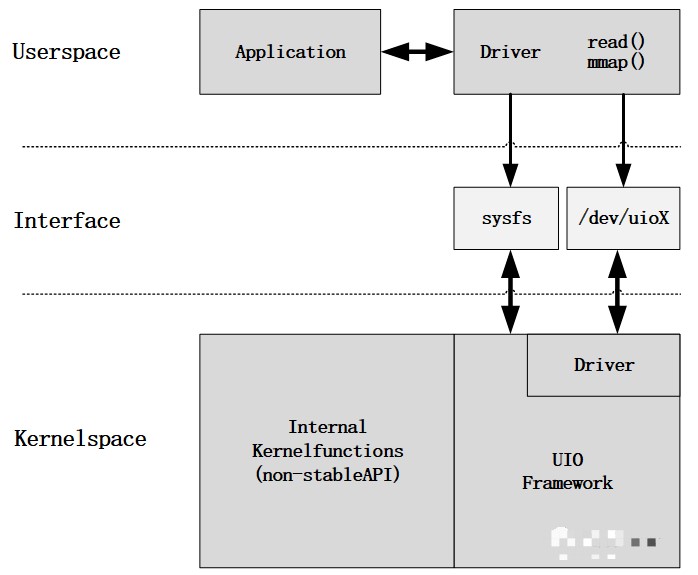

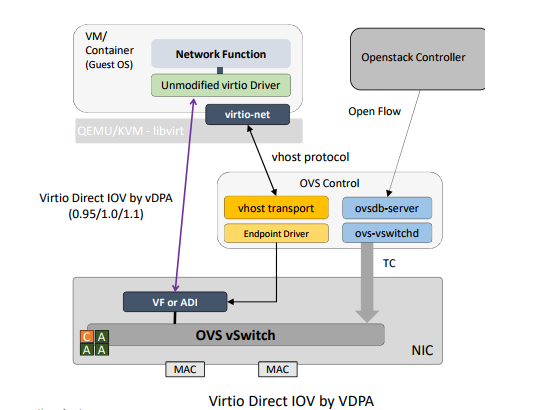

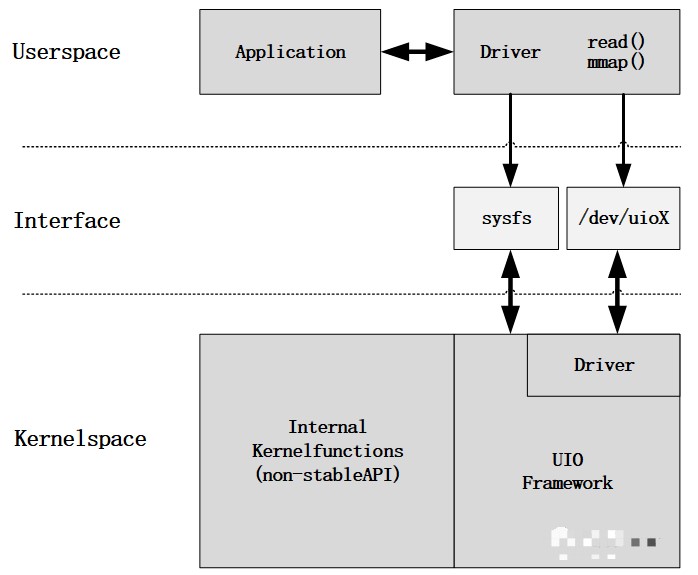

vfio是Linux Kernel UIO特性的升级版本。UIO的作用是把一个设备的IO和中断能力暴露给用户态,从而实现在用户态对硬件的直接访问。

2020-09-25 15:32:49 10132

10132

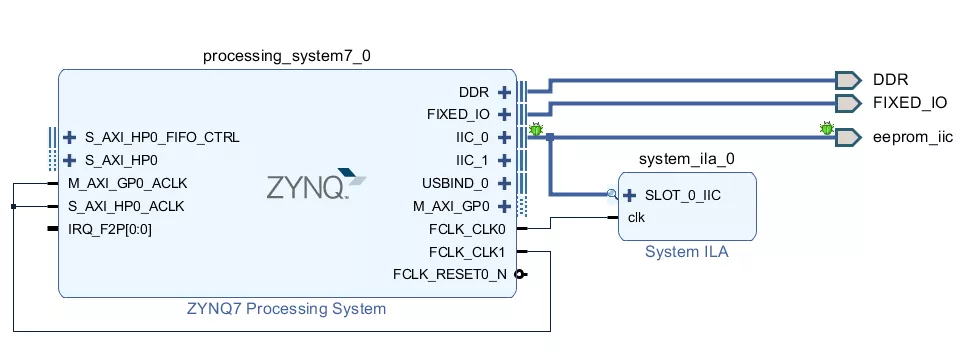

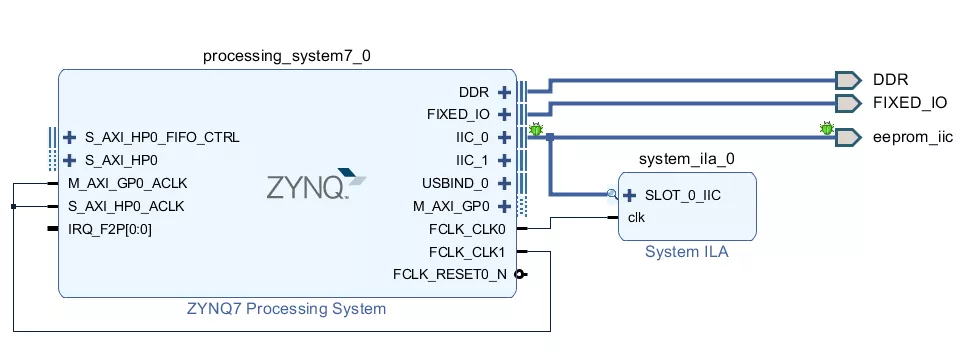

的逻辑部分,PS侧为arm端以及一些AXI接口控制部分,二者实际上通过AXI接口实现通信和互联。PS可以通过AXI来对PL逻辑部分进行配置和控制,PL侧通过AXI和PS进行数据交互。本章

2020-11-30 11:56:01 5532

5532

。 Pynq降低了开发人员的门槛,但知其然也知其所以然,开发效率将会更高。因此,在进入PYNQ的python开发之前,我们先来学习ZYNQ的PL与PS开发,为接下来的学习提供良好的基础。 本部分的学习

2020-12-25 14:11:50 9770

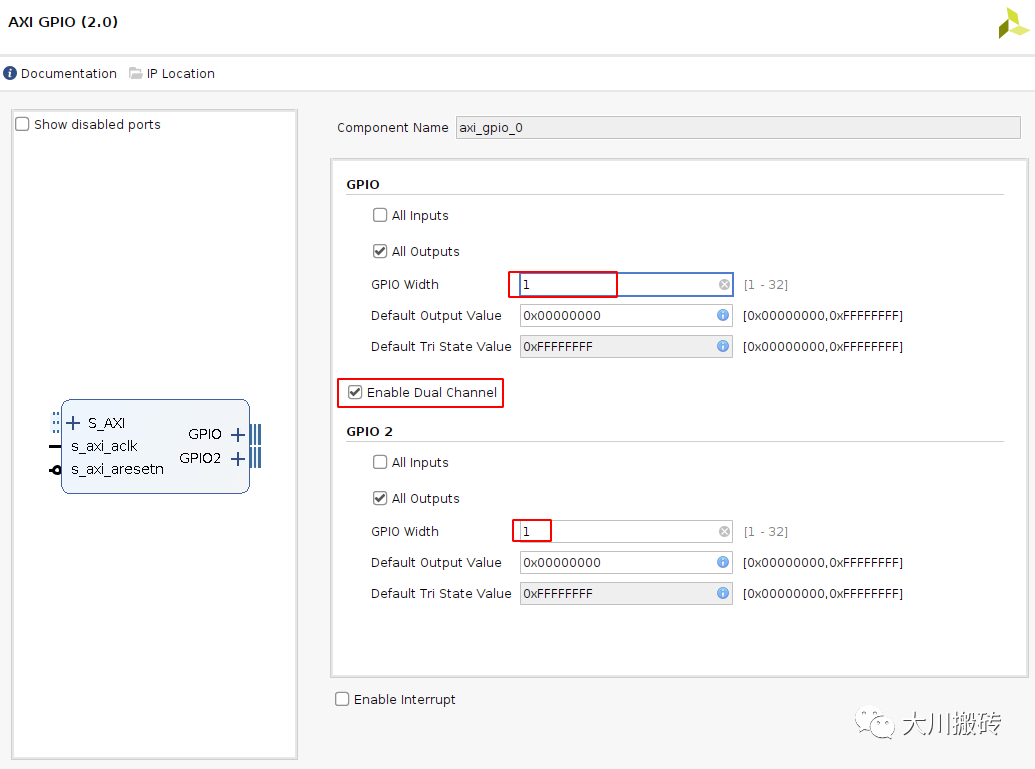

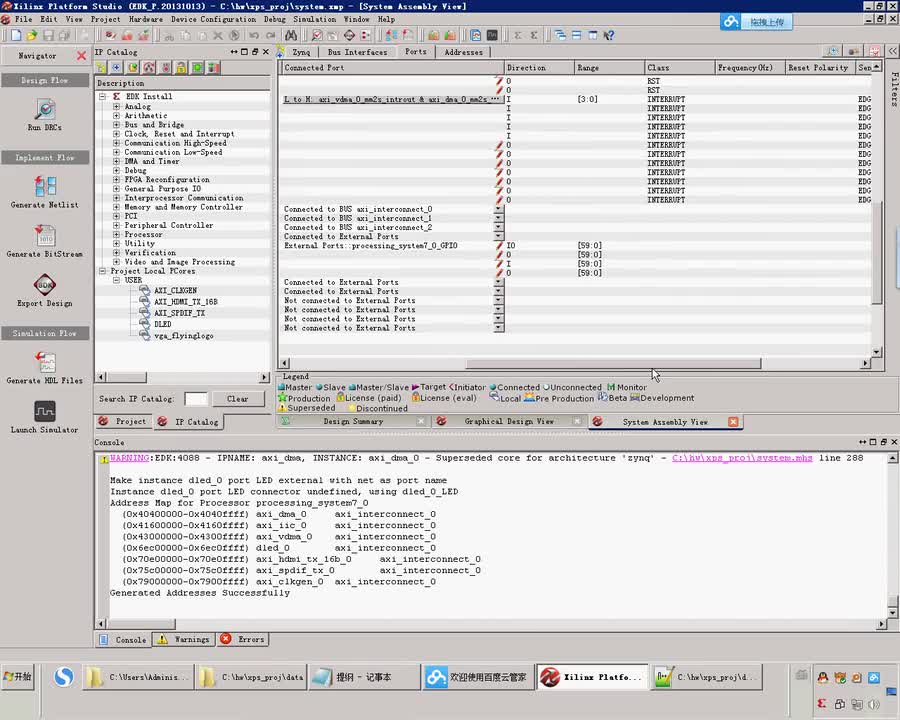

9770 使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL端的LED灯,实验虽然简单,不过可以让我们了解PL和PS是如何结合的。

2021-02-01 10:06:00 7851

7851

麻烦,灵活性也比较差,本节课程讲解如何直接通过AXI总线来读写PS端ddr的数据,这里面涉及到AXI4协议,vivado的FPGA调试等。

2021-01-30 09:54:00 16464

16464

/005899fe6815 二、ZYNQ7020 分为PS端、PL端 PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。 PL: 可编程逻辑

2021-05-12 10:25:31 19446

19446

。 axi_timer_pwm_demo案例 1 案例功能 案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI Timer IP核,IP核再根据命令通过PWM方式控制评估底板PL端LED5的状态

2021-09-07 17:03:30 3710

3710

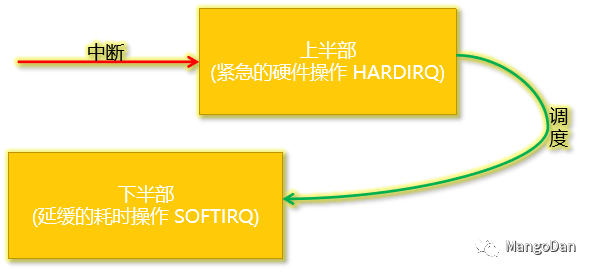

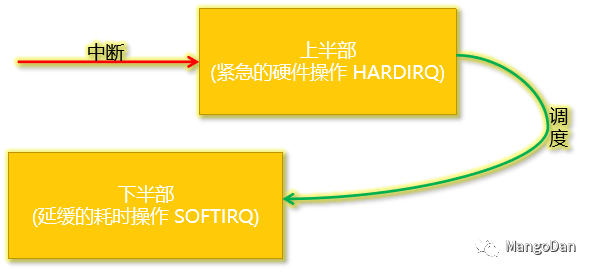

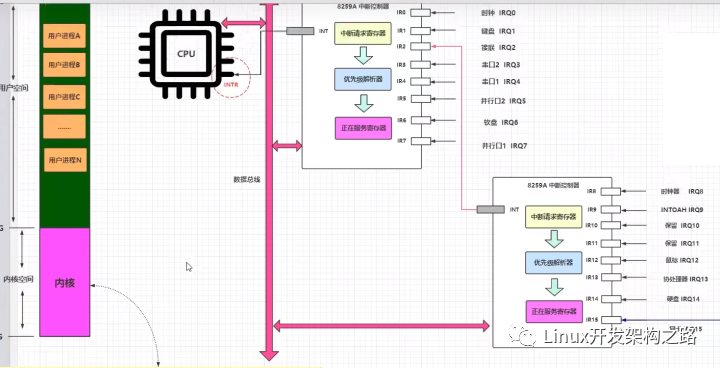

裸机编程中使用中断比较麻烦,需要配置寄存器、使能IRQ等等。而在Linux驱动编程中,内核提供了完善的终端框架,只需要申请中断,然后注册中断处理函数即可,使用非常方便。

2022-07-29 08:57:24 1157

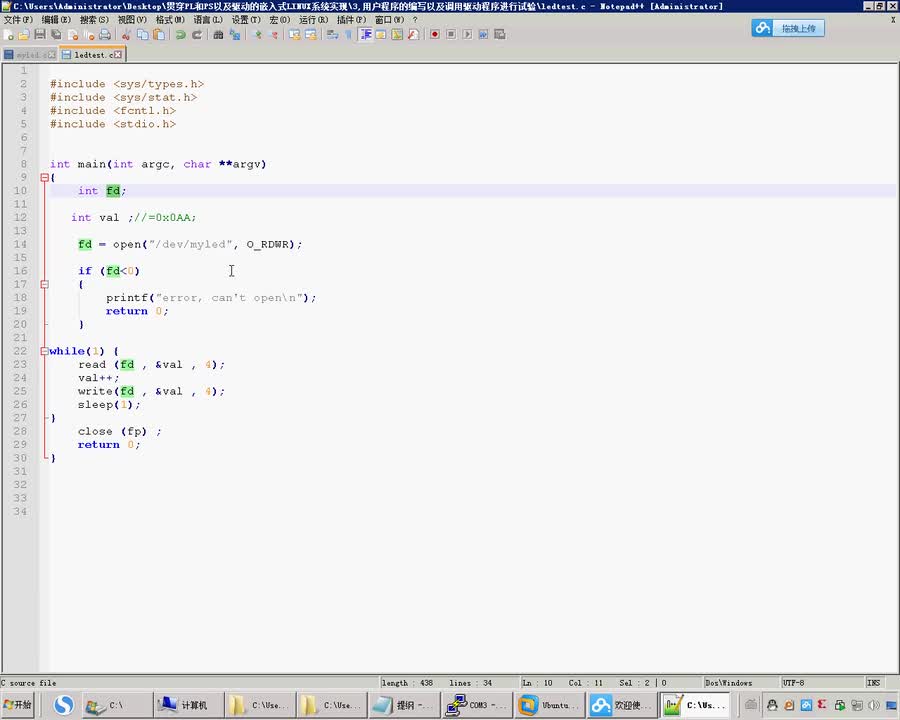

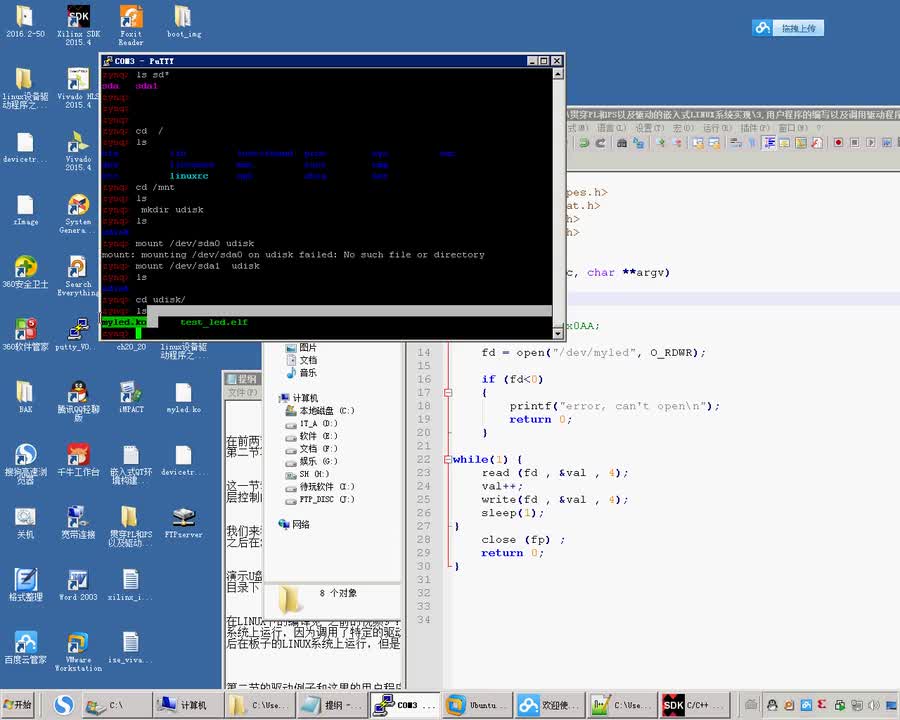

1157 Linux下的按键输入驱动开发模板一文中介绍了基本的按键输入捕获流程,这里将进一步介绍如何使用中断的方式来驱动按键,同时通过定时器实现按键消抖功能,应用程序读取按键值并通过终端打印出来

2022-07-29 08:59:43 1321

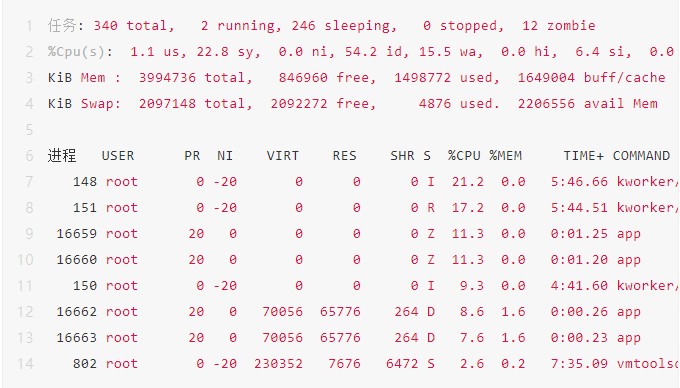

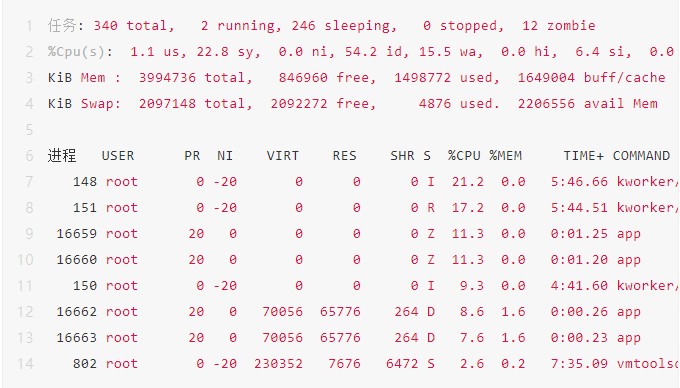

1321 文章对 Linux 系统下进程的几种状态进行介绍,并对系统出现大量僵尸进程和不可中断进程的场景进行分析,使用常用的几种工具进行问题分析定位。

2022-11-24 16:15:11 14506

14506

`基于紫金桥跨平台跨平台实时数据库,可Linux系统下快速实现一个监控系统。1、组态流程和传统windows组态差不多,所以上手很快。2、不仅软件支持跨平台,工程也支持跨平台,windows

2019-12-23 15:46:41

视频监控和家电控制一、视频监控基础1、摄像头2、v4l23、Linux下的摄像头使用流程4、烧写程序到开发板5、运行程序 (先插上摄像头)二、视频监控功能1、监控源码分析2、图片抓拍功能实现3、抓拍

2022-02-16 07:19:22

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档目录一、总览二、实战效果1.PL 写数据给PS效果2.PS写数据给PL效果总结前言没看过上一篇的去看一下上一章节对AXI_Lite在

2022-01-10 08:00:55

UARTO作为PS端调试串口。 CON10通过RS232收发器SIT3232EEUE引出PL端串口(EMIO UART1),TX和RX引脚 分别为Y12、Y3,电平为3.3V. 管脚约束可查看案例&

2024-07-25 16:14:10

Mini Linux EMMC

2023-03-28 13:06:25

我想用 uIO-Stick链接 RX P1.1TX P1.0 下载程序。型号是TLE9869QX 。我用uIO-Stick链接不了是为什么?请大师指导一下 谢谢。

2024-02-02 08:33:19

。1 axi_gpio_led_demo案例1.1 案例功能案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI GPIO IP核,IP核再根据命令控制评估底板PL端LED5的状态图

2021-05-28 14:28:28

我们现在遇到一个问题,我们申请了 GPIO_0_14下降沿中断,但是进中断函数后,我们获取IO的状态并打印的时候,发现值为1,下降沿中断本应该为零才对,我们给GPIO_0_14低电平时间约为

2018-06-21 06:29:03

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

的PL中断,所以应该将util_vector_logic IP配置成反相器,宽度设计成1)3、AXI_GPIO(当然也可以采用EMIO的方式)配置PS,修改端口名字,配置好的工程如下:综合分配管脚生成

2015-06-12 11:45:30

一直纠结于怎样给PL提供时钟,zynq开发不同于一般的FPGA开发。其中时钟和复位问题就是相当重要的问题,有两种方式可以为PL部分提供时钟和复位:1、PS部分可以产生四个毫无关系的输出时钟和复位信号

2015-06-08 17:29:32

本帖最后由 blackroot 于 2015-6-10 17:06 编辑

一直没搞懂PS怎样给PL提供复位和时钟,今天这个问题终于解决了~~~~~用一个简单的例子来说明一下,怎样使用PS输出

2015-06-10 16:59:53

在板子上除了给PS(33.33 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。为了让PL部分正常工作,一种方法是使用接口板从外部

2015-06-01 11:54:12

使用uio Stick v2(不是uio Stick),通过config wizard for smart power switches工具控制SPOC系列智能功率开关,使用时通过updata

2024-01-26 07:06:56

典型应用领域

axi_uart_demo案例演示案例说明PS端通过AXI4-Lite总线发送命令至PL端AXI Uartlite IP核,IP核根据命令控制评估底板PL端串口进行数据收发。案例测试将PC

2024-08-22 14:04:12

中断在单片机程序中为什么如此重要?对linux下中断程序的格式有什么要求?如何去编写linux下的中断服务程序?有哪些步骤?

2021-07-08 06:01:50

linux下查看中断请求记录。通过cpu的中断请求的响应,可以看出cpu都在为哪些设备干活,干的活有多少量等信息。

2019-07-23 06:06:52

而无法再操作。我的目标是使用一个仅包含PL部件设计的比特流,不需要任何PS描述或PS和PL之间的连接来配置PL,而linux(PS)运行良好。实际上,我想设计一个系统来逐个配置来自不同用户的许多不同位

2020-05-21 07:07:50

我的设备是zedboard702,我知道如何在使用PS和PL时使用SDK生成启动映像和程序闪存。问题是我只是使用PL,现在如何编程flash?

2019-09-30 09:43:18

亲爱的大家,我只是想知道如何找到Ultrascale +的PL和PS的地址转换(映射方案到DRAM-我的意思是哪个等级,库等)?

2019-10-16 08:35:37

大家好,我已经在PS中产生了一个100Mhz的时钟信号,并使其在外部被PL接收。我使用了原始的ODDR但没有成功我可以从引脚输出100 Mhz时钟。有什么建议么??以上来自于谷歌翻译以下为原文

2019-02-22 09:09:05

为什么一个简单的程序运行不了,请求帮忙看一下。做个LED流水灯,是想用PS部分生成100MHz的频率,然后用这个频率来实现PL部分三色led移位,但是好像PS部分有问题,不知道怎么配置了。这是PS

2016-01-02 21:35:38

在Linux下之前是通过lsusb查看一些信息,但有时候也需要监控到USB数据,故请教一下各位有没有Linux下的USB监控软件,或者一些监控的方法。谢谢各位。

2024-01-24 06:52:37

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

2020-08-03 15:53:30

你好,我想知道从ADC到PL的群延迟,直到它通过ZCU111上的DAC转换回来。到目前为止,我们找不到任何可用的DOC。亲切的问候斯蒂芬

2019-10-23 06:10:13

的Linux的xdevcfg设备来编程PL部件。有趣的解决方案是通过在同一芯片的PS部分运行的XVC远程调试基于Zynq的设计。假设我将XAPP1251中描述的AXI-JTAG控制器添加到我的设计中,是否

2020-07-30 13:51:19

pl2303 linux驱动,支持linux.

2008-10-15 14:26:35 6

6 IC-PL7501,带输入可调过流保护,外围简单,SOP8封装。PL7501可应用于5V输入,给双节锂电池充电电路。5V输入,给两节锂电池串联的专用充电IC-PL750

2022-05-19 13:09:14

linux 中断和设备驱动

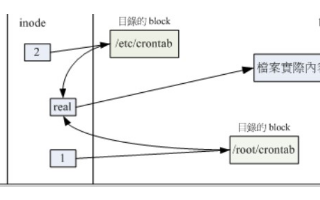

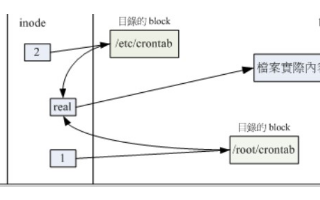

本章介绍L i n u x内核是如何维护它支持的文件系统中的文件的,我们先介绍 V F S ( Vi r t u a lFile System,虚拟文件系统),再解释一下L i n u x

2010-02-09 14:13:28 24

24 Linux 2.6 中断处理原理简介

中断描述符表(Interrupt Descriptor Table,IDT)是一个系统表,它与每一个中断或异常向量相联系,每一个向量在表中存放的是相应的中断或

2010-02-05 10:52:28 940

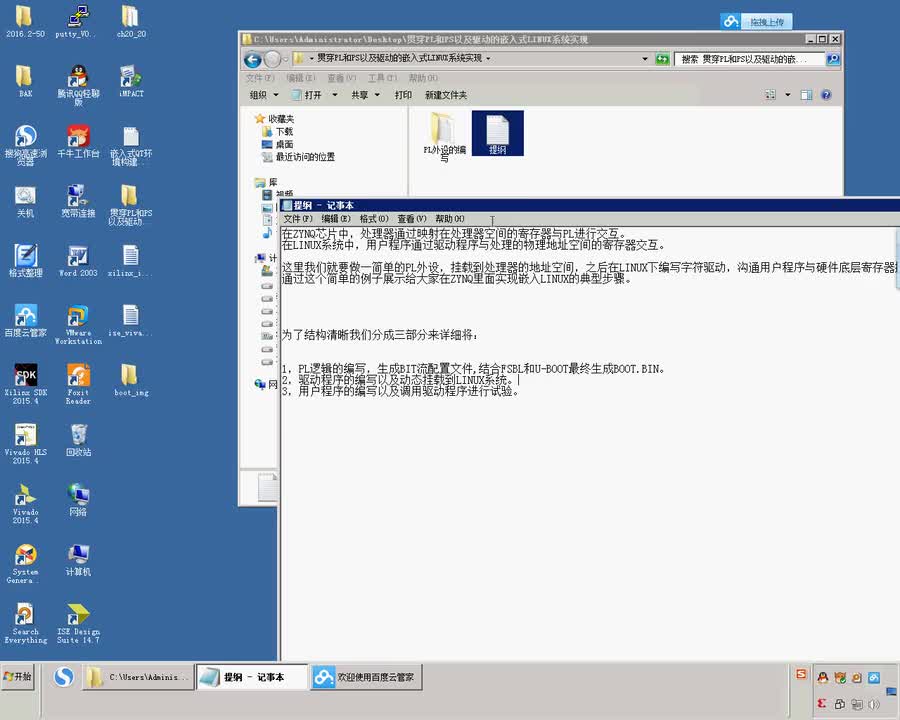

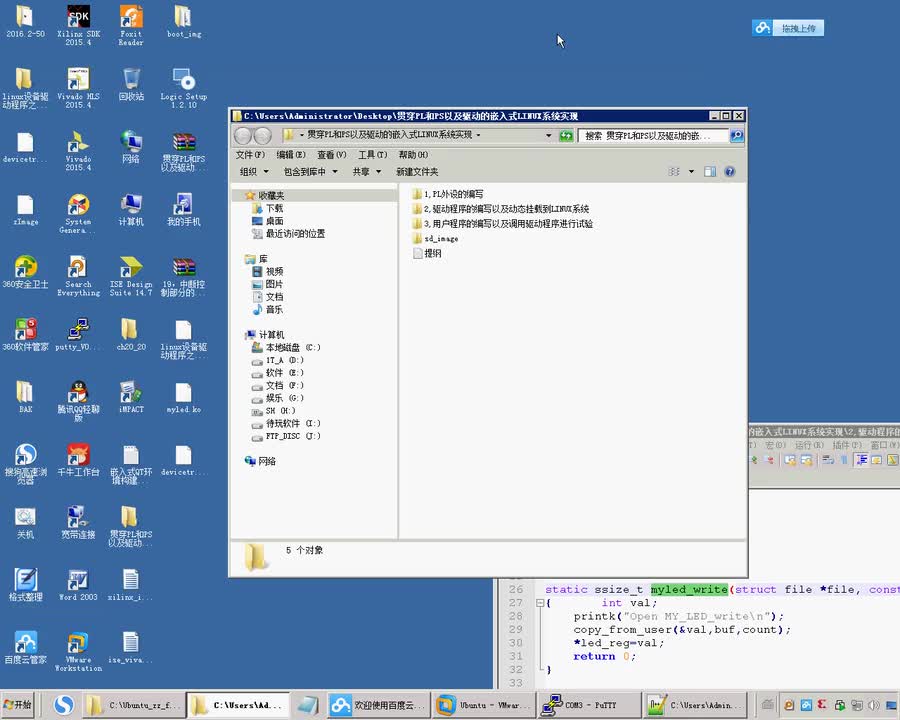

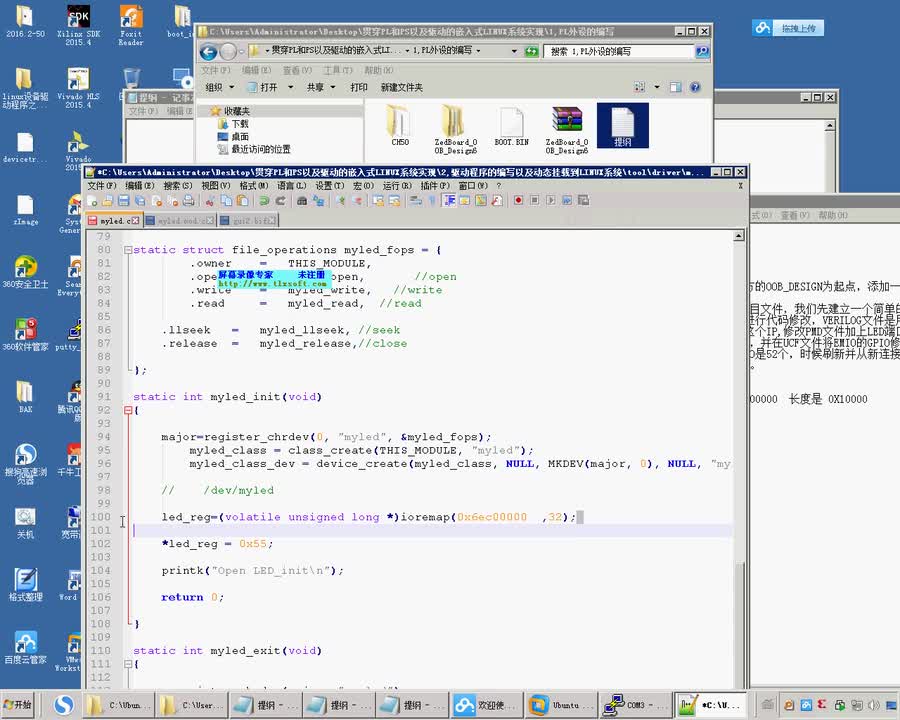

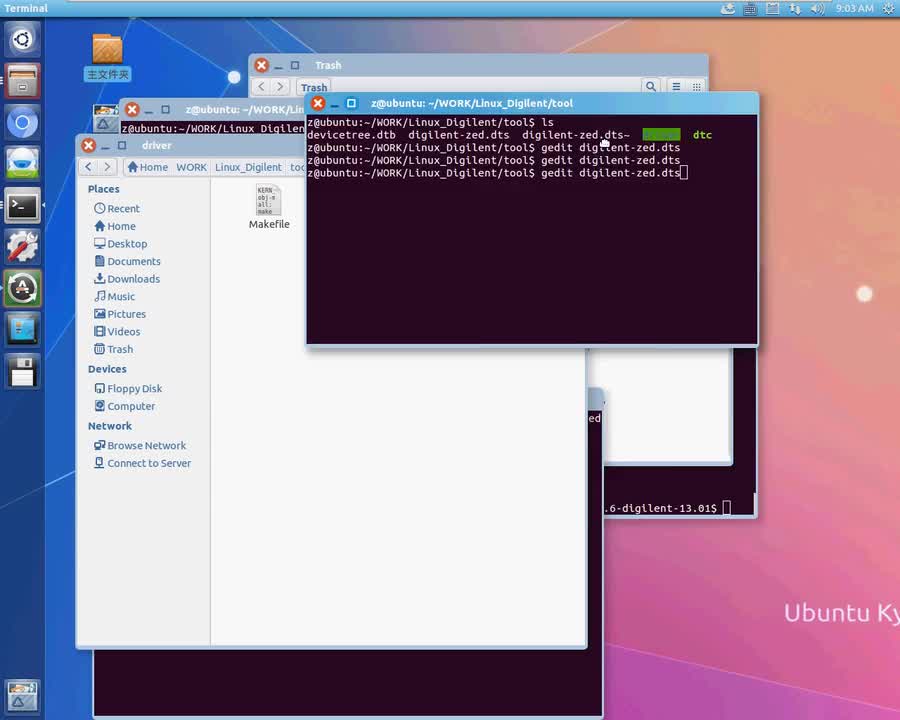

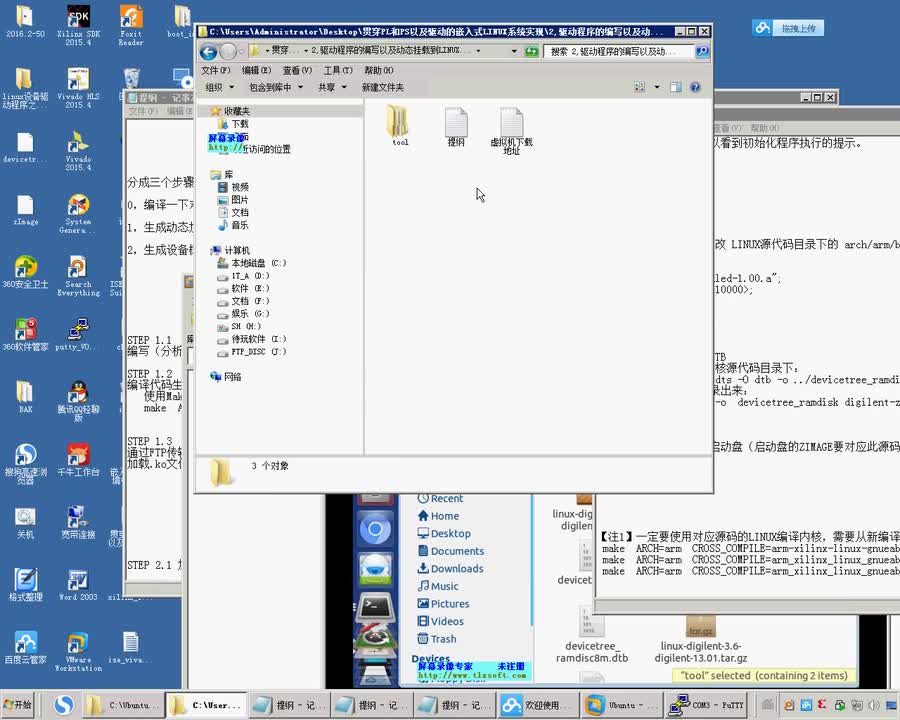

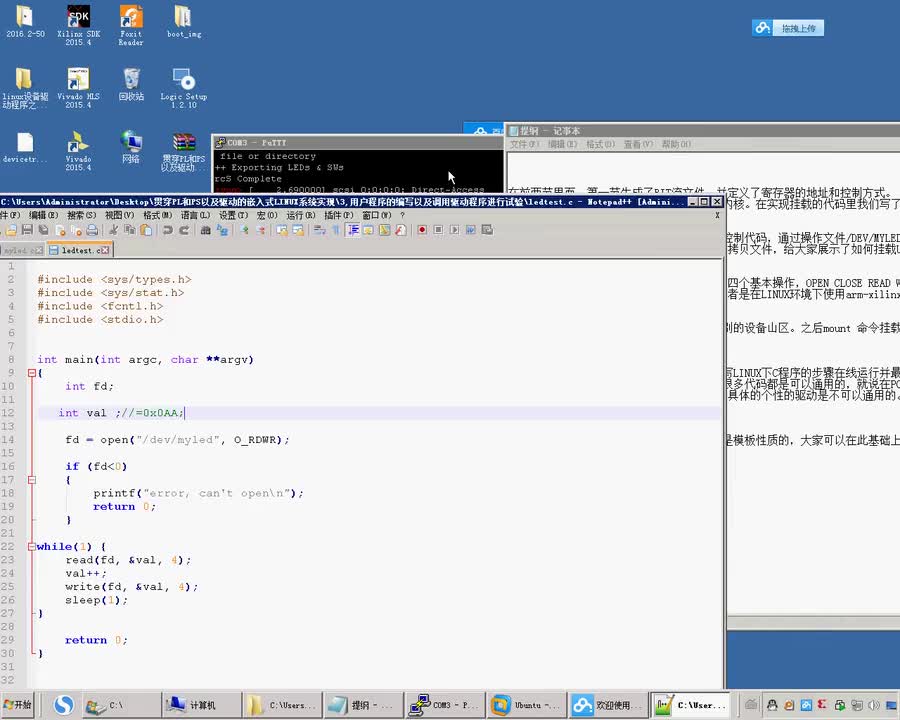

940 本文通过实例详细解析如何利用Zynq-7000的PL和PS进行交互。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22 58287

58287

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1、传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送; 2、PL端接口为FIFO接口; PS到PL的数据传输流程: PS

2017-02-08 01:00:11 2324

2324

因为MicroZed是个低成本的开发套件,所以在板子上除了给PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。

2017-02-09 14:16:11 4978

4978

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 1426

1426

构建SoC系统,毕竟是需要实现PS和PL间的数据交互,如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,本节研究如何再实现PL端对DDR3的读写操作。

2017-09-18 11:08:55 23

23 本文从Linux内核几种软中断机制相互关系和发展沿革入手,分析了这些机制的实现方法,给出了它们的基本用法。 软中断概况 软中断是利用硬件中断的概念,用软件方式进行模拟,实现宏观上的异步执行效果。很多情况下

2017-11-02 11:01:58 0

0 通过综合采用用户级别的top、ps等系统工具以及Linux内核防护技术,我们可以从用户/内核两个层次全方位地保护Linux系统中重要系统进程以及用户进程的安全性,从而达到保护Linux系统安全的目的

2017-11-06 11:20:01 0

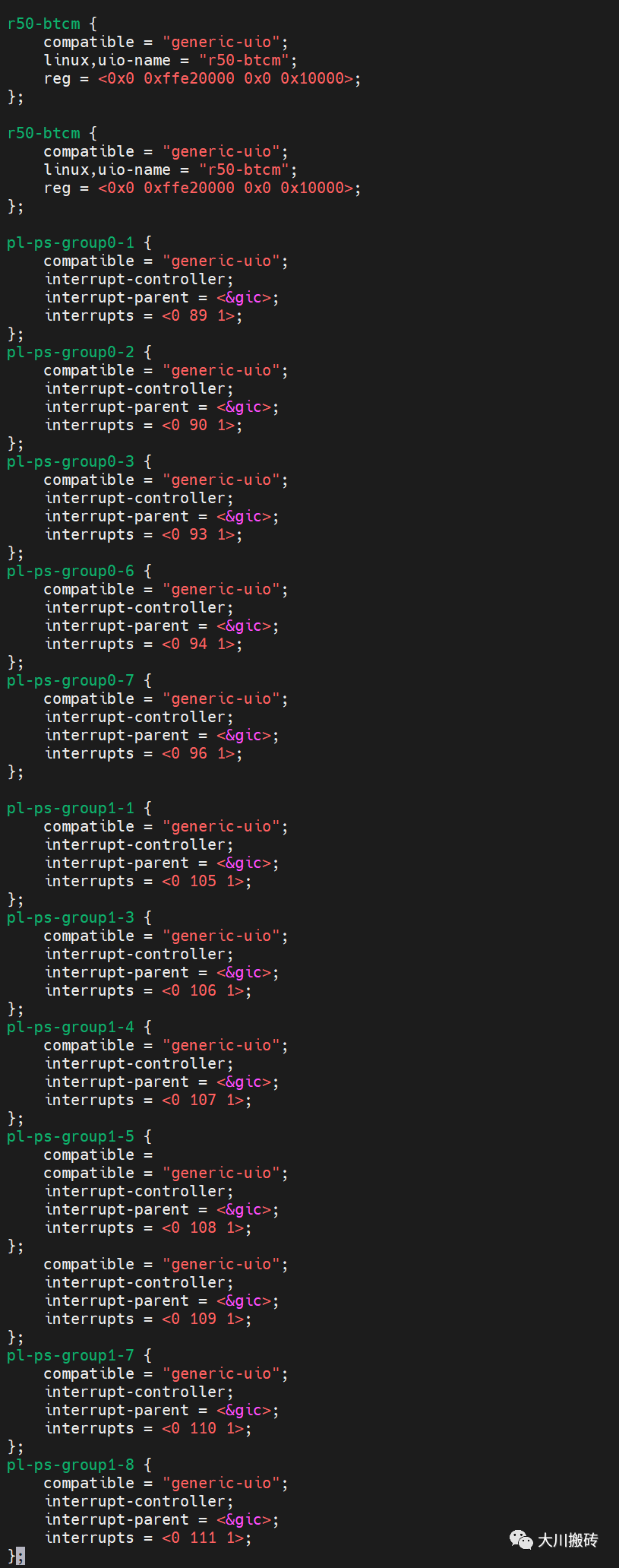

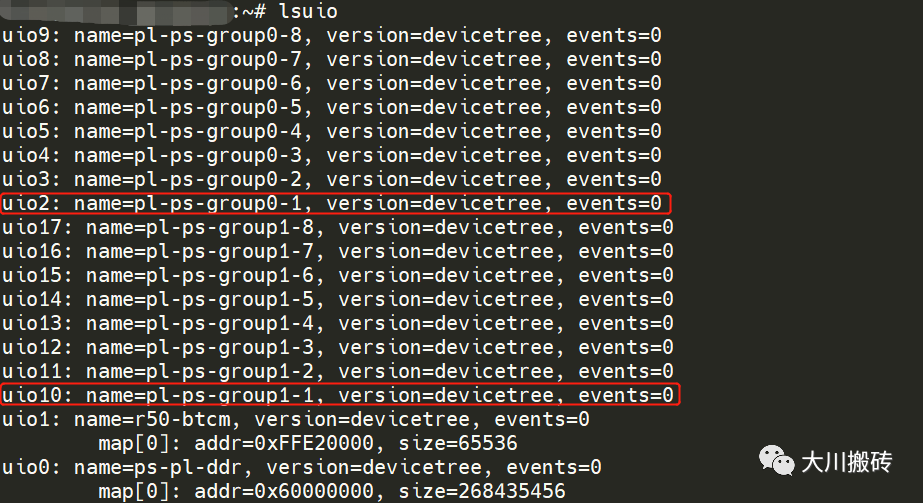

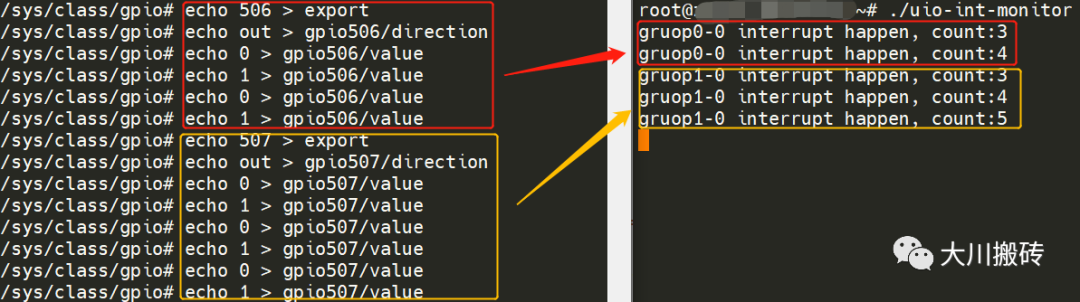

0 本实验工程利用Xilinx Zynq UtralScale+(MPSoC)ZCU102嵌入式评估板上实现多个UIO,借助Xilinx的工具完成硬件工程和linux BSP的开发,最后通过测试

2017-11-15 14:46:59 15723

15723

本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

2018-03-21 14:55:00 3684

3684

zedboard可以将逻辑资源和软件分别映射到PS和PL中,这样可以实现独一无二和差异换的系统功能,主要分为两大部分,处理系统和可编程逻辑。以及二者之间的互联特性。这篇笔记主要记录zedboard的大体架构。

2018-06-26 06:24:00 7451

7451 GPIO应用是嵌入式设备最基本的应用之一, 本文就基于Embedded Linux系统演示开发GPIO中断以及输出相关的基本应用示例.

2019-04-29 15:48:20 2994

2994

中断是指在CPU正常运行期间,由于内外部事件或由程序预先安排的事件引起的CPU暂时停止正在运行的程序,转而为该内部或外部事件或预先安排的事件服务的程序中去,服务完毕后再返回去继续运行被暂时中断的程序。Linux中通常分为外部中断(又叫硬件中断)和内部中断(又叫异常)。

2019-05-05 15:30:38 930

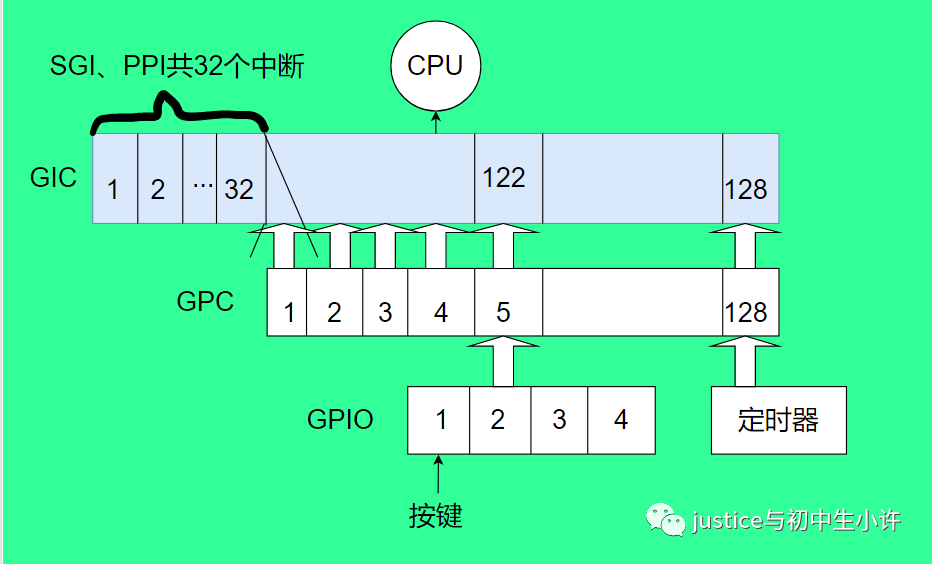

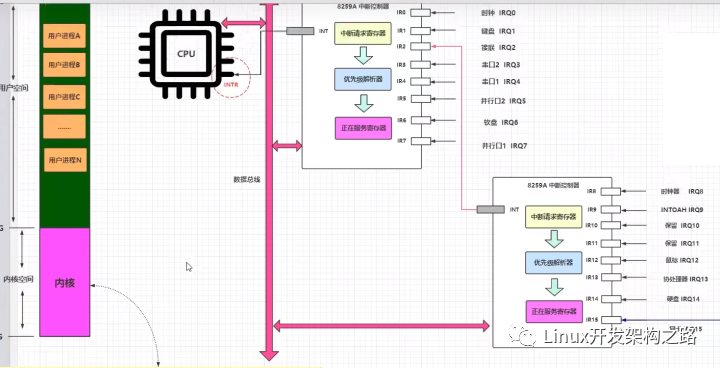

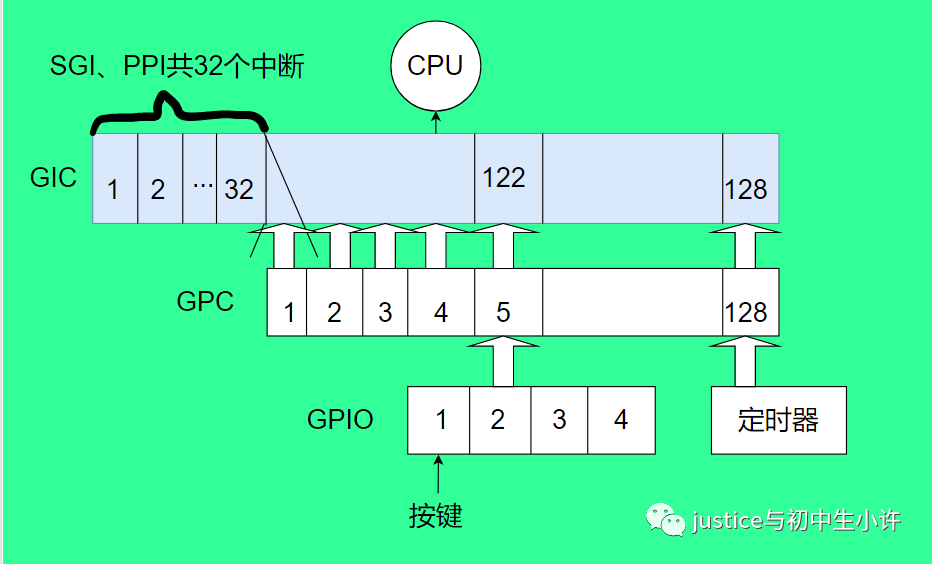

930 在硬件上,中断源可以通过中断控制器向CPU提交中断,进而引发中断处理程序的执行,不过这种硬件中断体系每一种CPU都不一样,而Linux作为操作系统,需要同时支持这些中断体系,如此一来,Linux中就

2019-05-08 13:49:02 917

917 本文档的主要内容详细介绍的是Linux下的51单片机简单的外部中断实验的资料电路图及程序免费下载

2019-08-09 17:33:00 0

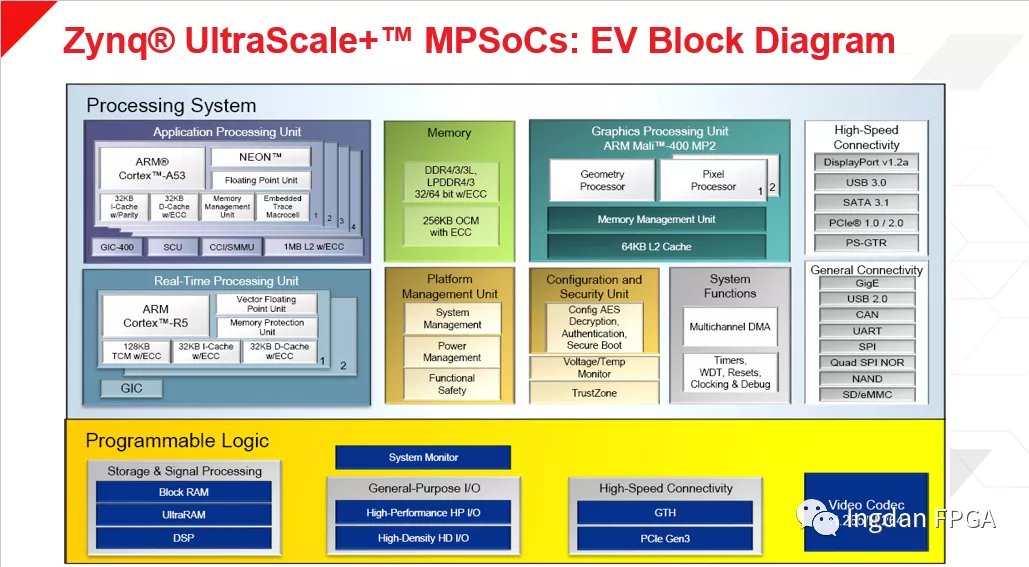

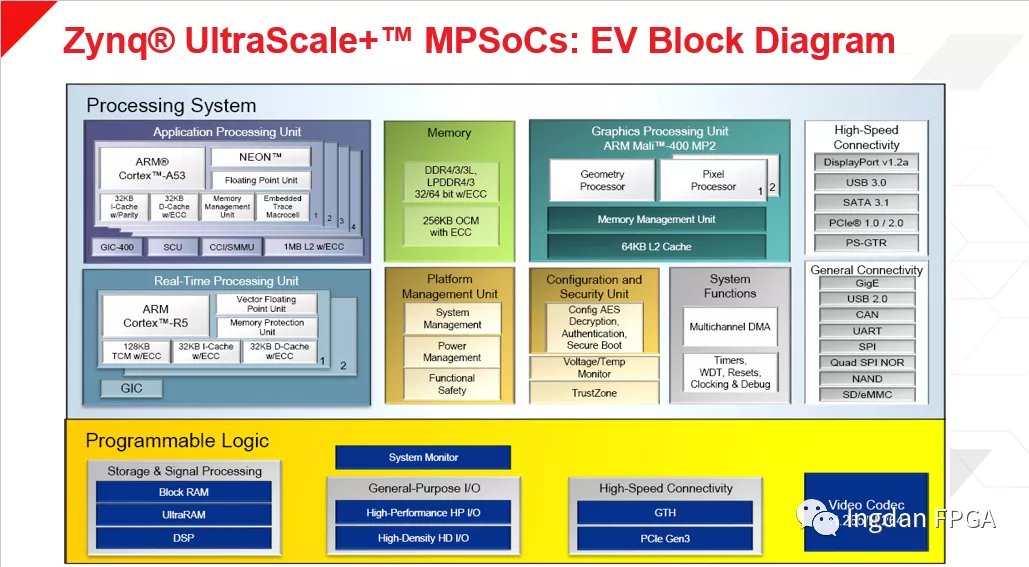

0 MPSoC是Xilinx基于16nm工艺推出的异构计算平台,由于灵活、稳定,在业界得到了广泛的使用。异构计算是一个比较新的领域,需要协调硬件设计、逻辑设计、软件设计,对工程师的要求很高。实际设计过程中,很多工程师对实现PS/PL之间的数据交互感到头疼。

2020-09-15 09:27:00 12835

12835

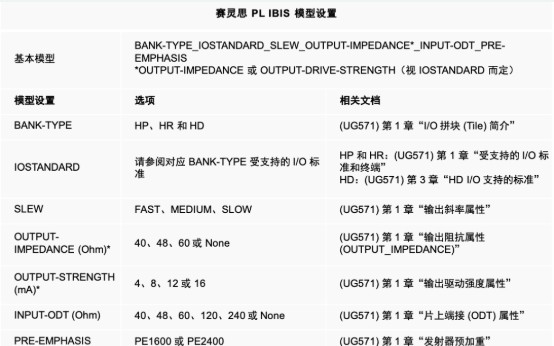

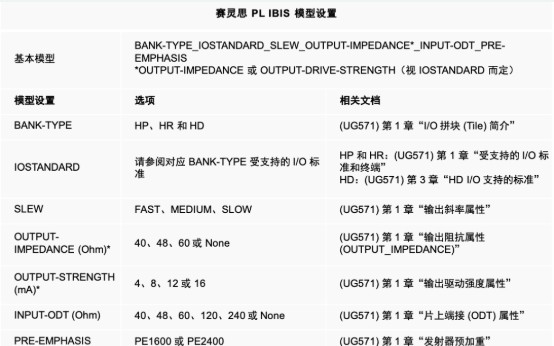

。 本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。 本文主要分 3 个部分: PL I/O 标准 PS MIO

2020-10-15 18:29:15 3123

3123

Linux嵌入式设计中最基本的任务之一是创建用户应用程序。 在本篇博文中,我们将探讨如何在 Vitis 中使用 UIO 驱动框架创建简单的 Linux 用户应用。 1 硬件设计 本次

2020-11-20 14:05:34 5335

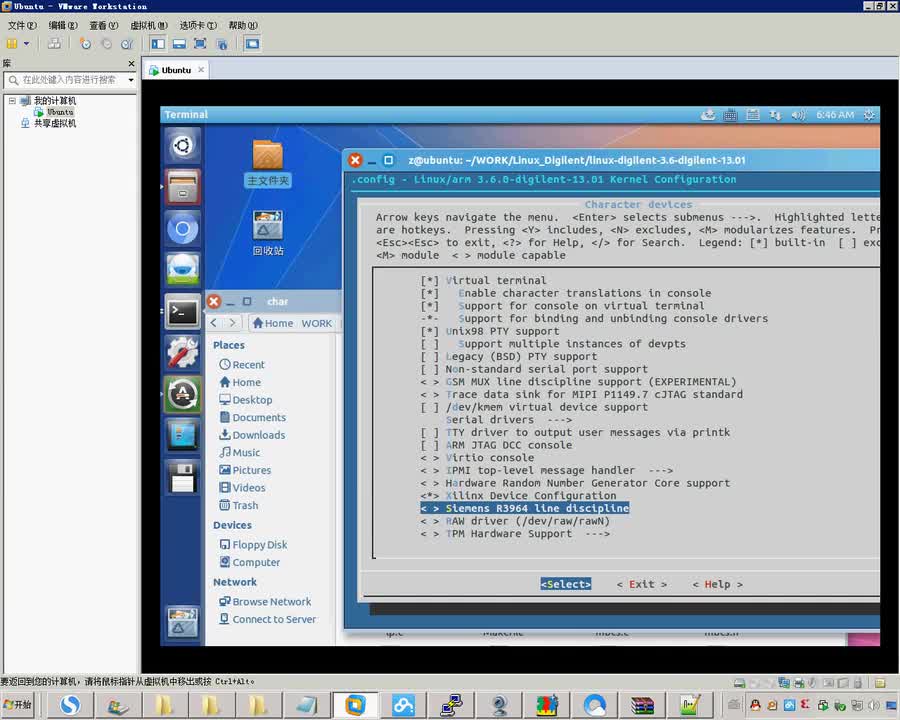

5335 目录1. MPSoC的中断处理介绍 2. 扩展PL中断 3. 扩展AXI Intc中断 3.1. AXI Intc PL连接 3.2. AXI Intc Device Tree 3.3. AXI

2021-05-07 15:34:15 4690

4690 刚学ZYNQ的时候,看到里面反复提到PS和PL,还以为PS是PhotoShop的意思,PL是哪种型号的简称。 稍微了解之后才知道,ZYNQ是ARM和FPGA的组合,PS是programming

2021-06-18 16:09:46 11177

11177 用过STM32的大概都知道,基本每个GPIO管脚都支持中断模式,这样在检测外部插入一个硬件设备时,通过GPIO管脚电平中断就非常方便。那么AM3354的片子是否支持GPIO管脚电平中断呢?答案是肯定

2021-11-01 16:57:32 4

4 做个STM32开发的都知道,通过程序配置让普通的GPIO口具有中断功能。这样对于设备检测某些硬件的自动设备要方便的多。那么在嵌入式的Linux是否具有这样的功能呢?答案是肯定的,下面我们就来介绍一下

2021-11-01 17:37:40 6

6 大多数 Linux 用户使用预装的默认系统监控工具来检查内存、CPU 使用率等。在 Linux 中,许多应用程序作为守护进程在系统后台运行,这会消耗更多的系统资源。在 Linux 中,您可以使用各种

2022-06-16 12:11:50 2164

2164 部分 ZynqUltraScale+MPSoC的可编程逻辑(PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自PL 或PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间

2022-08-02 16:48:15 4463

4463

MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线

2022-08-02 09:45:03 1412

1412 本文主要讲解在 PL 中从 IP 核到 PS 之间需要完成含超 16 次中断的布线的情况下,该如何使用 AXI Interrupt Controller (INTC)。其中使用的AMD Xilinx外设包括 Vivado 设计中的 GPIO、IIC、UART 以及定时器。

2022-08-24 09:21:56 5754

5754 在无 JTAG 的模式下,Zynq 是通过片上CPU完成对芯片的配置,也就是PS和PL的配置是通过 PS 处理器 ARM 核来实现的。需要注意的是,与传统的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持从 PL 端进行直接启动配置的,一定要通过 PS 部分来完成。

2022-10-19 09:11:55 2023

2023 电子发烧友网站提供《将Zynq PS和PL与内存映射寄存器集成.zip》资料免费下载

2022-12-06 15:14:29 2

2 UIO(Userspace I/O)是运行在用户空间的I/O技术,Linux 系统中一般的驱动设备都是运行在内核空间,应用程序在用户空间调用即可。UIO 则是将驱动的小部分运行在内核空间,在用户空间实现驱动的绝大多数功能,使用 UIO 可以避免设备的驱动程序需要随着内核的更新而更新的问题。

2023-01-19 16:35:00 12528

12528

S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

2023-02-01 15:36:53 4694

4694 在嵌入式系统中,经常会用到gpio外部中断来获取外部事件,比如按键、传感器、网络通信等等。一般中断都会绑定一个中断回调函数,来执行产生中断后的一些任务。Linux的中断是操作系统管理的资源,需要在内核层配置中断以及绑定回调函数。

2023-03-24 11:27:32 4499

4499

当有一种情况,我们需要像上面第四点中提到的通过CPU和内存的使用率来筛选进程,并且我们希望结果能够每秒刷新一次。为此,我们可以将ps命令和watch命令结合起来。

2023-04-04 09:23:26 1410

1410 在一个系统中,中断时常发生,而且线程调度也是由一个硬件定时器时时刻刻发出中断来支撑的。可以说中断就是linux系统的灵魂。

2023-06-23 14:22:00 1018

1018

上篇文章我们从内核工程师的角度剖析了内核的外部中断,这节我们从BSP工程师的角度剖析一下外部中断。

2023-06-23 15:19:00 865

865

电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案应用笔记.pdf》资料免费下载

2023-09-15 10:29:25 3

3 电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案.pdf》资料免费下载

2023-09-15 10:05:18 2

2 前言本文主要介绍PS+PL端异构多核案例的使用说明,适用开发环境:Windows7/1064bit、XilinxVivado2017.4、XilinxSDK2017.4。案例位于产品资料“4-软件

2023-01-03 15:50:37 19

19 LInux 操作系统中断 什么是系统中断 这个没啥可说的,大家都知道; CPU 在执行任务途中接收到中断请求,需要保存现场后去处理中断请求!保存现场称为中断处理程序!处理中断请求也就是唤醒对应的任务

2023-11-10 11:29:49 1367

1367

今天浩道跟大家分享运维工作中,Linux下常见的十几款CPU监控工具,你可能只会用到其中某些,但是个人觉得作为一个资深运维,你要知道有这些工具可以监控CPU。

2024-01-22 09:19:14 3251

3251

ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之间的数据交互是系统设计的核心。

2025-10-15 10:33:19 738

738

电子发烧友App

电子发烧友App

评论