本文主要介绍Zynq UltraScale+ MPSoC系列器件的PS-PL之间互连的AXI总线接口。

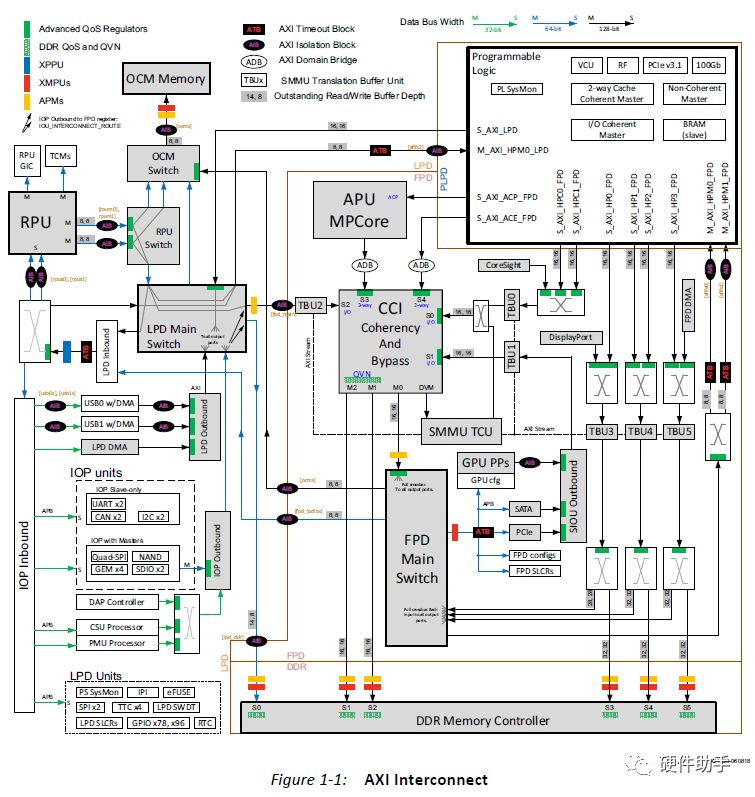

Zynq MPSoC系列器件的AXI总线结构如下图所示:

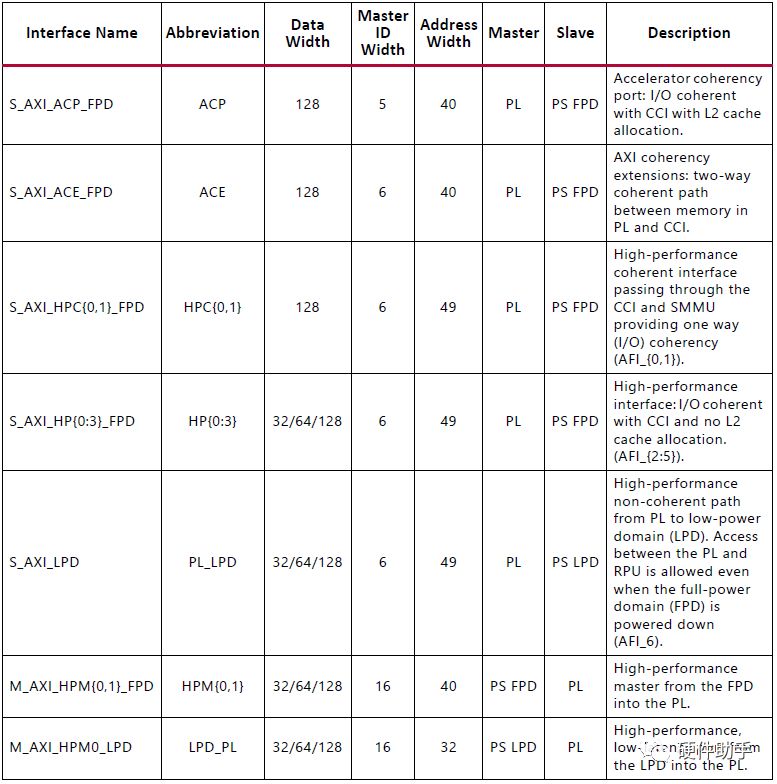

PS侧可以使用PS-PL AXI接口调用PL侧的硬件加速器等接口。这种互连属于高带宽、低延迟的连接方式。 Zynq MPSoC提供了12个PS-PL AXI端口,详细如下表所示:

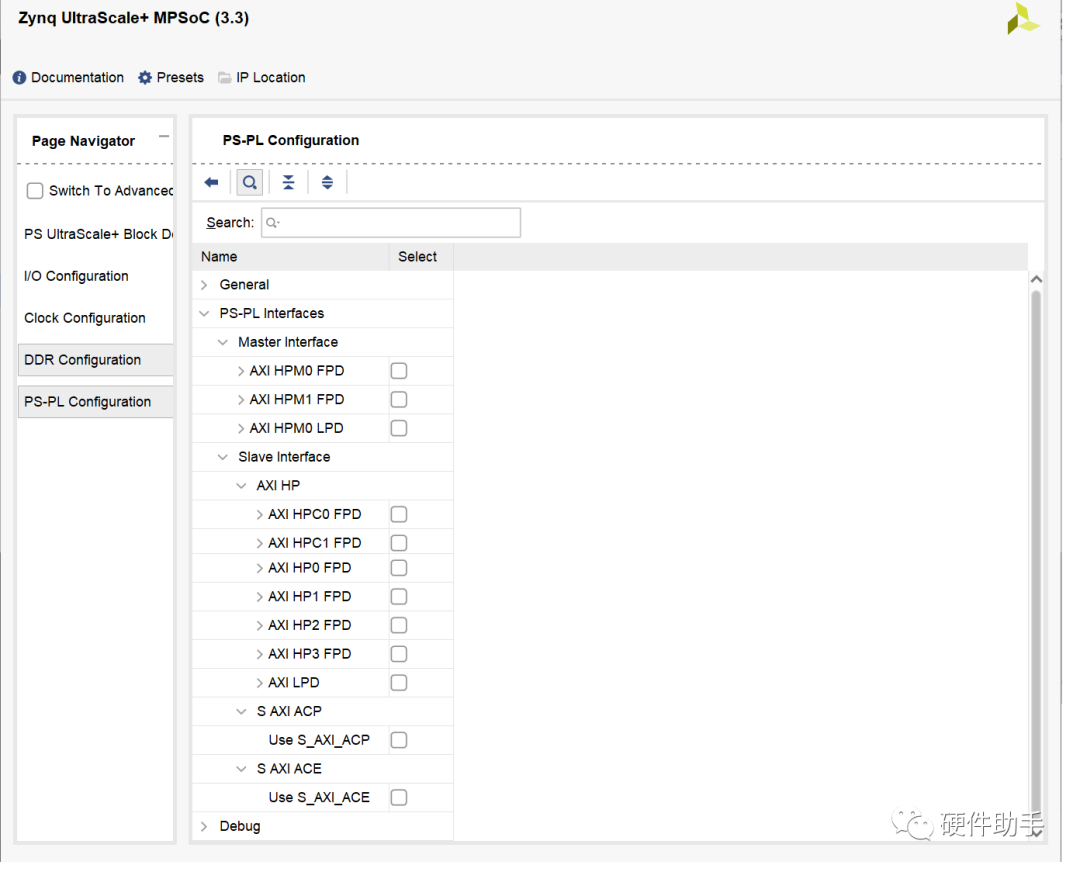

vivado里面也是12个PS-PL Interfaces可以使用。

这些PS-PL接口的主要特性如下:

High-performance AXI4 interface with FIFO support in the PS.

Selectable native PL data bus width support (32/64/128).

Independent read and write clocks.

Three interfaces support I/O coherency through the cache-coherentinterconnect (CCI).

System Memory Management Unit (SMMU) for PS bound transactions (virtual to physical address translation).

Dedicated low-latency path between the low-power domain (LPD) and PL.

Accelerator coherency port (ACP) interface for I/O coherency and allocation into the APU’s L2 cache.

AXI coherency extensions (ACE) interface for full coherency. Usable as ACE-Lite for I/O coherency.

32 bits for general-purpose input and 32 bits for output from the platformmanagement unit (PMU) for communication with the PL.

16 shared interrupts and four inter-processor interrupts.

Dedicated interfaces from the gigabit Ethernet controller (GEM) and the Display Port protocol.

Other PS-PL interfaces, such as extended MIO and PL clocks.

S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

5

ACE(AXI一致性扩展)协议扩展了AXI4协议,并支持硬件一致性缓存。S_AXI_ACE_FPD使用《AMBA AXI and ACE Protocol Specification》中描述的ACE协议。S_AXI_ACE_FPD是一个PL作为master与PS中的CCI-400相连的接口。它能够支持PS和PL中的硬件块之间的完全一致性(双向)。与AXI接口相比,ACE协议使用了五个额外的通道,三个通道用于监听,两个用于应答。此接口允许PL将其缓存存储在FPGA的专用存储资源或逻辑结构中。然后,可以使用ACE接口与PS中的其他相干主机和PL中的相干主机保持一致。尤其是APU可以监听PL缓存(使用S_AXI_ACP_FPD接口这是不可能实现的)。由于S_AXI-ACE-FPD端口直接连接到CCI-400总线上,而不会通过SMMU,因此,它无法利用PS中的物理和虚拟地址映射。

MPSoC有六个PL侧高性能(HP)AXI主接口连接到PS侧的FPD(PL-FPD AXI Masters),可以访问PS侧的所有从设备。这些高带宽的接口主要用于访问DDR内存。有四个HP AXI主设备接口表示为S_AXI_HPn_FPD,两个高性能一致性(HPC)AXI主设备接口表示为S_AXI_HPCn_FPD。

每个S_AXI_HPn_FPD接口都通过几个AMBA switch连接到DDR内存控制器。它们之间的特性如下:

S_AXI_HP0_FPD-此接口与PL侧的DP口共享其在DDR内存控制器上的端口,这些接口连接到DDR内存控制器的端口3。

S_AXI_HP{1,2}_FPD-这两个端口共享DDR内存控制器的端口4,且能独占该端口。这种独占性提供了与DDR内存的高吞吐量、低延迟通信。

S_AXI_HP3_FPD-此接口与FPDMA控制器共享DDR内存控制器上的端口。

所有的六个HP AXI主接口都通过PS中的SMMU。SMMU能够使用物理和虚拟地址转换。这使得每个接口都支持与APU的虚拟化。

S_AXI_LPD是连接PL和LPD之间的一个高性能的AXI接口。它能够低延迟地访问OCM和TCMs。当FPD断电时,这个接口特别有用,因为它仍然能够为PL提供对LPD的高性能访问。但是,由于互连的拓扑结构,这个端口与DDR控制器的的访问延迟比较大。

在FPD和PL之间有两个高性能通信接口,在LPD和PL之间有一个高性能通信接口,如下所示:

在FPD中,有两个到PL的接口:M_AXI_HPM0_FPD和M_AXI_HPM1_FPD。这些接口适合于为PS中的FPD主机提供对PL中的存储器的访问,以便能够传输大量数据。

在LPD中,有一个高性能从接口M_AXI_HM0_LPD。该接口适合于为PS中的LPD主机(例如LP-DMA)提供对PL中的存储器的访问,以便能够传输大量数据。这个接口是低延迟的,可以在FPD关机时访问。但由于路径中有一个ID转换器,APU无法访问此接口。

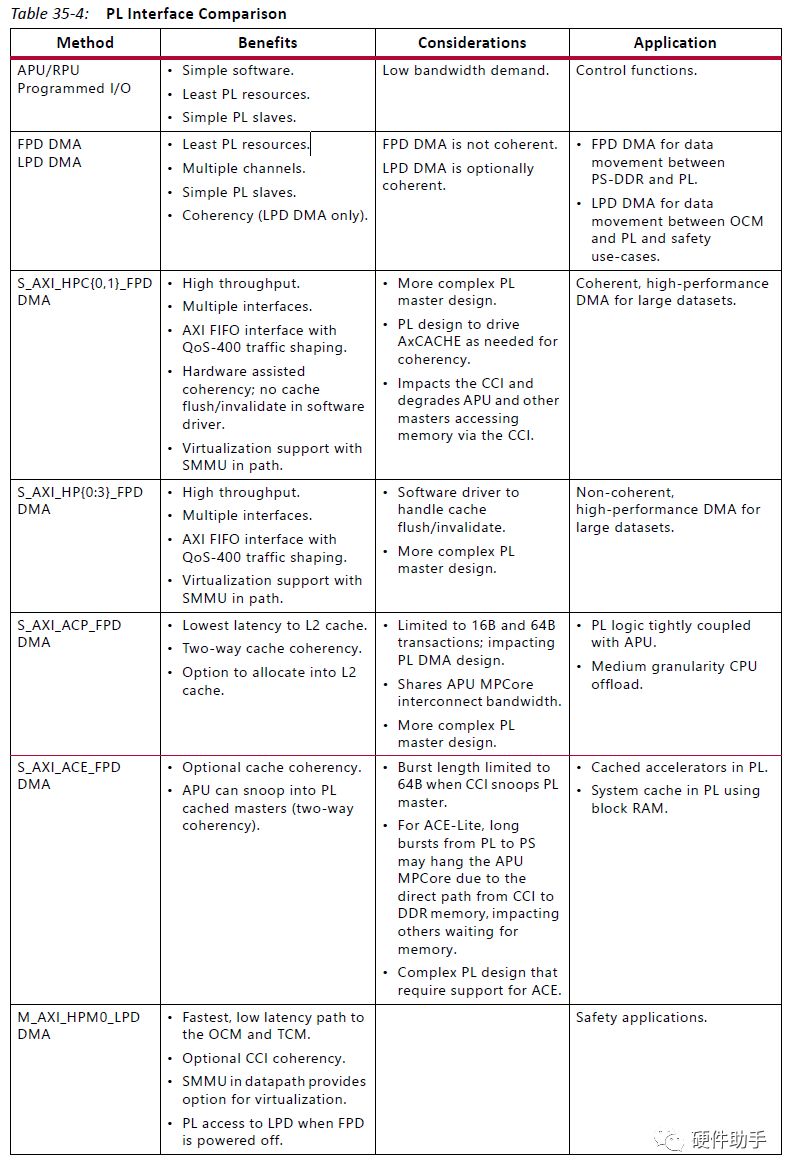

下面是这十二个接口的一个简单的比较:

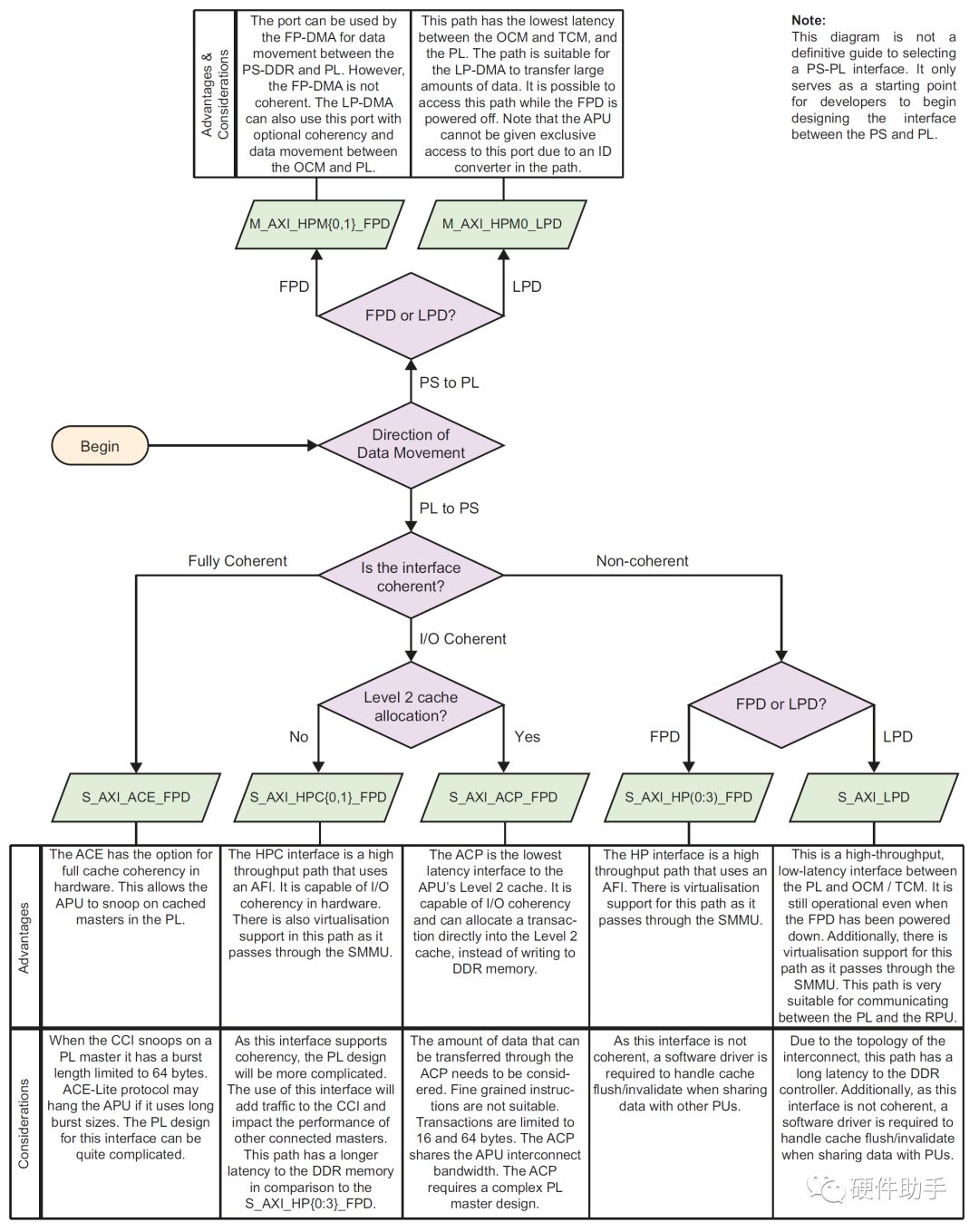

下面提供一个简单的选择流程,详细说明了使用Zynq MPSoC时选择PS-PL AXI接口的方法。其中包括使用每个接口的一些好处,以及在选择该接口时需要考虑的问题。

以上就是针对Zynq MPSoC的PS-PL AXI接口的简单介绍,使用时可以参考相关文档进行详细了解。

审核编辑 :李倩

-

FPGA

+关注

关注

1655文章

22287浏览量

630319 -

总线接口

+关注

关注

0文章

93浏览量

31346

原文标题:FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL读写PS端DDR数据

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM实现PS与PL交互

ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念

ZYNQ PS + PL异构多核案例开发手册之1axi_gpio_led_demo案例

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”

评论