在涉及Xilinx Zynq UltraScale+ MPSoC的项目中,实现设备间高速、低延迟的数据传输往往是核心需求之一。PCIe(尤其PS侧)结合DMA(直接内存访问)正是满足这类需求的理想技术方案。

2025-10-22 13:53:56 3397

3397

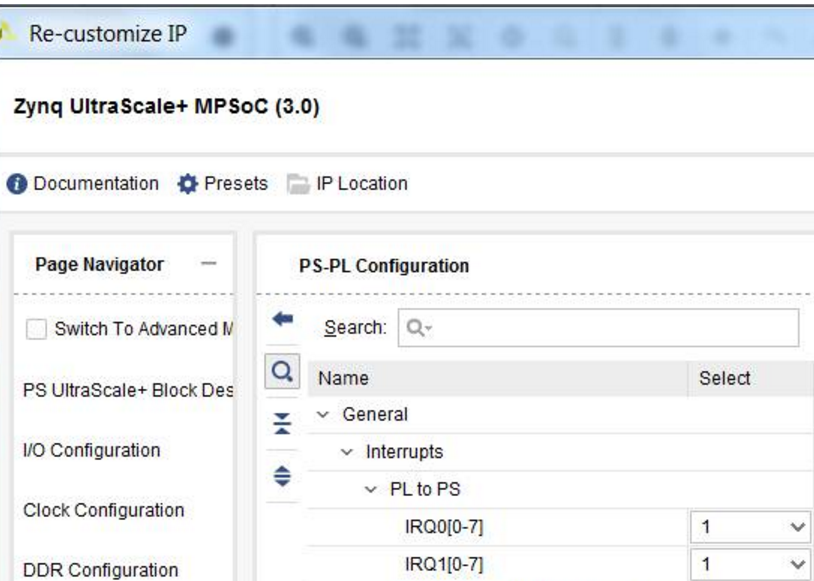

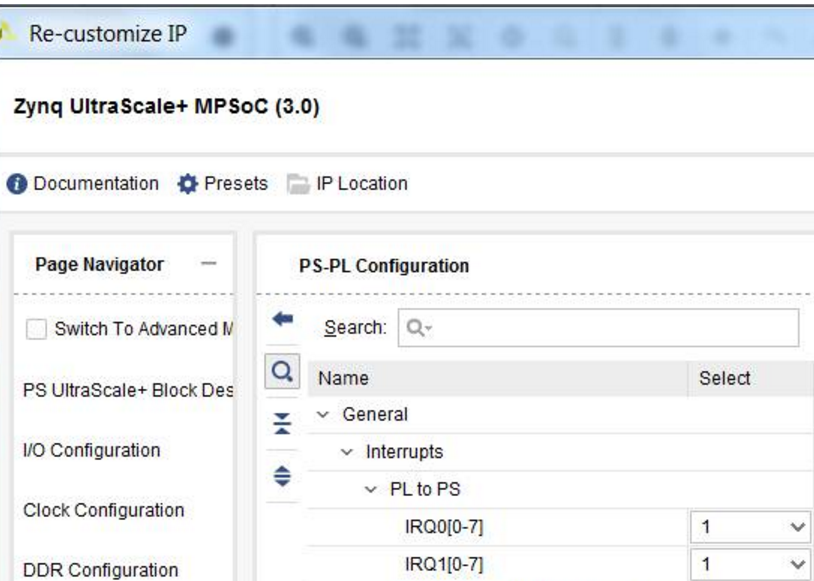

硬件连接MPSoC 可以接收两组来自 PL 的中断信号。在 Vivado 中,可以通过 PS-PL Conf

2017-09-28 06:39:00 9863

9863

。 Pynq降低了开发人员的门槛,但知其然也知其所以然,开发效率将会更高。因此,在进入PYNQ的python开发之前,我们先来学习ZYNQ的PL与PS开发,为接下来的学习提供良好的基础。 本部分的学习

2020-12-25 14:11:50 9769

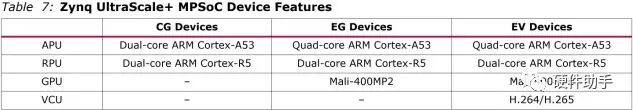

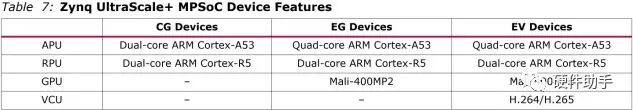

9769 本篇主要介绍ZU+系列MPSoC的外围接口,针对每个接口进行概述性介绍,后续会针对个别接口进行详细介绍原理图设计和PCB设计。 ZU+系列MPSoC的外围接口主要包括两部分:PL部分和PS部分。PL

2020-12-26 10:04:38 6135

6135

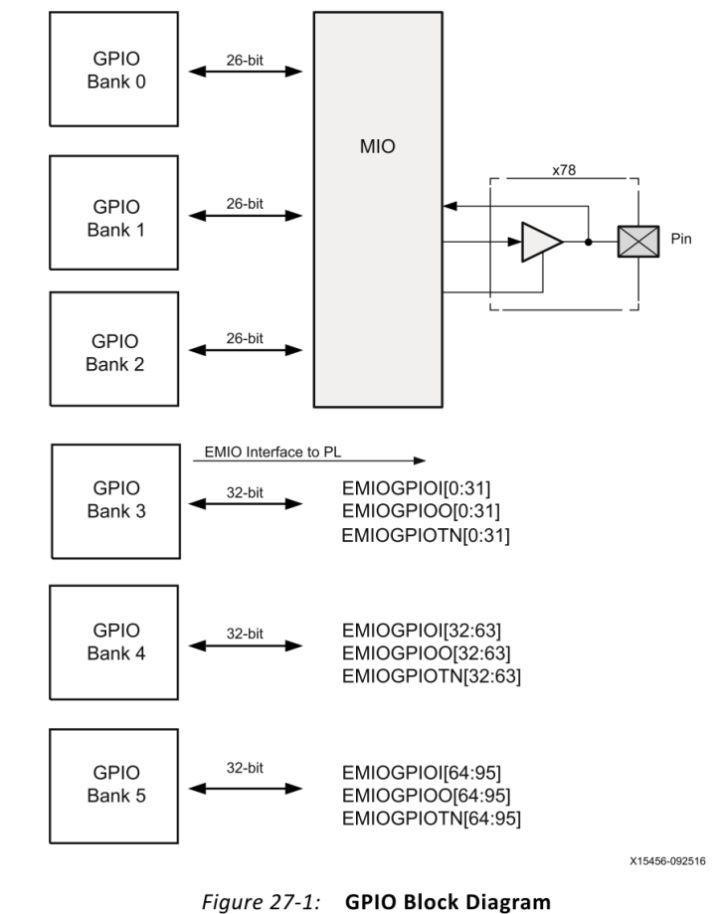

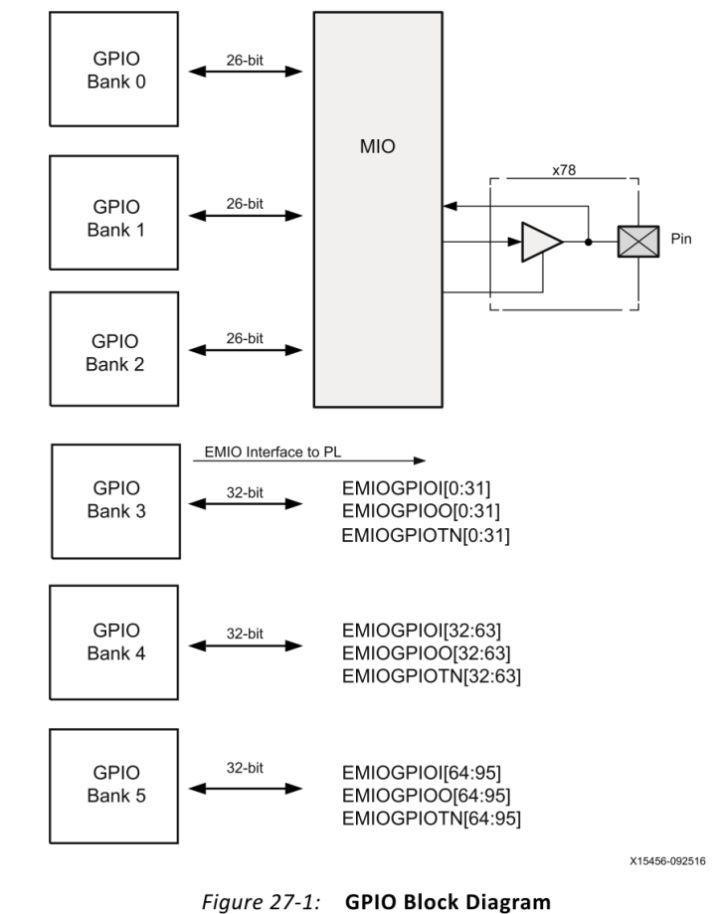

如果想用PS点亮PL的LED灯,该如何做呢?一是可以通过EMIO控制PL端LED灯,二是通过AXI GPIO的IP实现控制。本章介绍如何使用EMIO控制PL端LED灯的亮灭。同时也介绍了,利用EMIO连接PL端按键控制PL端LED灯。

2021-01-30 10:05:00 8761

8761

使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL端的LED灯,实验虽然简单,不过可以让我们了解PL和PS是如何结合的。

2021-02-01 10:06:00 7851

7851

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常

2021-01-30 09:54:00 16464

16464

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

2021-02-22 13:51:00 9724

9724

/005899fe6815 二、ZYNQ7020 分为PS端、PL端 PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。 PL: 可编程逻辑

2021-05-12 10:25:31 19445

19445

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 3710

3710

MPSoC有六个PL侧高性能(HP)AXI主接口连接到PS侧的FPD(PL-FPD AXI Masters),可以访问PS侧的所有从设备。这些高带宽的接口主要用于访问DDR内存。有四个HP AXI

2022-07-22 09:25:24 4483

4483 在Zynq MPSoC的器件里,PS (Processing System )集成了三个看门狗,分别是CSU SWDT,LPD SWDT和FPD SWDT。

2023-06-30 09:47:22 2983

2983

xilinx mpsoc 平台中,PS 和 PL 进行交互时,PS 需要获取 PL 发出的中断信号。从 mpsoc 技术参考手册 ug1085 TRM 中可知,PL 给到 PS 的中断有两组

2023-08-24 16:06:22 2986

2986

大家好,我似乎遇到了与MPSoC交互的UART接口问题。在遵循系统控制器GUI教程(XTP433)时,我似乎无法连接到MP。波特率设置为115200.当尝试设置Si5328频率时,软件超时且无法设置

2019-10-09 07:03:27

;,可看到UART1已配置成EMIO模式。 2 emio_can_demo案例 2.1案例功能 案例功能:PS端通过EMIO方式使用CAN接口进行数据收发 CON6通过CAN总线隔离芯片引出PL端10

2024-07-25 16:14:10

实验15_i2c时序及EEPROM介绍16_i2c EEPROM及温度传感器控制实验17_PS端DP接口显示实验18_SD原理介绍19_SD卡TXT文件读写实验20_SD卡Bmp图片显示实验21_

2022-07-21 10:34:51

中的片内外设。AXI-HP接口(4个):是高性能/带宽的标准的接口,PL模块作为主设备连接(从下图中箭头可以看出)。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)AXI-ACP接口

2018-01-08 15:44:39

、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机

2021-05-28 14:28:28

ZYNQ PS端IIC接口使用笔记

2021-02-23 06:23:31

ZYNQ Ultrascale+ MPSOC FPGA教程

2021-02-02 07:53:25

建立这部分请参考我上篇讲述搭建操作系统的文章二、VIVADO工程设置zynq核的搭建也请参照上篇文章,不过需要增加一些内容;双击zynq核,进入zynq的配置;选择PS-PL Configuration,选中General—>Enable Clock Resets—>FCLK_RESET

2021-12-17 06:42:06

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

本帖最后由 blackroot 于 2015-6-10 17:06 编辑

一直没搞懂PS怎样给PL提供复位和时钟,今天这个问题终于解决了~~~~~用一个简单的例子来说明一下,怎样使用PS输出

2015-06-10 16:59:53

在板子上除了给PS(33.33 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。为了让PL部分正常工作,一种方法是使用接口板从外部

2015-06-01 11:54:12

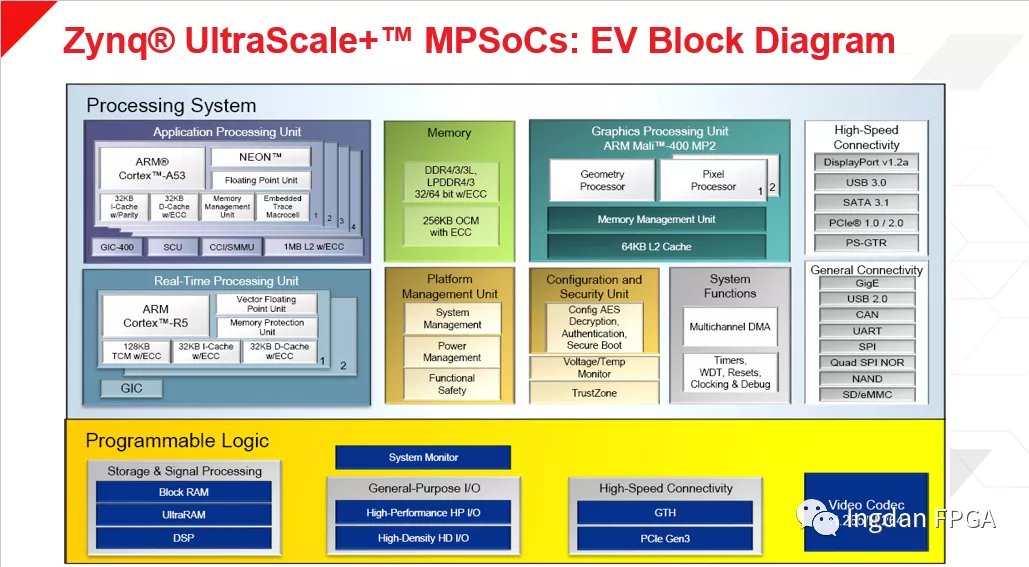

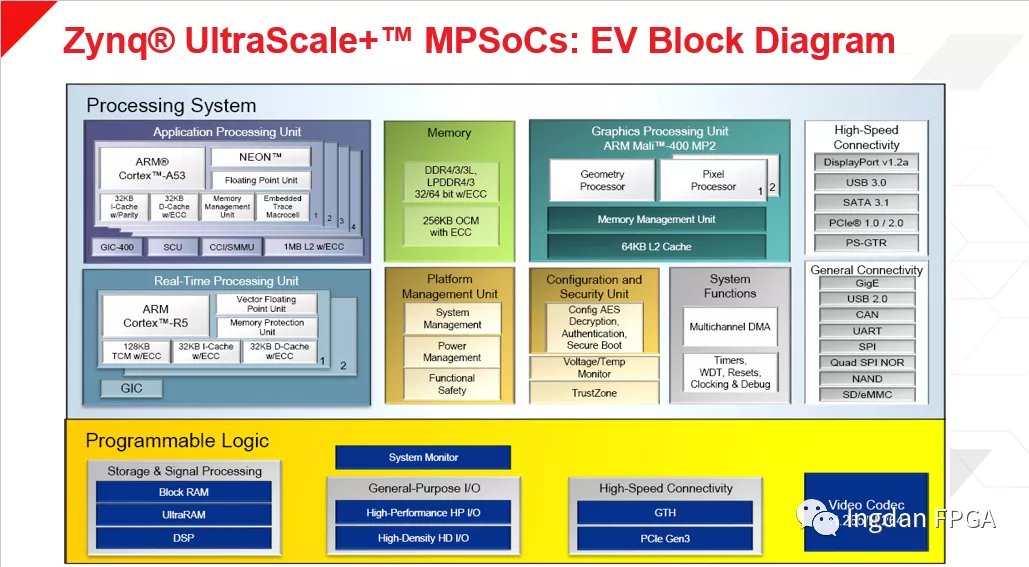

。 ZYNQ MPSoC芯片的总体框图 PS: 处理系统(Processing System) , 就是与FPGA无关的ARM的SoC的部分。 PL: 可编程逻辑 (Progarmmable

2021-01-07 17:11:26

我想给板子接上一个u***接口的键盘,不跑操作系统,只用ps部分接收键盘的数据然后传递给PL,不知道如何编写sdk的代码来跟u***的phy通信呢?有没可以参考的例程或者文档?

2015-12-16 17:12:38

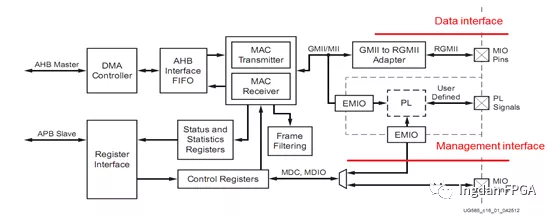

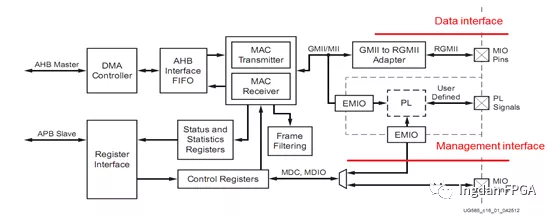

本文介绍了一种基于MPSoC的以太网接口设计方案。

2021-05-19 07:22:17

机与评估板的调试串口相连接,将评估板的RS232串口连接至PC机的USB接口,硬件连接如下图所示。

图 3

参考产品资料,先加载设备树文件和PL端可执行文件,然后在PS端串口终端执行如下命令,通过

2024-08-22 14:04:12

赛灵思和 DornerWorks 的系统软件团队在赛灵思的 Zynq® Ultrascale+™ MPSoC 上启动 Xen Project 管理程序时,我们发现可通过运行当年叱诧一时的流行电子游戏

2019-10-09 06:21:21

我的设备是zedboard702,我知道如何在使用PS和PL时使用SDK生成启动映像和程序闪存。问题是我只是使用PL,现在如何编程flash?

2019-09-30 09:43:18

亲爱的大家,我只是想知道如何找到Ultrascale +的PL和PS的地址转换(映射方案到DRAM-我的意思是哪个等级,库等)?

2019-10-16 08:35:37

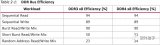

),并在高级选项卡中启用高级流量生成器: DDR 应用: 一旦 PHY 接口被验证,如果还会出现问题,请尝试切换到 PS-DDR,看看问题是否还会继续。 这将表明该问题是一个 VCU 至内存

2021-01-07 16:02:09

大家好,我已经在PS中产生了一个100Mhz的时钟信号,并使其在外部被PL接收。我使用了原始的ODDR但没有成功我可以从引脚输出100 Mhz时钟。有什么建议么??以上来自于谷歌翻译以下为原文

2019-02-22 09:09:05

5.31我在做PL控制PS DDR时遇到个问题,就是从机(DDR)的wready信号就不会拉高,只有你发出wvalid信号时才会拉高,(这是通过跑通例程抓取信号看见的)。然而awready信号是会

2024-05-31 12:04:29

为什么一个简单的程序运行不了,请求帮忙看一下。做个LED流水灯,是想用PS部分生成100MHz的频率,然后用这个频率来实现PL部分三色led移位,但是好像PS部分有问题,不知道怎么配置了。这是PS

2016-01-02 21:35:38

PS测试1、 QSPI加载2、 DDR3读写3、 EMMC读写4、 网口测试(RGMII接口)5、 USB转串口收发测试2.MPSOC PL测试1、 KEY/LED/拨码开关/PMOD测试2

2023-04-13 16:04:38

你好我们正在考虑在我们的新设计中使用Zynq Ultrascale + MPSOC。我们想在我们的电路板设计中加入HDMI接口。 Zynq Ultrascale + MPSOC在PS中有一个

2019-10-14 09:17:03

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

2020-08-03 15:53:30

XAPP1251说明显示,可以在Zynq ARM处理器上运行XVC服务器来控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一个FPGA中控制PL JTAG?可以使用运行在设备PS部分上

2020-07-30 13:51:19

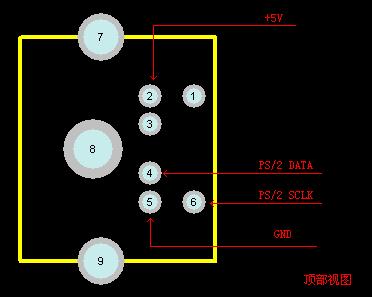

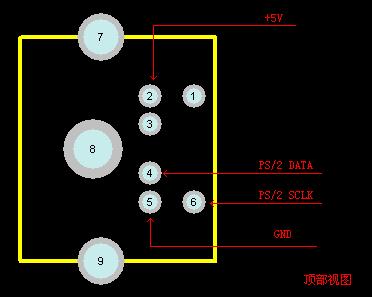

鼠标有RS232串口和PS/2二种接口,在单片机应用中,由于PS/2鼠标是1yrL电平,和单片接口更方便,通常PS/2鼠标控制芯片采用TP8452。以TP8452为例说明PS/2鼠标的工作原理,其他

2008-10-22 23:00:22 121

121 altera大学项目PS2接口

2009-08-03 09:31:31 30

30 RS232接口在嵌入式设备中应用广泛。为了充分利用USB接口即插即用的特点,详细介绍一种基于PL2303的RS232与USB转换的设计方案。PL2303是高集成度的通用串行总线(USB)与串口的接口转

2010-12-31 17:23:17 277

277

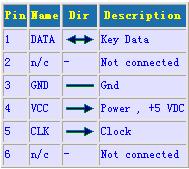

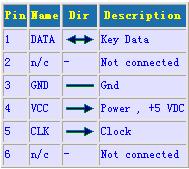

PS/2接口协议解析及应用

2006-07-03 14:29:19 2830

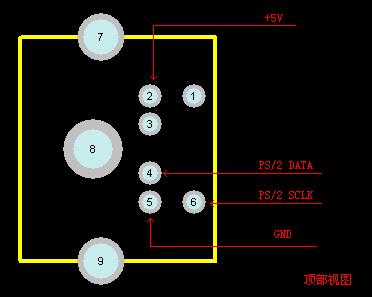

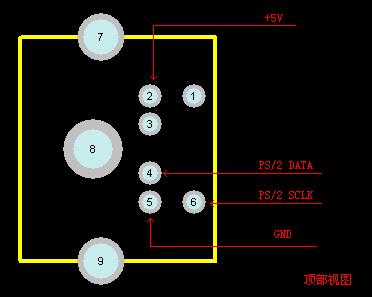

2830 ps 2接口定义图

外观为: &n

2007-11-19 17:25:36 6800

6800

PS 2 鼠标接口引脚定义图

PS/2 鼠标接口为 6 针母插,外观为:

2007-11-27 12:34:52 20239

20239

PS2键盘接口引脚定义图

PS/2 键盘接口为 6 针母插,外观为:

2007-11-27 12:36:18 44970

44970

PS/2 鼠标接口定义PS/2 鼠标接口为 6 针母插。Pin Name Description1 DATA Key Data2 n/c Not connected3 GND Gnd4 VCC +5 VDC5 CL

2009-02-12 10:34:34 3010

3010 什么是ps2接口 ps2接口是什么意思?

PS/2接口是目前最常见的鼠标接口,最初是IBM公司的专利,俗称“小口”。这是一种鼠标和键

2009-05-03 22:07:26 27855

27855

什么是PS/2接口

很多老式的品牌机上采用PS/2口来

2010-01-22 12:21:57 2542

2542 什么是主板PS/2鼠标接口

PS/2鼠标接口:现今的一些流行的Pentium

2010-02-05 11:46:51 1652

1652 本文通过实例详细解析如何利用Zynq-7000的PL和PS进行交互。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22 58287

58287

文中详细介绍了PS/2接口协议的内容、电气特性和标准键盘的第二套键 盘扫描码集。给出了基于嵌入式系统的PS/2接口的软、硬件实现方法,并介绍了工控PC外接双键盘的解决方案。

2016-03-25 15:25:53 18

18 针对标准的PS/2设备,实现了与单片机的接口,本文分析了PS/2键盘的接口和通讯议,介绍了PS/2键盘与单片机的接口设计,并以8051为例,配合点阵LCD显示器,实现了PS/2键盘的输入,并进一步探讨了用PS/2鼠标实现嵌入式设备的图形化人机接口(GUI)。

2016-03-25 14:50:51 11

11 本篇文章详细的介绍了介绍ps2接口协议及其典型应用

2016-08-24 16:52:02 10

10 分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1、传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送; 2、PL端接口为FIFO接口; PS到PL的数据传输流程: PS

2017-02-08 01:00:11 2324

2324

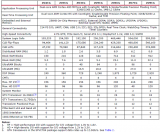

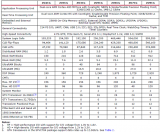

可以直接给出这个数据使我们看到有多少个SerDes接口,以及Zynq UltraScale+ MPSoC系列中的每款器件各有多少个

2017-02-08 05:50:41 847

847 的GTR也是单独供电的,还有还有,这个GTR的电压竟然和PL端的GTH完全不同。图4是Zynq-7000和Zynq UltraScale MPSoC电源系统的比较。 典型的是,内核电压由1.0V降至

2017-02-08 08:33:41 650

650

因为MicroZed是个低成本的开发套件,所以在板子上除了给PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。

2017-02-09 14:16:11 4978

4978

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 1426

1426

我们先来了解一下上节中介绍的Zynq SoC PS/PL接口,我创建一个很简单的外设,使用的是DSP48E1的DSP逻辑片,依靠这个外设第一个寄存器内的控制字执行乘法,加法或减法。

2017-02-10 12:04:41 843

843

构建SoC系统,毕竟是需要实现PS和PL间的数据交互,如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,本节研究如何再实现PL端对DDR3的读写操作。

2017-09-18 11:08:55 23

23 的文章,在此分享。 当我们在设计中使用Zynq SoC或Zynq UltraScale + MPSoC时,可以有两种方法来实现SPI接口: 1. 使用PS端的SPI控制器(PS端有两个SPI控制器

2017-12-30 05:03:45 7716

7716

zedboard可以将逻辑资源和软件分别映射到PS和PL中,这样可以实现独一无二和差异换的系统功能,主要分为两大部分,处理系统和可编程逻辑。以及二者之间的互联特性。这篇笔记主要记录zedboard的大体架构。

2018-06-26 06:24:00 7451

7451 该视频重点介绍了UltraScale +产品系列的第一个成员Zynq®UltraScale+™MPSoC,并展示了使用可编程逻辑中的DDR4 SDRAM IP的存储器接口系统的稳健性。

2018-11-29 06:36:00 3849

3849 iVeia演示了将Android操作系统移植到Zynq UltraScale + MPSoC上,以获取角落和边缘检测滤波器的实时视频和控制系数。

结果是使用软件仿真器QEMU实现更快的从PS到PL的算法

2018-11-26 06:57:00 6006

6006 (PS)和可编逻辑(PL)架构,主要用在航空航天与国防,汽车电子,数据中心,无线通信基础设备和无线基础设施.本文介绍了Xilinx公司的Zynq® UltraScale+™MPSoC系列主要特性,应用方案以及AvnetUltra96开发板主要特性,框图,电路图,材料清单和PCB设计图.

2019-03-05 15:18:14 3941

3941

Cortex-A53和双核ARM Cortex-R5处理系统(PS)以及Xilinx可编逻辑(PL)UltraScale架构;此外还集成了片上存储器,多端口外接存储器接口,以及丰富的外设连接接口.处理单元

2018-12-11 18:17:01 2086

2086 Zynq在PS和PL之间有9个AXI接口。

2018-12-30 09:45:00 8291

8291 和基于双核ARM Cortex-R5的处理系统(PS)和Xilinx可编程逻辑(PL)超尺度架构。还包括片上存储器、多端口外部存储器接口和一组丰富的外围连接接口。

2019-02-20 15:57:46 15

15 和基于双核ARM Cortex-R5的处理系统(PS)和Xilinx可编程逻辑(PL)的超尺度结构。还包括片上存储器、多端口外部存储器接口和一组丰富的外围连接接口。

2019-02-21 16:48:54 22

22 Zynq UltraScale+ MPSoC是Xilinx推出的第二代多处理SoC系统,在第一代Zynq-7000的基础上做了全面升级,在单芯片上融合了功能强大的处理器系统(PS)和用户可编程逻辑(PL)。Zynq UltraScale+ MPSoC系统框图

2019-11-18 11:03:22 4111

4111

MPSoC是Xilinx基于16nm工艺推出的异构计算平台,由于灵活、稳定,在业界得到了广泛的使用。异构计算是一个比较新的领域,需要协调硬件设计、逻辑设计、软件设计,对工程师的要求很高。实际设计过程中,很多工程师对实现PS/PL之间的数据交互感到头疼。

2020-09-15 09:27:00 12835

12835

工程师根据FSBL的main.c中的InitWatchDog( ),添加代码后,依然不能使MPSoC的PS复位。

2020-09-19 11:15:06 2065

2065

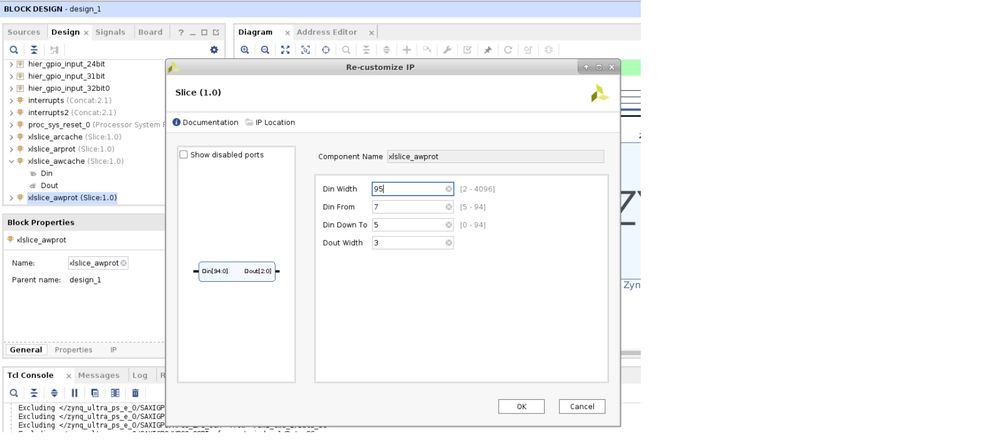

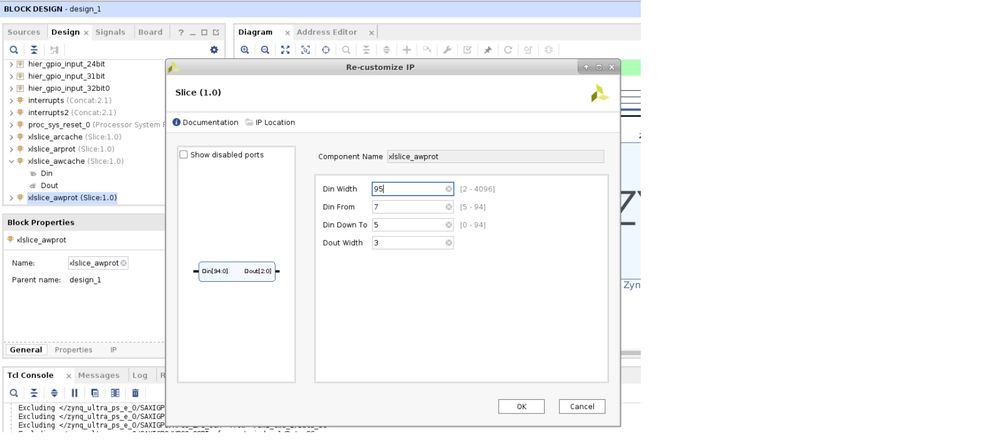

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。 普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚

2020-11-04 14:57:17 2474

2474

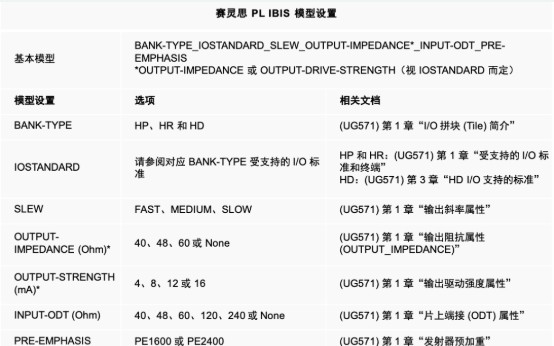

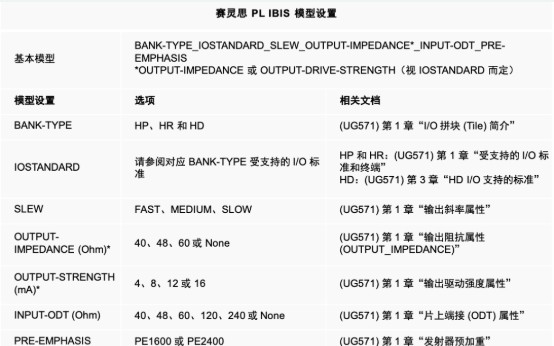

。 本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。 本文主要分 3 个部分: PL I/O 标准 PS MIO

2020-10-15 18:29:15 3123

3123

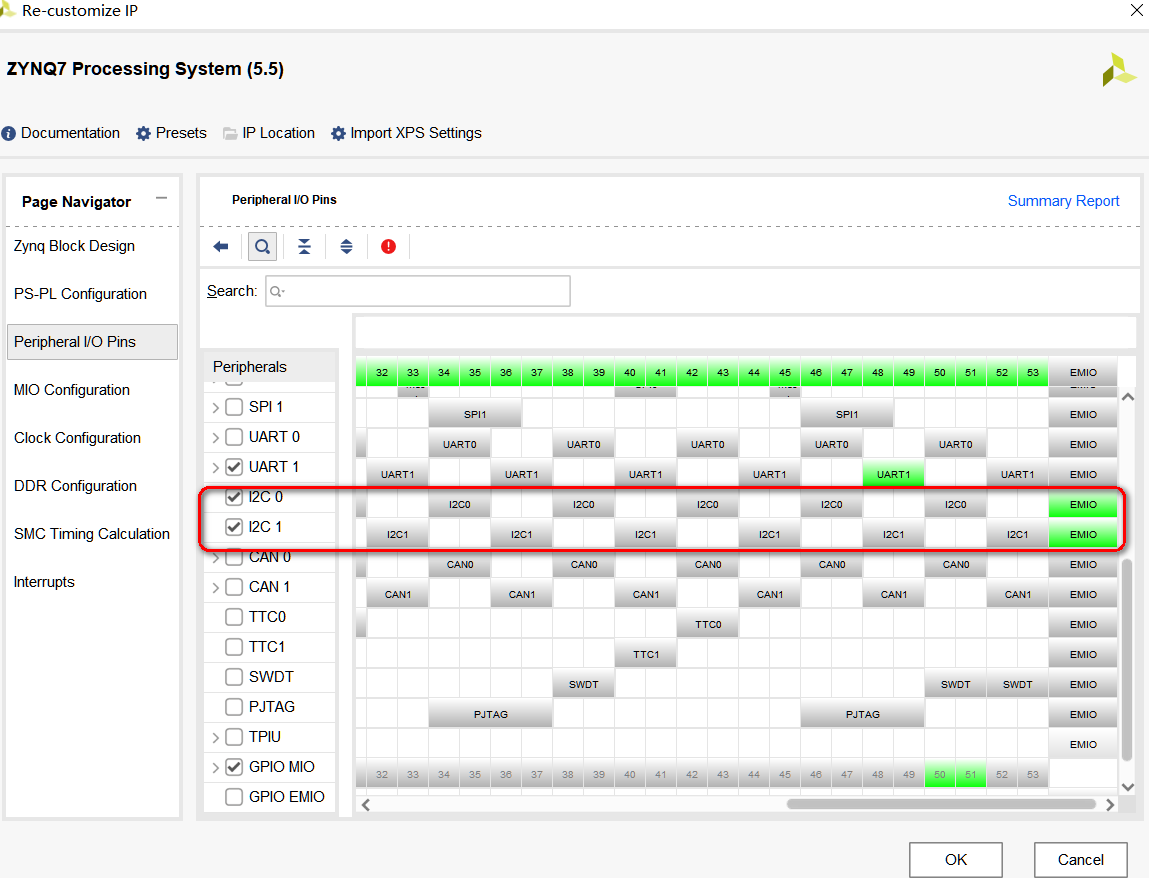

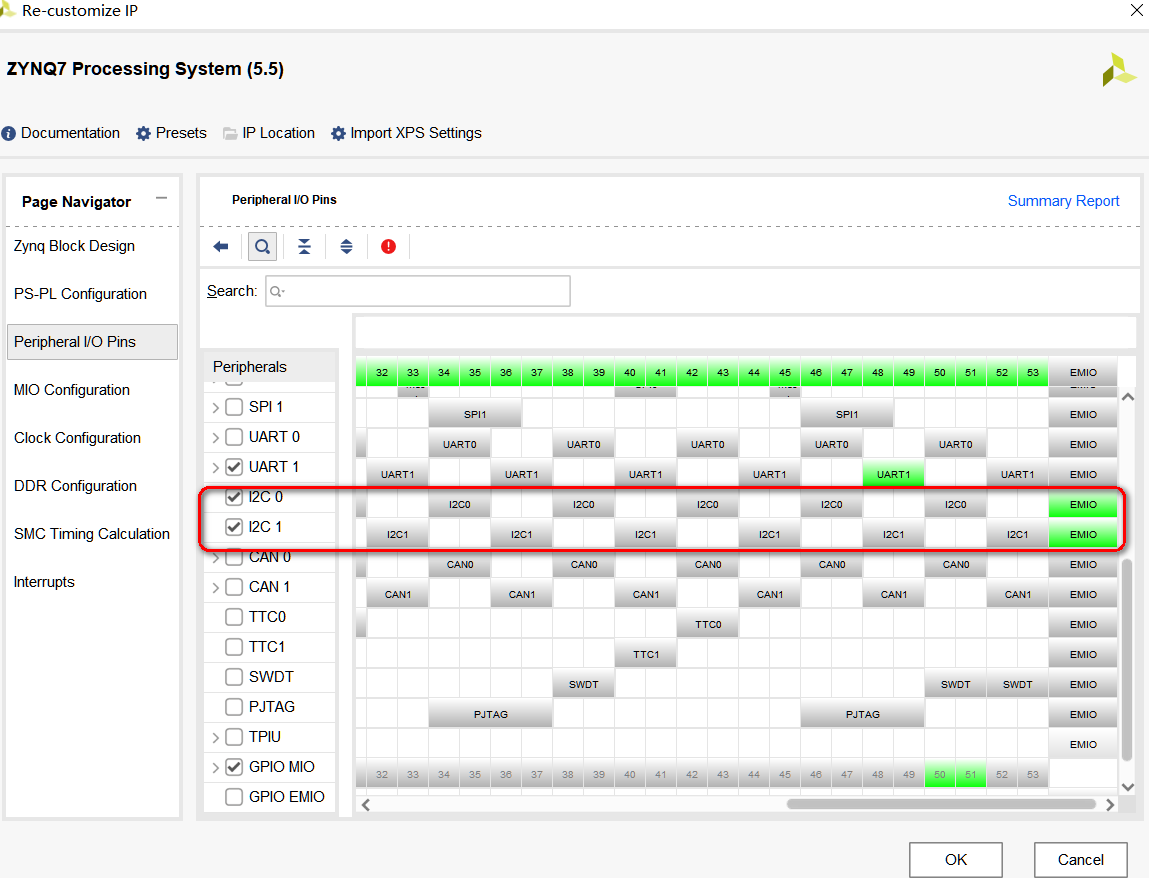

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK中

2022-07-25 17:56:52 3345

3345

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK中

2021-01-28 08:05:27 26

26 FPGAs,Zynq 和 Zynq MPSoC! Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品

2021-04-02 17:20:14 18829

18829

目录1. MPSoC的中断处理介绍 2. 扩展PL中断 3. 扩展AXI Intc中断 3.1. AXI Intc PL连接 3.2. AXI Intc Device Tree 3.3. AXI

2021-05-07 15:34:15 4690

4690 和PL侧。 PL和PS均支持64位的DDR4(不带ECC功能),PL部分如果要支持64位的DDR4,则至少需要提供三个bank的HP接口,只能

2021-09-16 10:17:02 7985

7985

的协议,可用于寄存器式控制/状态接口。例如,Zynq XADC 使用 AXI4-Lite 接口连接到 Zynq PS。

2022-05-10 09:52:12 4732

4732 Zynq&ZU+ Mpsoc的以太网使用普遍,从功能大致分为2类应用:调试管理、数据传输。本文主要集中在PS端的Ethernet RGMII外接phy设计和调试,该部分客户用的最多也最容易出问题,希望通过本文对基于RGMII+phy的典型应用快速入门,解决问题。

2022-08-02 08:03:29 4869

4869

目前基于MPSOC的一些参考设计中并没有实现开机画面的功能 ,那在一些带显示屏的产品在设计的时候就需要这一功能,基于原来传统的方式也可以在FPGA中来实现,今天分享一个在PS侧来实现开机画面,以节省PL侧的宝贵资源。

2022-08-02 10:23:20 1670

1670

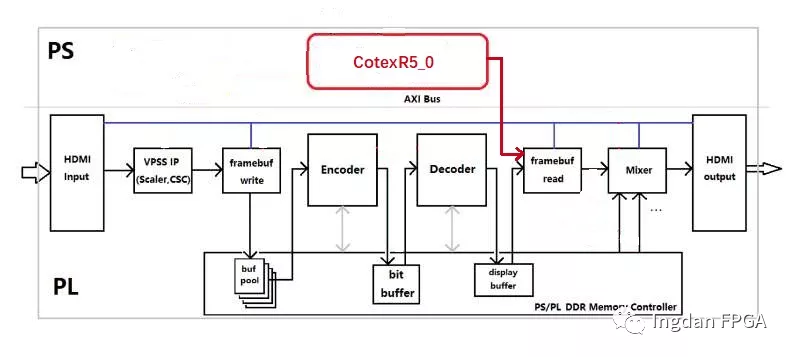

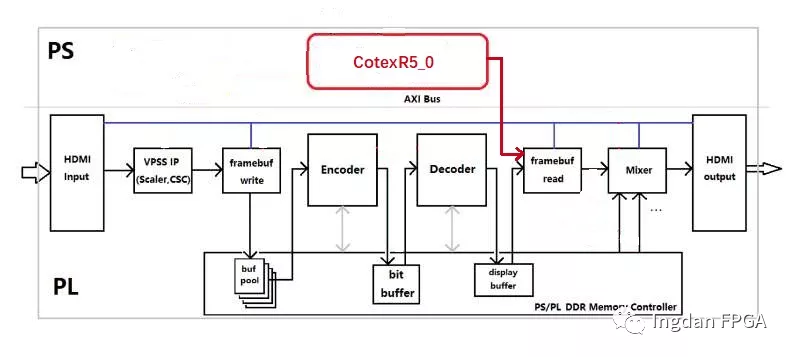

部分 ZynqUltraScale+MPSoC的可编程逻辑(PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自PL 或PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间

2022-08-02 16:48:15 4463

4463

MPSoC是带ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请

2022-08-02 09:14:52 2125

2125 Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点.

2022-08-15 09:16:38 3750

3750 电子发烧友网站提供《将Zynq PS和PL与内存映射寄存器集成.zip》资料免费下载

2022-12-06 15:14:29 2

2 S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

2023-02-01 15:36:53 4693

4693 有客户需要通过PCie从Windows系统访问MPSoC的DDR,从而使X86和A53通过共享DDR内存的方式交互大量数据

2023-07-10 16:52:32 1823

1823

电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案应用笔记.pdf》资料免费下载

2023-09-15 10:29:25 3

3 电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案.pdf》资料免费下载

2023-09-15 10:05:18 2

2 资料\Demo\All-Programmable-SoC-demos\”目录下。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机/Linu

2023-01-03 15:50:37 19

19 ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之间的数据交互是系统设计的核心。

2025-10-15 10:33:19 737

737

电子发烧友App

电子发烧友App

评论