它是RoCE v2协议进行信息及数据交换的核心机制,也是DUT需要实现的核心机制之一,对该功能的仿真....

在接收到正确的删除队列请求后,首先进入连接断开流程,即四次挥手断链,如图中红框部分。随后进行队列删除....

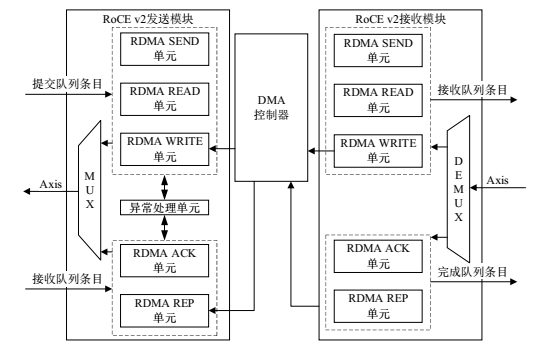

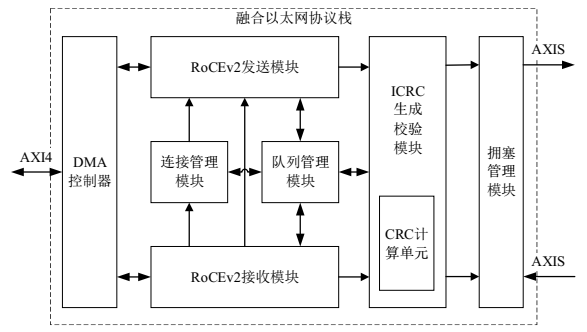

当 RoCE v2 发送模块检测到发送队列非空时,则从发送队列中读取一个发送队列条目,并判断请求类型....

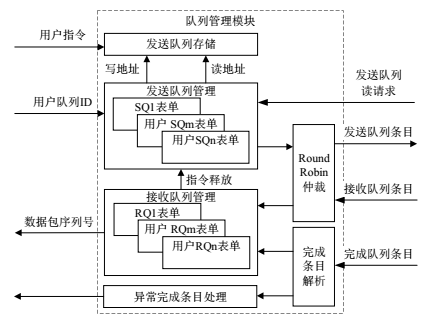

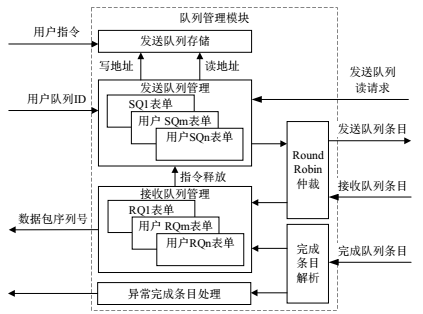

发送队列存储为所有发送队列共用的存储空间,根据用户环境和开发板环境不同可由 BRAM、URAM 或 ....

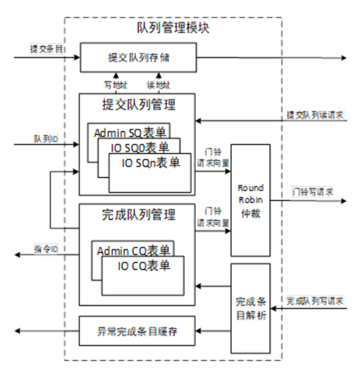

队列管理模块采用管理与存储分离的结构进行设计,由发送队列存储、发送队列管理、接收队列管理、完成条目解....

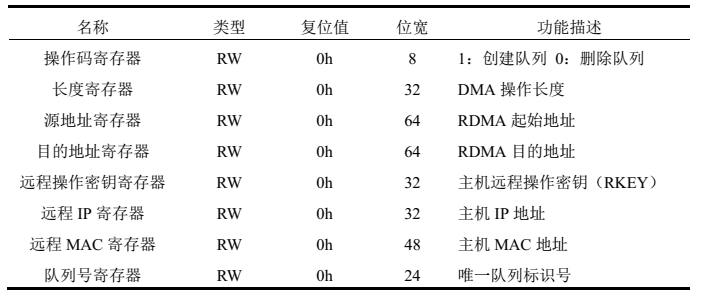

连接管理模块负责管理 RoCE v2 高速数据传输系统与主机之间的连接和断开。在 RoCE v2 中....

指令控制单元负责控制数据传输及 DMA 数据读写。该单元简化了数据传输及DMA 操作,使得用户可以更....

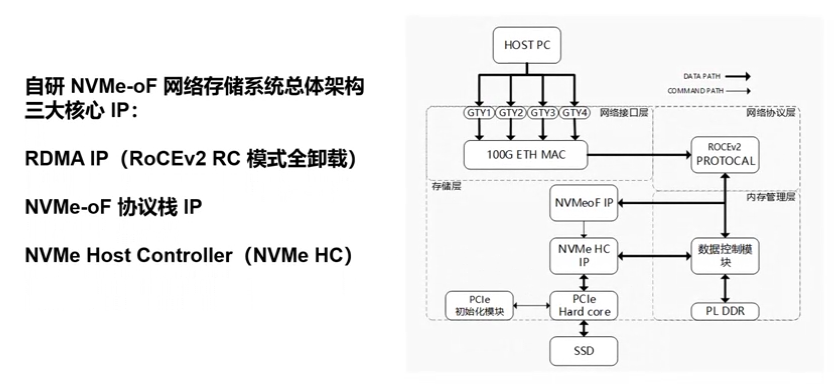

解决网络传输瓶颈,这里主要分析如何设计对列控制管理

状态管理单元负责读取系统工作状态,包括物理链路连接状态和队列连接状态,并反馈给上位机。

目前相关IP较少,网上主要是知名FPGA厂家的IP,疑似被泄露。但是技术支持可能没有了,补丁会限制部....

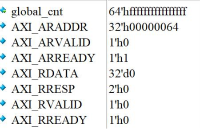

寄存器最大值为 64’hFFFFFFFFFFFFFFFF,到达最大值后一个时钟周期后翻转回 0, 在....

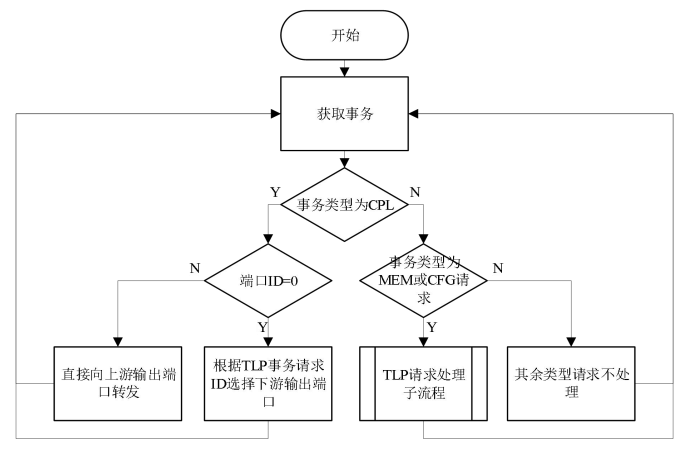

最小桥设备模型的每个端口的输入端对接一个 TLP事务处理程序, 该程序负责将接收到的 TLP 事务进....

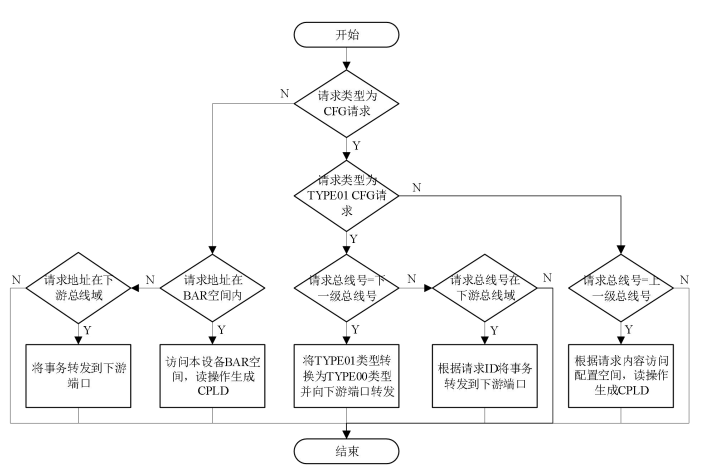

当请求类型为 MEM 读写请求时使用地址路由的方式。 如果请求地址在此设备 BAR 空间内, 则对 ....

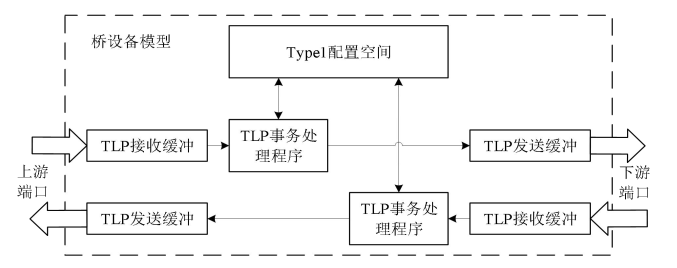

桥设备模型模拟虚拟 PCI 桥设备的配置空间和路由功能。 桥设备是拓展 PCIe 链路的关键设备, ....

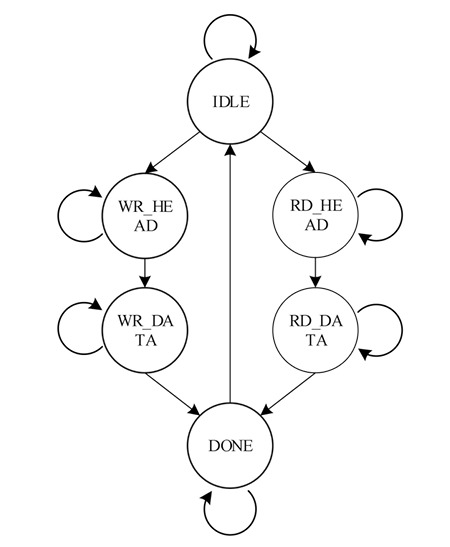

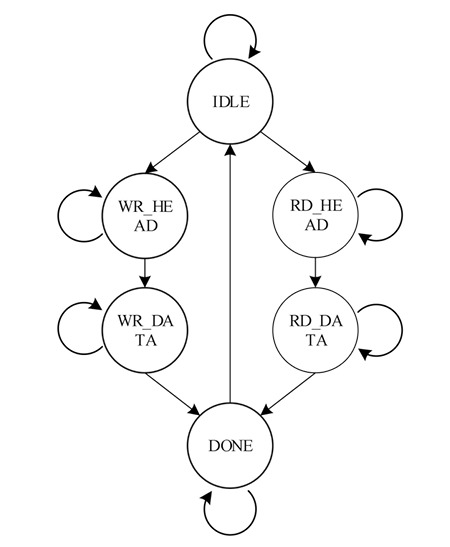

驱动器负责 TLP 事务与接口信号的转换, 驱动器的程序结构如图 1 所示。 在本IP中使用的接口为....

UVM 验证包的主要功能是对 DUT 提供激励, 仿真验证对应的功能, 并对测试结果进行自动对比分析....

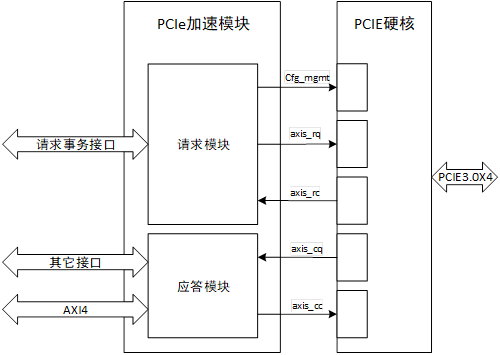

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接....

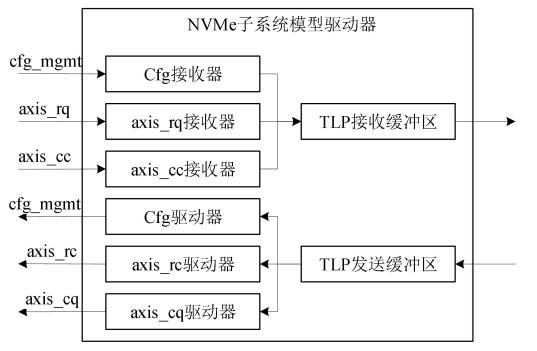

应答模块的具体任务是接收来自PCIe链路上的设备的TLP请求,并响应请求。由于基于PCIe协议的NV....

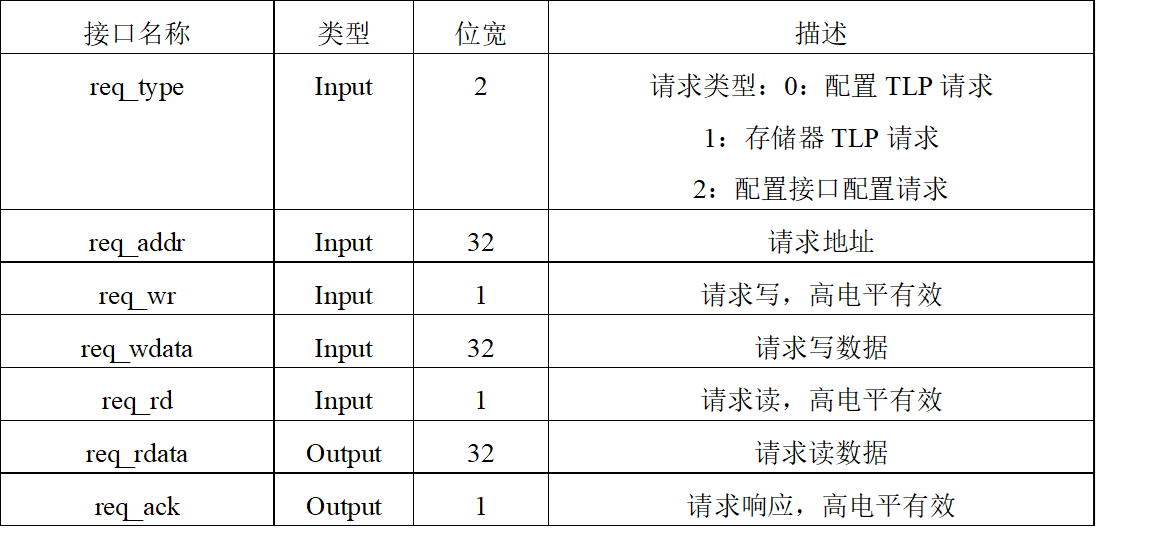

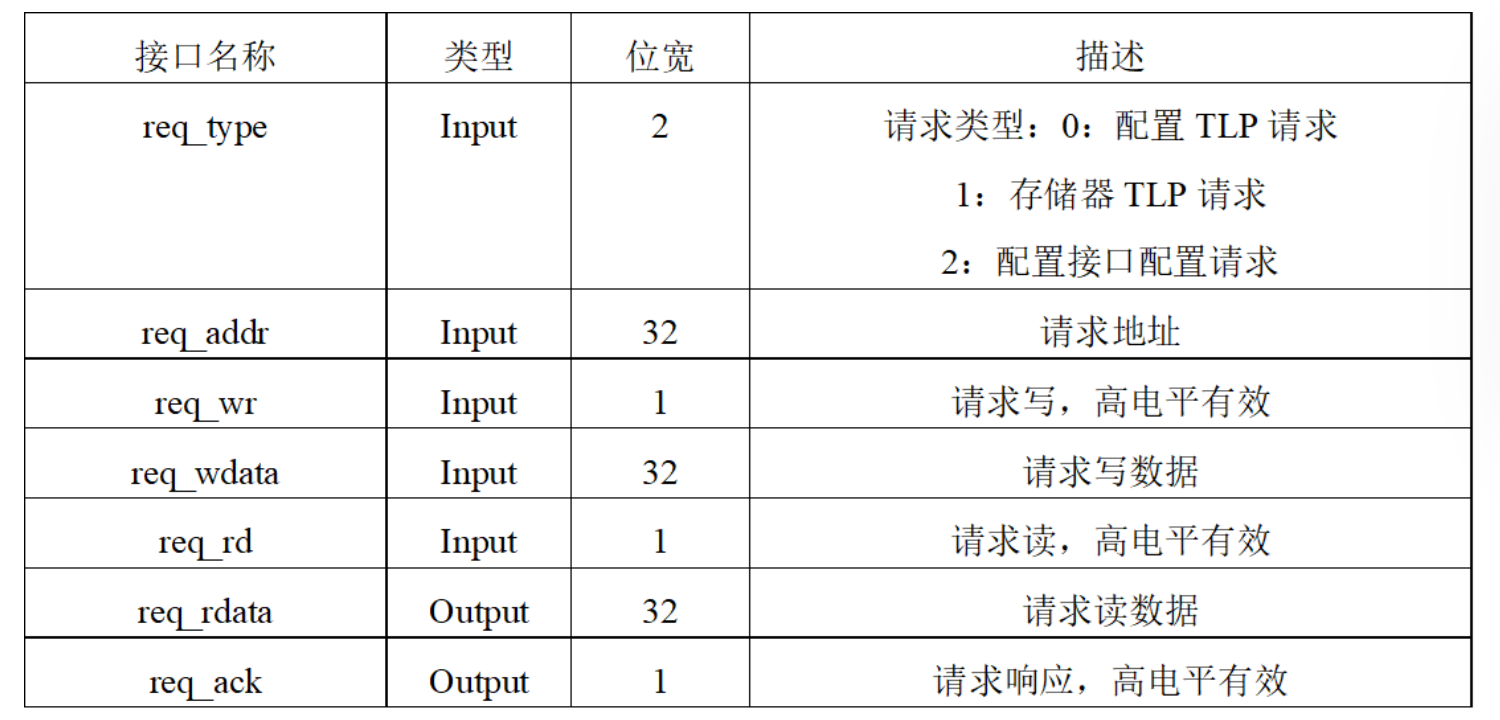

在接收到请求总线接口的请求事务后,当请求类型的值为0时,表示通过PCIE硬核的配置管理接口发送请求,....

请求模块的具体任务是将系统的请求转换成为axis接口形式的TLP或配置管理接口信号。这些请求主要包含....

PCIe加速模块负责实现PCIe传输层任务的处理,同时与NVMe层进行任务交互。PCIe加速模块按照....

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接....

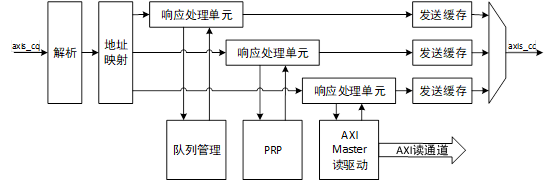

对于存储器读请求TLP,使用Non-Posted方式传输,即在接收到读请求后,不仅要进行处理,还需要....

应答模块的具体任务是接收来自PCIe链路上的设备的TLP请求,并响应请求。由于基于PCIe协议的NV....

在接收到请求总线接口的请求事务后,当请求类型的值为0时,表示通过PCIE硬核的配置管理接口发送请求,....

这是采用PCIe设计NVMe,并非调用XDMA方式,后者在PCIe4.0时不大方便,故团队直接采用P....

请求模块负责将系统请求转换为AXIS接口的TLP信号或配置管理接口信号,处理初始化配置请求和门铃写请....

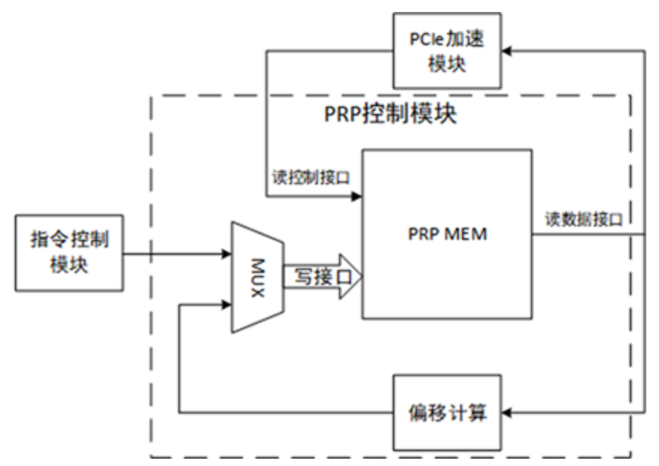

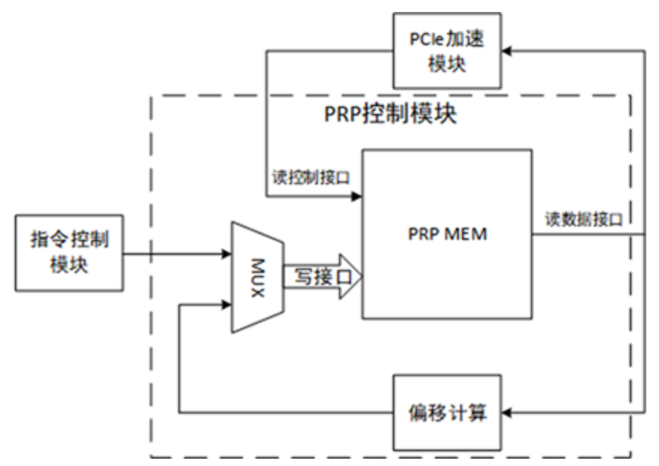

PRP控制模块优化了NVMe协议中的PRP列表管理机制,通过将PRP存储位置迁移至NoP逻辑加速引擎....

摘要:PRP控制模块优化了NVMe协议中的PRP列表管理机制,通过将PRP存储位置迁移至NoP逻辑加....

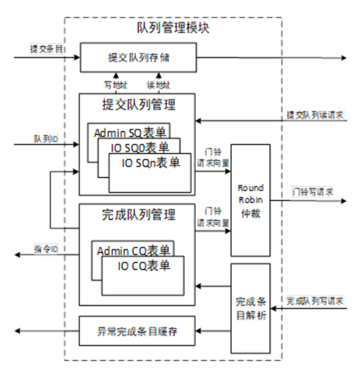

队列管理模块采用队列的存储与控制分离的设计结构,由于提交队列管理单元使用表单管理队列信息,所以使队列....