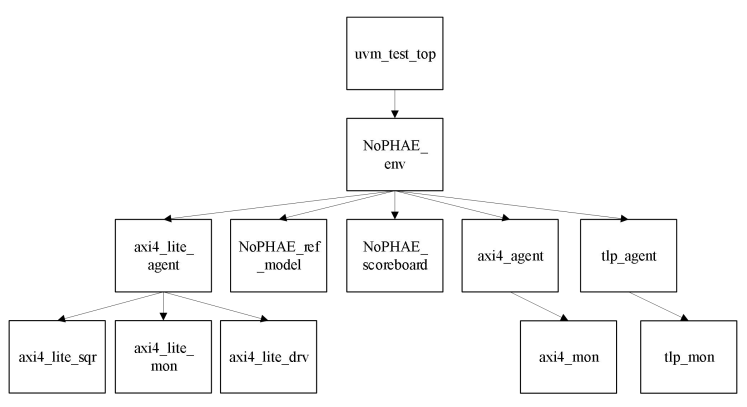

UVM 验证包设计结构如图 1 所示。 UVM 验证包的主要功能是对 DUT 提供激励, 仿真验证对应的功能, 并对测试结果进行自动对比分析与统计。 验证包包含一个NoPHAE_env 验证环境, 验证环境下包含 axi4_lite_agent、 axi4_agent、 tlp_agent、NoPHAE_ref_model、 NoPHAE_scorebarod 组件。

图1 UVM 验证包设计结构图

Axi4_lite_agent 负责对接 AXI4-Lite 接口。 在 DUT 使用的三个接口中, AXI4-Lite接口用于连接系统控制模块, 实现系统控制功能, 所以激励的添加主要通过 AXI4-Lite接口。 在 axi4_lite_agent 中包含 axi4_lite_drv、 axi4_lite_mon、 axi4_lite_sqr 三个组件,分别提供 axi4_lite 总线的主机驱动器( driver)、 监测器( monitor) 和序列发生器(sequencer)。 驱动器从序列发生器获取事务, 并将其转换为 AXI4-Lite 接口信号;监测器从接口上监测信号, 将其组成事务发送到参考模型和计分板; 序列发生器根据测试用例产生事务。

Axi4_agent 负责监测 AXI4 总线接口。 由于 AXI4 总线接口用于进行数据传输,在验证平台中该总线接口实际与 AXI BRAM IP 对接, 不需要添加特殊的激励。 因此, axi4_agent 中只包含了一个 monitor, 将总线信号转换为 AXI4 事务发送到计分板。

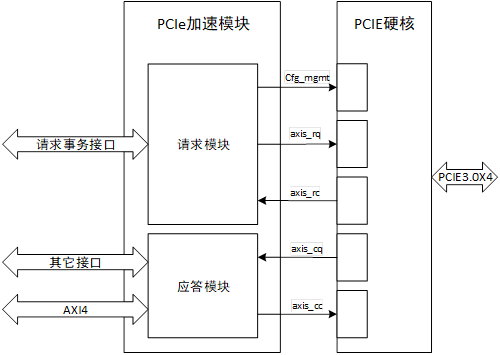

Tlp_agent 负责监测分离的 PCIE 集成块接口, 分别是一个 cfg_mgmt 接口, 四个axis 接口, 这些接口信号均可转换为 PCIe TLP 事务。 这些接口与 NVMe 子系统模型对接, 因此 tlp_agent 中只包含一个 monitor, 将监测到的 PCIe TLP 事务发送到计分板。

NoPHAE_ref_model 是模拟 DUT 设计功能的参考模型, 该模型从 axi4_lite_agent的监测器获取寄存器配置信息, 根据这些信息将预期的 AXI4 事务和 PCIe TLP 事务发送到 NoPHAE_scorebarod。

NoPHAE_scorebarod 计分板负责收集各个接口监测器监测到的传输事务, 并将这些事务与参考模型给出的预期事务进行对比, 并统计对比结果, 根据结果判断测试用例执行是否成功。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

-

PCIe

+关注

关注

16文章

1483浏览量

88955 -

UVM

+关注

关注

0文章

183浏览量

20106 -

高速存储

+关注

关注

0文章

15浏览量

6103 -

nvme

+关注

关注

0文章

301浏览量

23918

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计九:队列管理模块设计(上)

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

NVMe高速传输之摆脱XDMA设计42:DMA 读写功能验证与分析

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化

NVMe IP高速传输却不依赖XDMA设计之九:队列管理模块(上)

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

评论