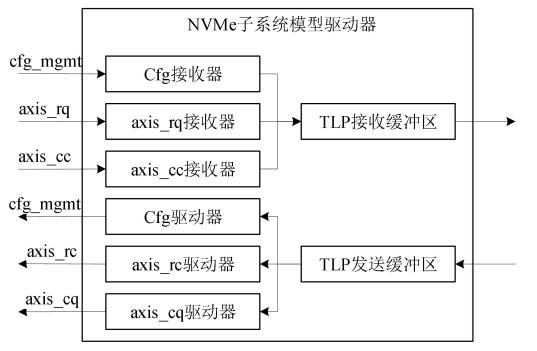

驱动器负责 TLP 事务与接口信号的转换, 驱动器的程序结构如图 1 所示。 在本IP中使用的接口为 PCIE 集成块的接口, 分别是 cfg_mgmt 接口、axis_rq 接口、axis_rc接口、 axis_cq 接口、 axis_cc 接口。

图 1 驱动器程序结构图

cfg_mgmt 接口仅用来传递 RC 端发起的 PCIe Type0 配置事务, axis_rq 接口是 RC端发起 TLP 请求的接口, axis_rc 接口是 RC 端接收 TLP 请求响应的接口, axis_cq 接口是 PCIe 下游设备发送 TLP 请求的接口, axis_cc 接口是 PCIe 下游设备接收请求响应的接口。 对应接口的接收器在从接口接收到请求时, 首先提取 TLP 报文头部信息到 TLP 事务类中, 当请求类型为写请求时, 将数据存入 TLP 事务类中, 否则等待下一个接口事务。 驱动器在接收到下游设备的 TLP 包后, 根据包类型选择接口驱动器,再将 TLP 事务类中的数据结构整合为对应接口的数据形式发送。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

审核编辑 黄宇

-

驱动器

+关注

关注

54文章

9118浏览量

156601 -

PCIe

+关注

关注

16文章

1483浏览量

88976 -

高速传输

+关注

关注

0文章

46浏览量

9322 -

nvme

+关注

关注

0文章

301浏览量

23923

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计44:工程设计考量?

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

NVMe高速传输之摆脱XDMA设计26: 驱动器设计

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化

NVMe高速传输之摆脱XDMA设计26:驱动器设计

NVMe高速传输之摆脱XDMA设计26:驱动器设计

评论