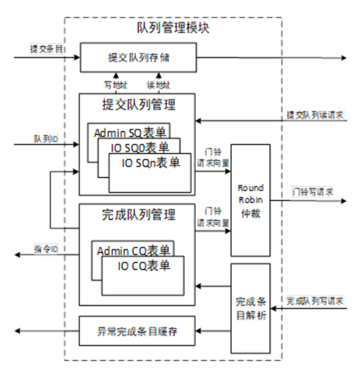

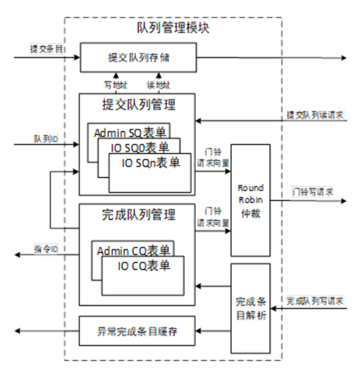

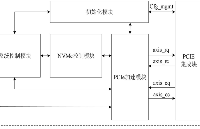

续上,队列管理模块采用队列的存储与控制分离的设计结构,如图1所示为队列管理模块的结构框图。

图1 队列管理结构

由于提交队列管理单元使用表单管理队列信息,所以使队列具有了可动态配置的属性,通过修改表单的信息便可以修改队列数量和深度。在实际应用中,当出现大量随机数据读写请求时,可以通过修改表单增加队列数量和深度,增强随机读写性能;在顺序读写数据时,可以清除表单减少队列数量和深度,降低资源占用和功耗。

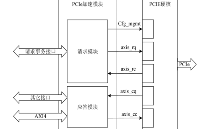

对于完成队列,设置一个完成队列管理单元、一个完成条目解析单元和一块异常完成条目缓存。完成管理单元中同样包含了完成队列表单,与提交队列表单不同的是完成队列表单中只包含了门铃地址、队列深度和门铃头、尾指针,并且只设置了一个admin完成队列和一个I/O完成队列。

这样的结构设计基于两个方面的考量:首先,当完成条目状态为正常完成时,只需将完成条目中的指令ID释放到ID池,将对应提交队列ID的门铃头指针更新到提交队列条目,当完成条目状态为异常时,将其写入异常完成条目缓存等待处理,这些过程由完成条目解析单元在短时间内并行处理,不会出现完成队列写请求的阻塞,因此不需要设置多个I/O完成队列和完成条目的存储空间。其次,由于ID池的存在,所有的NVMe指令都具有一个唯一的ID,完成条目中的提交队列ID不再作为指令的标识,因此仅使用一个I/O完成队列对应多个I/O提交队列是可行的,并且异常的I/O完成条目和异常的admin完成条目存放在同一个缓存中也不会影响ID的辨识作用。

在有新的提交条目写入提交队列和新的完成队列写请求时,提交队列管理单元和完成队列管理单元向对应的队列发起门铃写请求,这些请求经过Round Robin仲裁器的仲裁后被发送给SSD。实际上,随着仲裁输入数量的增加,仲裁的效率和时序也会变差[[i]]。假设采用完成队列和提交队列一一对应的结构,仲裁的输入数量将是提交队列数量的2倍,要保证仲裁效率和良好的时序,只能降低提交队列数量,导致性能下降。而完成队列管理单元所实现的结构只占用两个仲裁请求输入,基于此可以增加更多的I/O提交队列,充分发挥SSD性能。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

审核编辑 黄宇

-

nvme

+关注

关注

0文章

301浏览量

23923

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计54:如何测试队列管理功能2

NVMe高速传输之摆脱XDMA设计53:如何测试队列管理功能

NVMe高速传输之摆脱XDMA设计37:队列管理功能验证与分析1

NVMe IP高速传输却不依赖XDMA设计之九:队列管理模块(上)

NVMe高速传输之摆脱XDMA设计十:队列管理模块设计(下)

NVMe高速传输之摆脱XDMA设计九:队列管理模块设计(上)

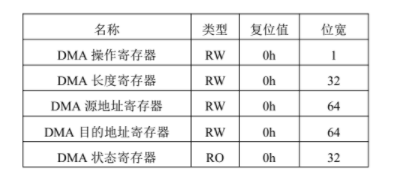

NVMe IP高速传输却不依赖XDMA设计之五:DMA 控制单元设计

NVMe IP高速传输却不依赖XDMA设计之五:DMA 控制单元设计

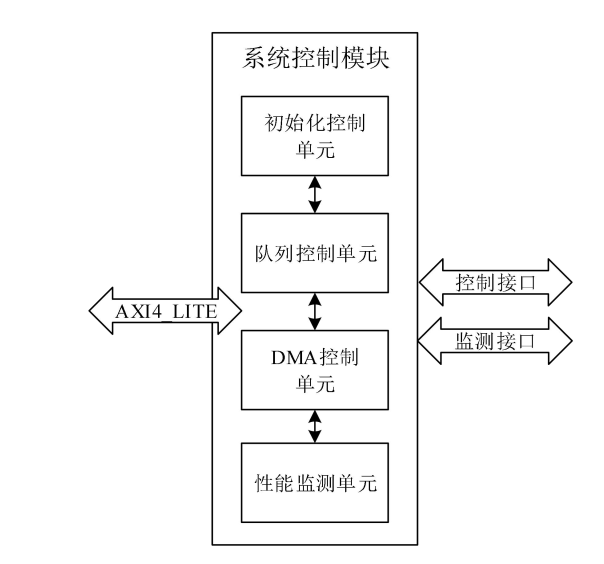

NVMe IP高速传输却不依赖XDMA设计之四:系统控制模块

NVMe IP高速传输却不依赖XDMA设计之三:系统架构

NVMe IP高速传输却不依赖便利的XDMA设计之三:系统架构

NVMe IP高速传输却不依赖XDMA设计之二:PCIe读写逻辑

NVMe IP高速传输却不依赖XDMA设计之十:队列管理模块下

NVMe IP高速传输却不依赖XDMA设计之十:队列管理模块下

评论