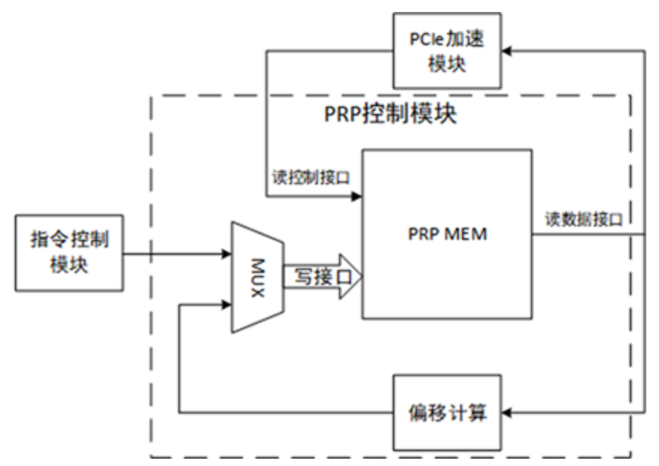

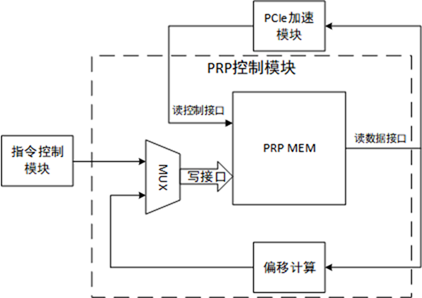

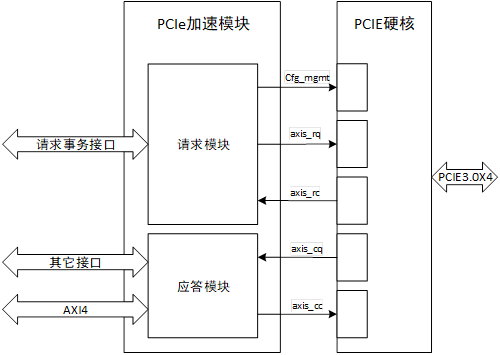

PRP控制模块负责实现指令相关的PRP列表的生成、存储与管理。NVMe的提交命令中,存在PRP1和PRP2两个字段,PPR2作为地址指针还是PRP列表指针是根据命令请求数据传输长度和PRP1的偏移量来确定的。当PRP2作为PRP列表指针时,PRP2指向PRP列表的首地址。在传统的NVMe系统中,PRP列表存放的位置一般与数据存放位置接近,因此在处理指令过程中,读取PRP经历的延时与读取数据的延时相近,为了降低读取PRP的延时,使用PRP控制模块将PRP的存储位置转移到NoP逻辑加速引擎内部。PRP控制模块的结构和连接关系如图1所示。

图1 PRP控制模块结构和连接关系图

当用户想要进行大块数据传输时,需要使用PRP提供数据的分布地址,为了降低PRP寻址的延时和复杂度,使用PRP控制模块替代原本的PRP机制。需要传输大块零散分布数据时,可以减小DMA请求长度,不使用PRP链表,将PRP链表条目字节转换为DMA请求地址。需要传输大块连续数据时,只需要PRP链表将由PRP控制模块根据请求地址自动生成。指令控制模块接收到相关指令时,根据PRP1和传输长度判断PRP2类型,如果PRP2类型为PRP链表指针,则以指令ID为地址,将PRP1的4KB偏移写入PRP MEM,PRP2则包含指令ID并指向PRP控制模块。当PCIe加速模块收到指向PRP控制模块的读数据请求时,判断为读PRP请求,PRP控制模块根据读地址取出对应的存储条目返回,然后将该数据进行偏移4KB地址计算后重新写入PRP MEM。PRP MEM的大小与指令ID池的深度一致,每个指令ID指向一个64比特的PRP MEM存储条目。

审核编辑 黄宇

-

PCIe

+关注

关注

16文章

1423浏览量

87568 -

nvme

+关注

关注

0文章

287浏览量

23721

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计44:工程设计考量?

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

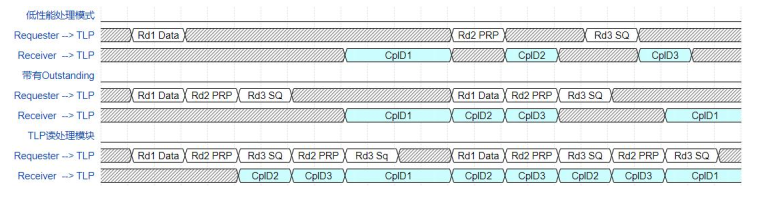

NVMe高速传输之摆脱XDMA设计16:TLP优化

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

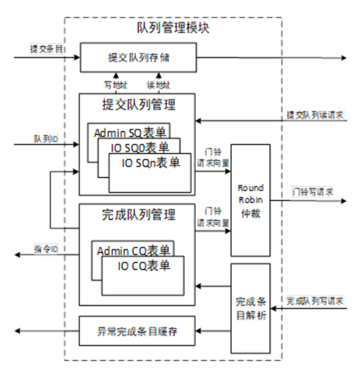

NVMe IP高速传输却不依赖XDMA设计之九:队列管理模块(上)

NVMe高速传输之摆脱XDMA设计九:队列管理模块设计(上)

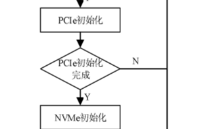

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化

NVMe高速传输之摆脱XDMA设计之11:PRP控制模块设计

NVMe高速传输之摆脱XDMA设计之11:PRP控制模块设计

评论