(3) 边界测试结果

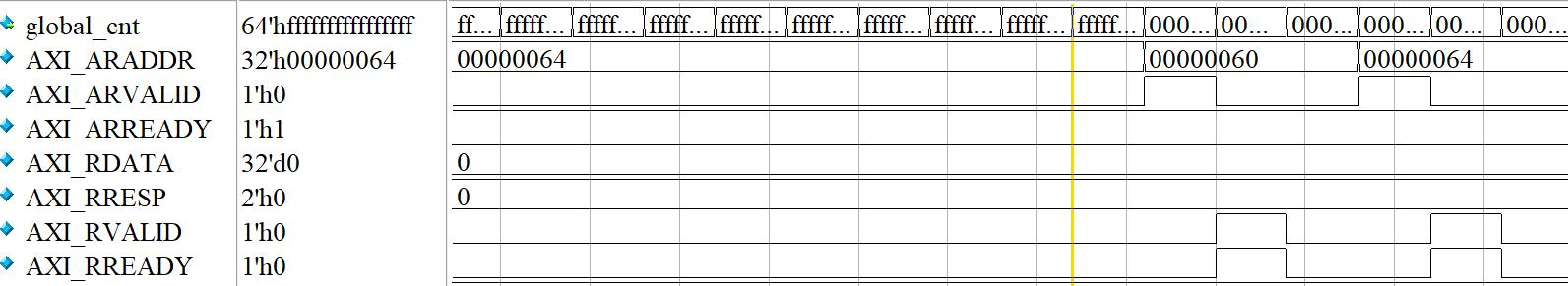

测试步骤 4 对应波形如图 1所示, 寄存器最大值为 64’hFFFFFFFFFFFFFFFF,到达最大值后一个时钟周期后翻转回 0, 在随机时刻使用 force 将寄存器赋值临近最大值, 当寄存器达到最大值后, 翻转回到 0, 读取数值为 0, 仿真行为符合设计预期。

图1 寄存器边界测试仿真波形图

(4) 功能测试结果

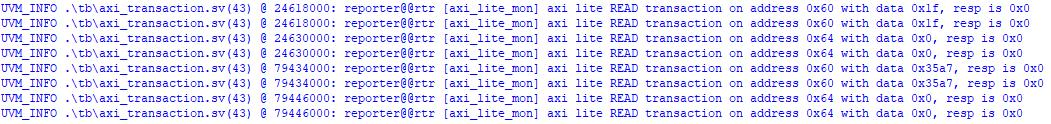

测试步骤 5 对应打印信息如图 2 所示, 由于此步骤波形跨度较大因此使用打

印信息展示。 在 24618ns 时刻读取寄存器值为 64’h1F, 在 79434ns 时刻读取寄存器值

为 64’h35A7, 计算时间差值除以 4 等于寄存器两次读取差值, 仿真行为符合设计预

期, 测试通过。

图2 寄存器功能测试打印信息图

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

原文链接:https://blog.csdn.net/tiantianuser/article/details/151548984

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5621浏览量

130471 -

nvme

+关注

关注

0文章

301浏览量

23925

发布评论请先 登录

相关推荐

热点推荐

NVMe高速传输之摆脱XDMA设计50:主要功能测试结果与分析2 nvmePCIe高速存储

如图 1 所示。配置初始化控制寄存器值为 2,启动 NVMe 初始化过程, 初始化状态机的值跳变为 3, 表示处于 NVMe 初始化状态。

图1

发表于 12-01 09:32

NVMe高速传输之摆脱XDMA设计42:DMA 读写功能验证与分析

读

写功能的测试点与测试步骤如表 1 所示。

表 1 DMA 读写功能验证步骤

1) DMA 读功能

测试步骤 1 关键信号波形如图1 所示, 首先配置 DMA

发表于 10-27 09:10

NVMe高速传输之摆脱XDMA设计37:队列管理功能验证与分析1

。 测试点与对应测试步骤如表 1所示。

表 1 队列管理功能验证步骤

(1) 创建队列功能测试结果

测试步骤 1、 2 关键信号波形如图1 所示。 在配置队列控制

发表于 10-13 11:17

NVMe高速传输之摆脱XDMA设计35:初始化功能验证与分析3

。 配置桥设备下游的 NVMe 设备模型波形如图 1 所示。 待测设计首先获取设备与供应商 ID, 然后获取配置空间类型为 TYPE0, 再向 BAR0~5 寄存器分配地址, 由于只启用了 64KB

发表于 10-10 18:21

NVMe高速传输之摆脱XDMA设计34:初始化功能验证与分析2

模型, 配置过程波形如图2所示, 图中bus_no表示当前配置总线号, dev_no表示设备号, reg_no表示寄存器号, 也对应双字对齐的寄存器地址。 待测设计首先读取了配置空间 00h

发表于 10-09 11:31

NVMe高速传输之摆脱XDMA设计33:初始化功能验证与分析

3, 表示 PCIe 初始化正常完成, 此时配置 init_ctrl 寄存器值为 2 启动 NVMe 初始化,初始化状态机跳转到 NVMe 初始化状态, 初始化状态

发表于 10-08 08:02

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

临近最大值, 当寄存器达到最大值后, 翻转回到 0, 读取数值为 0, 仿真行为符合设计预期.图1 寄存器边界测试仿真波形图

(4) 功能测试结果测试步骤 5 对应打印信息如图 2 所

发表于 10-02 11:47

NVMe高速传输之摆脱XDMA设计31: 寄存器功能验证与分析1

寄存器的初始值、 读写操作测试、 边界值测试、 功能测试等。(1) 初始值测试结果全局计数器寄存器(global_cnt) 测试步骤 1、 2

发表于 09-30 10:01

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

设备则需要开启至少 8KB 的 BAR0 空间, BAR0 地址空间中存放 NVMe 设备寄存器组, 其中包含了初始化过程中需要使用的控制器功能寄

发表于 09-29 09:31

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

, 将监测到的 PCIe TLP 事务发送到计分板。

NoPHAE_ref_model 是模拟 DUT 设计功能的参考模型, 该模型从 axi4_lite_agent的监测器获取寄存器配置信息, 根据

发表于 08-29 14:33

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

抽象为 PCIeTLP 事务,因此为了方便的在事务层构建复杂的测试用例,项目基于 UVM 搭建验证平台进行功能验证。图1 验证平台架构图在验证

发表于 08-26 09:49

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

抽象为 PCIeTLP 事务,因此为了方便的在事务层构建复杂的测试用例,项目基于 UVM 搭建验证平台进行功能验证。图1 验证平台架构图在验证

发表于 07-31 16:39

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化

采用XDMA是许多人常用xilinx库实现NVMe或其他传输的方法。但是,XDMA介绍较少,在高速存储设计时,尤其是PCIe4.0模式下,较

NVMe高速传输之摆脱XDMA设计之十:NVMe初始化状态机设计

DISABLE_CC状态。

RD_CAP:读控制器功能寄存器状态。该状态下读取NVMe设备的控制器功能

发表于 07-05 22:03

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

评论